关于Verilog 中的for语句的探讨

在C语言中,经常用到for循环语句,但在硬件描述语言中for语句的使用较C语言等软件描述语言有较大的区别。

在Verilog中除了在Testbench(仿真测试激励)中使用for循环语句外,在Testbench中for语句在生成激励信号等方面使用较普遍,但在RTL级编码中却很少使用for循环语句。主要原因就是for循环会被综合器展开为所有变量情况的执行语句,每个变量独立占用寄存器资源,每条执行语句并不能有效地复用硬件逻辑资源,造成巨大的资源浪费。简单的说就是:for语句循环几次,就是将相同的电路复制几次,因此循环次数越多,占用面积越大,综合就越慢。

在RTL硬件描述中,遇到类似的算法,推荐的方法是先搞清楚设计的时序要求,做一个reg型计数器。在每个时钟沿累加,并在每个时钟沿判断计数器情况,做相应的处理,能复用的处理模块尽量复用,即使所有的操作不能复用,也采用case语句展开处理。

对于下面的for循环语句:

for(i=;i<;i++)

DoSomething();

可以采用如下代码实现:

reg [:] counter;

always @(posedge clk)

if(syn_rst)

counter<='b0;

else

counter<=counter+;

always @(posedge clk)

begin

case(counter)

'b0000:

'b0001:

......

default:

endcase

end

另外,有几个语法的细节需要注意一下。for(i=0;i<16;i=i+1)中的i既可以是reg型的变量也可以是integer类型的变量,但是当i是reg型的变量时,需要注意因为判断语句i<16的缘故,i应定义为reg[4:0] i而不是reg[3:0] i 。由于verilog中没有自增运算符,文中提到的for语句不能写成for(i=0;i<16; i++)的形式。 下面简单的列举几个用for实现的程序代码:

示例一:

仿真结果如下:

//Leftshift for 4 bits

module For_Leftshift(

input wire [:]inp,

input wire L_EN,

output reg [:]result

); integer i;

always@(inp or L_EN)

begin

result[:] = ;

result[:] = inp;

if(L_EN == )

begin

for(i=;i<=;i=i+)

begin

result[i] = result[i-];

end

result[:] = ;

end

end endmodule

综合结果(RTL视图,实际是一个4位选择器)

示例三:for不仅可以用在组合逻辑中,而且还可以用在时序逻辑中,用于在1个周期类完成整个for循环。

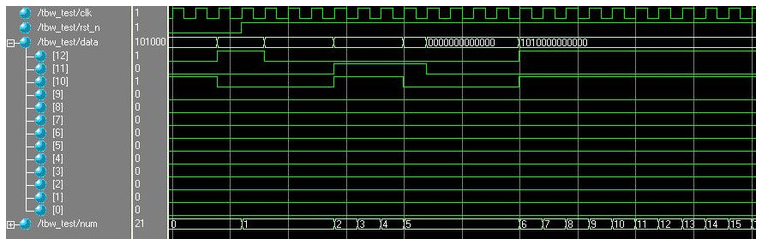

module For_Counter(

input wire clk,

input wire rst_n,

input wire [:] data,

output wire [:] numout

);

integer i;

reg[:] num; always @(posedge clk)

begin

if(!rst_n)

num = ;

else

begin

for(i=;i<;i=i+)

if(data[i]) num = num + ;

end

end assign numout = num; endmodule

综合结果(RTL视图,加法器+触发器)

关于Verilog 中的for语句的探讨的更多相关文章

- 一段比较有意思的代码——介绍system verilog中的新增幅值语句

system verilog中新加了很多幅值语句,虽然都只适用于阻塞幅值,但是在某些场合中非常实用. 下面是一段有意思的代码,覆盖了一些用法. package definitions; typedef ...

- 关于verilog中if与case语句不完整产生锁存器的问题 分类: FPGA 2014-11-08 17:39 260人阅读 评论(0) 收藏

在很多地方都能看到,verilog中if与case语句必须完整,即if要加上else,case后要加上default语句,以防止锁存器的发生,接下来就来说说其中原因. 一,什么是锁存器?锁存器与触发器 ...

- 总结Verilog中always语句的使用

always语句包括的所有行为语句构成了一个always语句块.该always语句块从仿真0时刻开始执行其中的行为语句:最后一条执行完成后,再开始执行其中的第一条语句,如此往复循环,直到整个仿真结束. ...

- verilog中初值定义

在利用verilog进行开发时,往往需要对某些寄存器进行赋初值,下面根据笔者在设计中遇到的情况进行分析. 例如下面是实现流水灯(4个led),代码如下: module ledrun ( input ...

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- Verilog中的$display和$write任务

$display(p1,p2, …,pn); $write(p1,p2, …,pn); 这两个函数和系统任务的作用都是用来输出信息,即将参数p2到pn按参数p1给定的格式输出.参数p1通常称为:“格式 ...

- Verilog中的阻塞与非阻塞

这篇文档值得阅读 按说阻塞与非阻塞是Verilog中最基本的东西,也是老生常谈.但是最近看到很多程序里用到阻塞语句竟然不是很明白,说到底是从来没有自己仔细分析过.当然一般情况程序中也是推荐用非阻塞的. ...

- 关于Verilog中的几种赋值语句

1. 连续赋值语句(Continuous Assignments) 连续赋值语句是Verilog数据流建模的基本语句,用于对线网进行赋值,等价于门级描述,是从更高的抽象角度来对电路进行描述.连续赋值语 ...

随机推荐

- [置顶] Android布局管理器 - 详细解析布局实现

布局管理器都是以ViewGroup为基类派生出来的; 使用布局管理器可以适配不同手机屏幕的分辨率,尺寸大小; 布局管理器之间的继承关系 : 在上面的UML图中可以看出, 绝对布局 帧布局 网格布局 相 ...

- Java HexString

byte[]和十六进制字符串相互转换 Java中byte用二进制表示占用8位,而我们知道16进制的每个字符需要用4位二进制位来表示. 所以我们就可以把每个byte转换成两个相应的16进制字符,即把by ...

- Nubia Z5S(高通公司MSM8974) QHSUSB_BULK砖的方法节省模式(随着win7在恢复recovery分区案例)

Nubia Z5S在某些异常情况或按组合键进入QHSUSB_BULK状态, 这种模式的现象, 猜想windows(实例win7)即使在数据线, 它会出现在计算机n载,甚至会提示要格式化某些分区(这里要 ...

- 轻量级的原型设计工具-Axure RP

1. 软件下载地址: http://www.downxia.com/downinfo/25742.html 这个版本不需要注册码,不需要安装,存绿色版. 2. 基本介绍教程: http://wenku ...

- [Android 中级]Voip之CSipSimple类库的编绎

CSipSimple是什么?是一款基于pjsip的Android客户端,相信想要研究VOIP通讯的朋友一定不会陌生,这里我就把如何编译CSipSimple写下来. 首先从CSipSimple官方网站上 ...

- IOS--实现滤镜效果的四种方式

IOS–实现滤镜效果 demo地址: https://github.com/AbeDay/ios–.git 使用CIFilter来完成IOS中滤镜效果 在IOS中可以使用系统自带的方法来达到路径效果: ...

- ASP.NET Core和ASP.NET Framework共享Identity身份验证

.NET Core 已经热了好一阵子,1.1版本发布后其可用性也越来越高,开源.组件化.跨平台.性能优秀.社区活跃等等标签再加上"微软爸爸"主推和大力支持,尽管现阶段对比.net ...

- 『零行代码』解决键盘遮挡问题(iOS)

关注仓库,及时获得更新:iOS-Source-Code-Analyze https://github.com/draveness/iOS-Source-Code-Analyze Follow: Dra ...

- Usaco 2010 Dec Gold Exercise(奶牛健美操)

/*codevs 3279 二分+dfs贪心检验 堆版本 re一个 爆栈了*/ #include<cstdio> #include<queue> #include<cst ...

- 【读书笔记】管道和FIFO

管道 提供一个单路(单向)数据流,可以为两个不同进程提供进程间的通信手段 #include <unistd.h> ]); 返回两个文件描述符,fd[0](读) 和 fd[1](写) 管道间 ...