ARM MMU架构 -- CPU如何访问MMU及DRAM

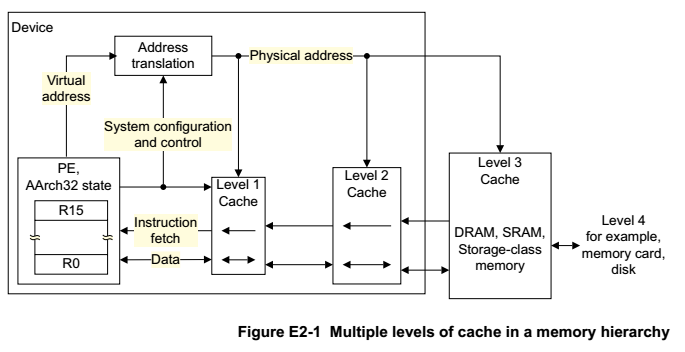

《ARM Architecture Reference Manual ARMv8-A》里面有Memory层级框架图,从中可以看出L1、L2、DRAM、Disk、MMU之间的关系,以及他们在整个存储系统中扮演的角色。

涉及到的相关文档有:

- 《ARM Architecture Reference Manual ARMv8-A》:E2 The AArch32 Application Level Memory Model和G3 The AArch32 System Level Memory Model两个章节,从总体架构上介绍了ARMv8-A Memory系统。

- 《Cortex-A53 TRM》:6 Level 1 Memory System、5 Memory Management Unit、7 Level 2 Memory System三个章节介绍了MMU/L1/L2三个模块在A53上的实现。

具体到MMU:

- 《MMU-500 TRM》:MMU-500技术参考手册。

- 《ARM SMMUv2》:System MMU 架构规格 version 2.0。

具体到L2:

- 《L2C-310 TRM》:L2控制器技术参考手册。

在Linux内核中查看L1/L2/L3缓存:

1 lscpu

2 ...

3 L1d cache: 32K

4 L1i cache: 32K

5 L2 cache: 256K

6 L3 cache: 6144K

7 ...

或者读取节点:

1 cat /sys/devices/system/cpu/cpu0/cache/indexx/size

2 cat /sys/devices/system/cpu/cpu0/cache/indexx/level

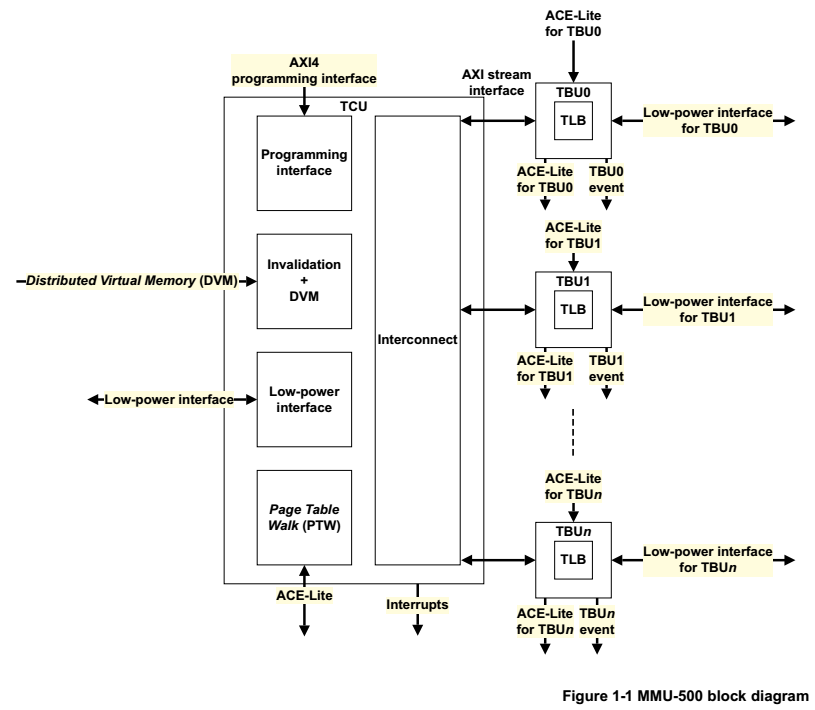

MMU-500组成

- VA:Virtual Address

- PA:Physical Address

- IPA:Intermediate Physical Address

MMU-500是系统级的存储管理单元,它基于自身寄存器和转换表中的地址映射和存储器属性,将虚拟地址转换成物理地址。

将这个转换过程分为两个阶段:

- Stage 1 - 将输入的VA转换成PA或者IPA输出。

- Stage 2 - 将IPA转换成PA。

- 或者结合Stage 1和Stage 2将输入的VA->IPA->PA。

MMU-500可以将 转换表查找结果缓存到TLB中。

MMU-500包含一下主要部件:

- TBU(Translation Buffer Unit) - 包含缓存页表的TLB,MMU-500给每个Master配置了一个TBU,专属于Master。

- TCU(Translation Control Unit) - 控制和管理地址转换,一个MMU-500仅包含一个TCU。

- Interconnect - 多TBU到TCU之间的连接。

Master可能包括GPU、Video engines、DMA Controller、LCD Controller、Network Controller等。

参考

关于CPU Cache -- 程序猿需要知道的那些事 • cenalulu's Tech Blog

阅读ARM Memory(L1/L2/MMU)笔记_weixin_34174132的博客-CSDN博客

关于TCM

TCM(Tighyly Coupled Memory,紧耦合内存)是一个固定大小的RAM,紧密地耦合至处理器内核,提供与cache相当的性能。

相比于cache的有点是,程序代码可以精确地控制什么函数或什么代码放在哪儿。当然TCM永远不会被踢出主存储器,他会有一个用户预设性能,而不是cache那样是统计特性的提高。

TCM对于以下几种情况的代码是非常有用、也是需要的:可预见的实时处理(中断处理)、时间可预见(加密算法)、避免cache分析(加密算法)、或者只是要求高性能的代码(编解码功能)。

随着cache大小的增加以及总线性能的规模,TCM将会变得越来越不重要,但是他提供了一个让你权衡的机会。

如何使用TCM?

在支持TCM的处理上,包含头文件#include <asm/tcm.h>。

使用__tcmdata、__tcmconst、__tcmfunc、__tcmlocalfunc修饰符,将变量、函数放到特定的tcm段中。

还可以使用tcm_alloc/tcm_free申请释放内存。

《对ARM紧致内存TCM的理解》- 关于TCM的介绍,以及和Cache相比的优劣。

《内核中tcm(arm)与sram代码》- 如何使用TCM。

ARM MMU架构 -- CPU如何访问MMU及DRAM的更多相关文章

- ARM v7-A 系列CPU的MMU隐射分析

ARM v7-A 系列CPU的MMU隐射分析 摘要:ARM v7-A系列的CPU加入了很多扩展,如多核处理器扩展.大物理地址扩展.TrustZone扩展.虚拟化扩展.若支持大的物理地址,则必须支持多核 ...

- ARM v8-A 系列CPU的MMU隐射分析

ARM v8-A 系列CPU的MMU隐射分析 摘要:V8-A系列CPU有ELX,X为0~3等4个异常级别,又有AArch64和AArch32两种执行状态,异常级别可以决定执行状态,而对应着执行状态,M ...

- ARM“庖丁解牛”之存储器管理单元MMU

转:http://blog.sina.com.cn/s/blog_a07635070101bcbt.html 最近笔者详细地学习了由杜春雷老师编写的<ARM体系结构与编程>.对ARM存储管 ...

- SoC嵌入式软件架构设计II:没有MMU的CPU虚拟内存管理的设计和实现方法

大多数的程序代码是必要的时,它可以被加载到内存中运行.手术后,可直接丢弃或覆盖其它代码. 我们PC然在同一时间大量的应用,地址空间差点儿能够整个线性地址空间(除了部分留给操作系统或者预留它用).能够觉 ...

- SoC嵌入式软件架构设计II:否MMU的CPU虚拟内存管理的设计与实现方法

大多数的程序代码是必要的时,它可以被加载到内存中运行.手术后,可直接丢弃或覆盖其他代码.我们PC然在同一时间大量的应用,能够整个线性地址空间(除了部分留给操作系统或者预留它用),能够觉得每一个应用程序 ...

- ARM与X86 CPU架构对比区别

CISC(复杂指令集计算机)和RISC(精简指令集计算机)是当前CPU的两种架构.它们的区别在于不同的CPU设计理念和方法.早期的CPU全部是CISC架构,它的设计目的是 CISC要用最少的机器语言 ...

- ARM架构--CPU的微架构

网上确实有说ARM架构的,但是此架构泛指用ARM指令系统的CPU,而不是CPU的微架构.,硬件电路上,要用ARM指令集系统,必然硬件设计电路上要要遵循,ARM指令的特点和寻址方式,所以说高通和苹果的C ...

- ARM与x86 CPU架构对比

CISC(复杂指令集计算机)和RISC(精简指令集计算机)是当前CPU的两种架构.它们的区别在于不同的CPU设计理念和方法.早期的CPU全部是CISC架构,它的设计目的是CISC要用最少的机器语言指令 ...

- ARM与X86 CPU架构区别

CISC(复杂指令集计算机)和RISC(精简指令集计算机)是当前CPU的两种架构.它们的区别在于不同的CPU设计理念和方法.早期的CPU全部是CISC架构,它的设计目的是 CISC要用最少的机器语言指 ...

- ARM系统架构

ARM系统架构 一.ARM概要 ARM架构,曾称进阶精简指令集机器(Advanced RISC Machine)更早称作Acorn RISC Machine,是一个32位精简指令集(RISC)处理器架 ...

随机推荐

- Springboot mybatis总结

mybatis 总结 属性配置 1. mybatis.configuration.mapUnderscoreToCamelCase=true mapUnderscoreToCamelCase用于映射表 ...

- git merge和git rebase总结

dev分支 * da349ef (dev) e * 75350bc d * 63cbbb8 c * c6509a5 b * 13405af a 文件可能会发生冲突,需要解决一下 aaaaaaaaa b ...

- FileInputStream字节输入流

FileInputStream字节输入流 编码思想:首相顶一个FileInputStream字节输入流对象,fis设置为nul,在try/catch里面放入FileInputStream字节输入流对象 ...

- docker学习笔记一-docker安装与卸载

环境查看 # 1 查询当前centOS的版本,官方要求版本为7以上 uname -r 查询系统内核 cat /etc/os-release 系统版本 安装 # 1.卸载旧版本 yum remove d ...

- python 模块、原始字符串

模块 三种方法: import from 模块 import 成员,成员 from 模块 import * *代表所有的成员 隐藏成员: 模块中以下划线_开头的属性 隐藏成员不会被from 模块 im ...

- null和undefined的区别、数组和伪数组的区别

null和undefined的区别 undefined: 字面意思是未定义的值,语义是希望表示一个变量最原始的状态,而非人为操作的结果.这种原始状态会在以下四个场景中出现: 声明了一个变量但没有赋值 ...

- 【Java面试】面试遇到宽泛的问题,这么回答就稳了,谈谈你对Redis的理解

"谈谈你对Redis的理解"! 面试的时候遇到这类比较宽泛的问题,是不是很抓狂? 是不是不知道从何开始说起? 没关系,今天我用3分钟教你怎么回答. 大家好,我是Mic,一个工作了1 ...

- ProxySQL(1):简介和安装

文章转载自:https://www.cnblogs.com/f-ck-need-u/p/9278818.html ProxySQL有两个版本:官方版和percona版,percona版是在官方版的基础 ...

- 洛谷P2866 [USACO06NOV]Bad Hair Day S (单调栈)

看到这道题很容易想到单调栈,但我一开始想的是从后往前扫,但发现会有问题(因为这样会对后面牛的答案造成影响),所以这时我们要及时换一个思路,从前往后扫. 维护一个单调递减的栈,插入h[i]时,小等于它的 ...

- AgileBoot - 基于SpringBoot + Vue3的前后端快速开发脚手架

AgileBoot 仓库 后端地址:https://github.com/valarchie/AgileBoot-Back-End 技术栈:Springboot / Spring Security / ...