No.4 Verilog 表达式

4-1 操作数

常数、参数、线网、变量、位选、存储器、数组。

*部分位选:

integer mark;

reg [:] inst;

wire [:] gpio;

inst[mark+ : ] //选择 mark,mark+1 位

gpio[mark- : ] //选择 mark,mark-1 位

inst[+:] <==> inst[:]

gpio[+:] <==> gpio[:]

inst[-:] <==> inst[:]

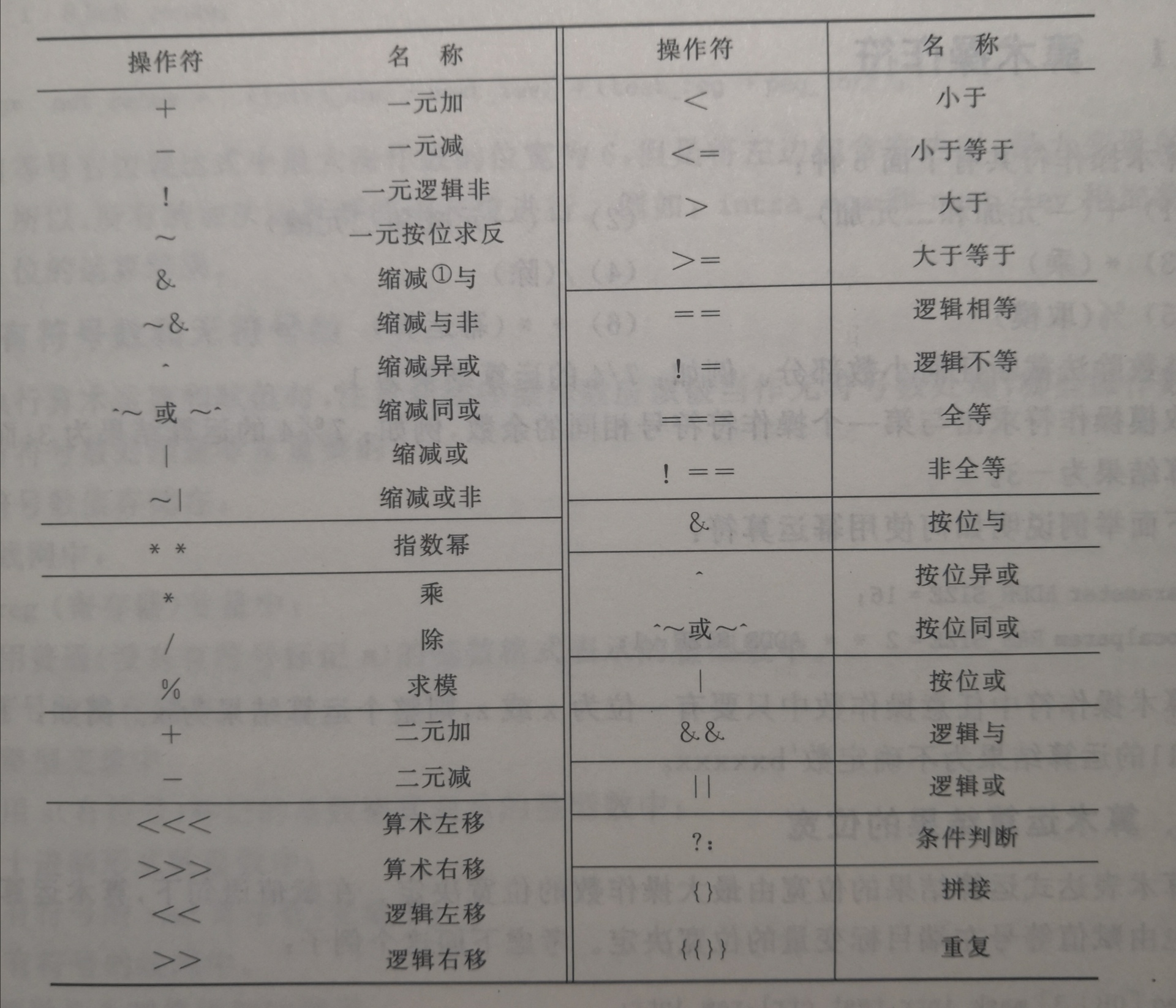

4-2 操作符

特殊:===、!==、{}、{{}}、~&、^~、<<<、>>>、**、?:。

例:

()sw = 'b11x0; xn = 'b11x0;

则 sw == xn 的结果为x,sw === xn 的结果为1。

()qreg = 'h17; //00010111

qreg >> //结果为8'b00000101,即05H

qreg >>> //结果为8'b00000101

()wire [:]zx; wire [:]cv;

assign zx[:] = {zx[],zx[],zx[],zx[]};

assign cv[:] = {zx[:],zx[:]}; {{'b0}} // 等效于 0000

{{abcd}} // 等效于 {abcd,abcd,abcd,abcd}

No.4 Verilog 表达式的更多相关文章

- verilog运算符及表达式

1.运输符 算术运算符(+,-,X,/,%) 赋值运算符(=,<=) 关系运算符(>,<,>=,<=) 逻辑运算符(&&,||,!)//与或非 条件运算符 ...

- Verilog学习笔记基本语法篇(十一)········ 常用系统函数

1)系统任务:$monitor 格式: $monitor(p1,p2,p3...pn); $monitor; $monitoron; $monitoroff; 任务$monitor提供了监控输出列 ...

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- system verilog的一些总结(从其他博客复制来的)

转载自 http://blog.sina.com.cn/s/blog_e7fec2630101f5t9.html SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 136 ...

- VHDL:信号、端口以及和Verilog的区别

1.信号 信号是描述硬件系统的基本数据对象,它的性质类似于连接线.信号可以作为设计实 体中并行语句模块间的信息交流通道. 信号作为一种数值容器,不但可以容纳当前值,也可以保持历史值(这决定于 ...

- 关于初次使用Verilog HDL语言需要懂的基本语法

关于初次使用Verilog HDL语言需要懂的基本语法 1.常量 数字表达式全面的描述方式为:<位宽><进制><数字> 8’b10101100,表示位宽为8的二进制 ...

- (原创)defparam的应用(Verilog,CPLD/FPGA)

1.Abstract 在同一个模块被多次例化的时候,改变参数构建不同的硬件实体是一个很好的选择.特别是今天帮一个朋友调试一个比较复杂的逻辑,深有体会.这个也是一个小技巧,回来也查了许多资料,强 ...

- Verilog学习笔记设计和验证篇(三)...............同步有限状态机的指导原则

因为大多数的FPGA内部的触发器数目相当多,又加上独热码状态机(one hot code machine)的译码逻辑最为简单,所以在FPGA实现状态机时,往往采用独热码状态机(即每个状态只有一个寄存器 ...

随机推荐

- tyvj 1266 费解的开关

传送门 解题思路 枚举第一行的状态,判断后面可不可行. 代码 #include<iostream> #include<cstdio> #include<cstring&g ...

- jquery判断元素是否出现在可视区

在我们的日常开发中,经常会遇到当元素出现在可视区的时候需要去出发某一事件的情况.我最近在优化环球网首页的时候,将非可视区的代码全部放入到webComponent中.打算当这个元素出现在可视区的时候 ...

- hdu4565

#include<iostream> #include<cstdio> #include<queue> #include<algorithm> #inc ...

- agc014F Strange Sorting

这套题比较简单,以为自己能够独立A掉D和E,或许就能自己A掉F,看来还真是想多了 题意:给一个$n$的全排列,每次操作把$max(a[1],a[2],...,a[i]) = a[i]$的记为$high ...

- 20190722-Moni和Boly的故事

Moni(模拟)可以得到60分 Boly(暴力)可以得到40分 还好说,这次有点可行. 过程是: 先看了T3,可以模拟,然后做T1T2 T1 好说,$exgcd$,不会. 暴力,暴力!骗了40. T2 ...

- Linux下安装docker,更改镜像仓库地址,并部署springboot应用

今天做不成的事,明天也不会做好. 各位同学大家好,随着docker的快速发展,越来越多的人开始使用,一方面随着容器化这个趋势越来越火,docker成为了其中的佼佼者:二来容器化确实降低了运维的门槛,让 ...

- 学习线程池源码--ScheduledThreadPoolExecutor

1. 创建ScheduledThreadPoolExecutor ScheduledThreadPoolExecutor继承自ThreadPoolExecutor,实现了Schedule ...

- day36 11-Hibernate中的事务:当前线程中的session

如果你没有同一个session开启事务的话,那它两是一个独立的事务.必须是同一个session才有效.它给我们提供一个本地线程的session.这个session就保证了你是同一个session.其实 ...

- Leetcode79. Word Search单词搜索

给定一个二维网格和一个单词,找出该单词是否存在于网格中. 单词必须按照字母顺序,通过相邻的单元格内的字母构成,其中"相邻"单元格是那些水平相邻或垂直相邻的单元格.同一个单元格内的字 ...

- Leetcode64.Minimum Path Sum最小路径和

给定一个包含非负整数的 m x n 网格,请找出一条从左上角到右下角的路径,使得路径上的数字总和为最小. 说明:每次只能向下或者向右移动一步. 示例: 输入: [ [1,3,1], [1,5,1] ...