关于信号的延迟---verilog

关于信号的延迟---verilog

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/02/08 11:39:20

// Design Name:

// Module Name: signal_detect

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module signal_detect( input wire clk,

input wire rst,

input wire signal_en

//input wire signal

//output wire signal_existence

); reg signal;

always @(posedge clk or posedge rst)

begin

if(rst)

signal <= 'b0;

else if(signal_en)

signal <= 'b1;

else

signal <= 'b0;

end reg signal_delay;

wire signal_rise;

always @(posedge clk or posedge rst)

begin

if(rst)

signal_delay <= 'b0;

else

signal_delay <= signal;

end assign signal_rise = !signal_delay && signal; endmodule /* add_force {/signal_detect/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/signal_detect/rst} -radix hex {1 0ns} {0 150ns}

add_force {/signal_detect/signal_en} -radix hex {0 0ns} {1 300ns} {0 400ns} */

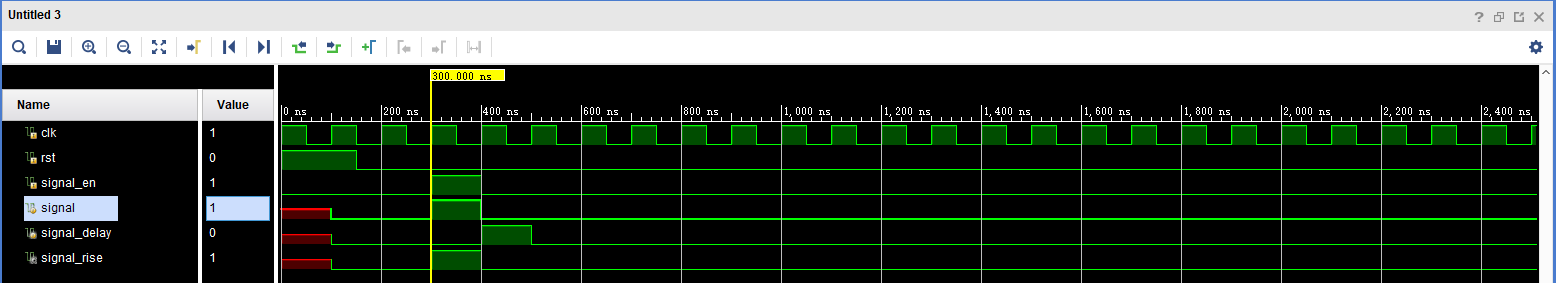

仿真波形:

容易犯下这样一种错误:

module signal_detect(

input wire clk,

input wire rst,

input wire signal

//input wire signal

//output wire signal_existence

);

reg signal_delay;

wire signal_rise;

always @(posedge clk or posedge rst)

begin

if(rst)

signal_delay <= 'b0;

else

signal_delay <= signal;

end

assign signal_rise = !signal_delay && signal;

endmodule

/*

add_force {/signal_detect/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/signal_detect/rst} -radix hex {1 0ns} {0 150ns}

add_force {/signal_detect/signal} -radix hex {0 0ns} {1 300ns} {0 400ns}

*/

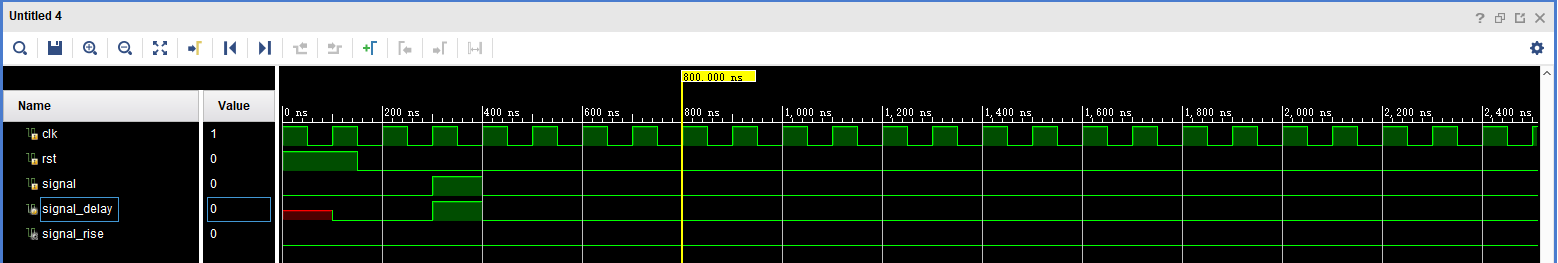

仿真波形:

像这种写法,根本就起不到边沿检测的作用,只是对外部信号进行一次采集。

关于信号的延迟---verilog的更多相关文章

- 信号滤波模块verilog代码---UNLOCK,LOCK状态机方式

信号滤波模块verilog代码 `timescale 1ns / 1ps /////////////////////////////////////////////////////////////// ...

- 【设计经验】1、Verilog中如何规范的处理inout信号

在FPGA的设计过程中,有时候会遇到双向信号(既能作为输出,也能作为输入的信号叫双向信号).比如,IIC总线中的SDA信号就是一个双向信号,QSPI Flash的四线操作的时候四根信号线均为双向信号. ...

- verilog语法实例学习(1)

本文档中通过verilog实例来学习verilog语法.Verilog是一种硬件描述语言,它具有并发性和时序性.并发性是指不同硬件模块的同时操作,时序性是指信号的赋值或操作在时钟的边沿进行.由于作者本 ...

- verilog语法学习目录

verilog语法实例学习(1) Verilog中的注释 Verilog中的信号 标识符 信号的值 Verilog中的数字 Verilog中的参数 verilog语法实例学习(2) 线网类型 变量类型 ...

- FPGA异步时钟系统中信号处理之单比特信号

有些东西当你习以为常而不去深思熟虑的时候,致命的错误就会因此埋下! FPGA开发中难免会遇到跨时钟域处理的问题,而对于单比特信号,我会不假思索的回答:打两拍不久解决了吗?但是事实时,这佯作的 ...

- 06-BCD计数器设计与应用——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:1.掌握BCD码的原理.分类以及优缺点 2.设计一个多位的8421码计数器并进行验证 3.学会基本的错误定位以及修改能力 ...

- 最快让你上手ReactiveCocoa之基础篇

前言 很多blog都说ReactiveCocoa好用,然后各种秀自己如何灵活运用ReactiveCocoa,但是感觉真正缺少的是一篇如何学习ReactiveCocoa的文章,这里介绍一下. 1.Rea ...

- ReactiveCocoa学习

ReactiveCocoa常见类 6.1RACSiganl:信号类,一般表示将来有数据传递,只要有数据改变,信号内部接收到数据,就会马上发出数据. 注意: 信号类(RACSiganl),只是表示当数据 ...

- ReactiveCocoa基础知识内容

本文记录一些关于学习ReactiveCocoa基础知识内容,对于ReactiveCocoa相关的概念如果不了解可以网上搜索:RACSignal有很多方法可以来订阅不同的事件类型,ReactiveCoc ...

随机推荐

- 2017中国大学生程序设计竞赛 - 网络选拔赛 HDU 6152 Friend-Graph(暴力搜索)

题目传送:http://acm.hdu.edu.cn/showproblem.php?pid=6152 Problem Description It is well known that small ...

- Spring Boot 揭秘与实战(五) 服务器篇 - Tomcat 启用 HTTPS

文章目录 1. 生成证书 2. 配置 HTTPS 支持 3. 启动与测试 4. 源代码 Spring Boot 内嵌的 Tomcat 服务器可以启用 HTTPS 支持. 生成证书 使用第三方 CA 证 ...

- Kaggle:Home Credit Default Risk 特征工程构建及可视化(2)

博主在之前的博客 Kaggle:Home Credit Default Risk 数据探索及可视化(1) 中介绍了 Home Credit Default Risk 竞赛中一个优秀 kernel 关于 ...

- 当BeanUtils遇到泛型

前言: BeanUtils(spring版/apache版)工具极大方便了java developer, 尤其在写业务代码中, 各种域模型DO, BO, VO等对象之间的复制. 但使用BeanUtil ...

- 创建一个版本库,把文件夹用Git管理起来

创建一个文件夹,把这个文件夹用Git管理起来,那么这个文件夹的改变都可以被Git跟踪到,当然也可以将Git中的文件还原到某一个时刻. 首先创建一个空的目录,然后将空的目录由Git来管理 1.建立一个文 ...

- C语言--第七周作业评分(5班)

作业链接:https://edu.cnblogs.com/campus/hljkj/CS2017-5/homework/1304 一.评分要求 要求1 完成PTA第七周所有题,总共两次题,每次12.5 ...

- i = i ++;的分解

步骤分解: package wrong; public class ShortTest { public static void main(String args[]) { /* * i = i ++ ...

- L3-019 代码排版 (30 分)

某编程大赛中设计有一个挑战环节,选手可以查看其他选手的代码,发现错误后,提交一组测试数据将对手挑落马下.为了减小被挑战的几率,有些选手会故意将代码写得很难看懂,比如把所有回车去掉,提交所有内容都在一行 ...

- oracle 数据库相关名词--图解

通过下图,我们可以更好的理解oracle的结构关系. 知识拓展: 知识点及常用的命令如下: 1)通常情况我们称的“数据库”,并不仅指物理的数据集合,他包含物理数据.数据库管理系统.也即物理数据.内存 ...

- cmake 创建并调用动态库和静态库

编程之路刚刚开始,错误难免,希望大家能够指出. 刚刚开始学习cmake,写这篇之前我认真的看了“小代码2016”的博客,感觉很不错,看完之后我自己练习了一遍,记录一下. 1.首先建立好合适的目录结构, ...