zedboard如何从PL端控制DDR读写(四)

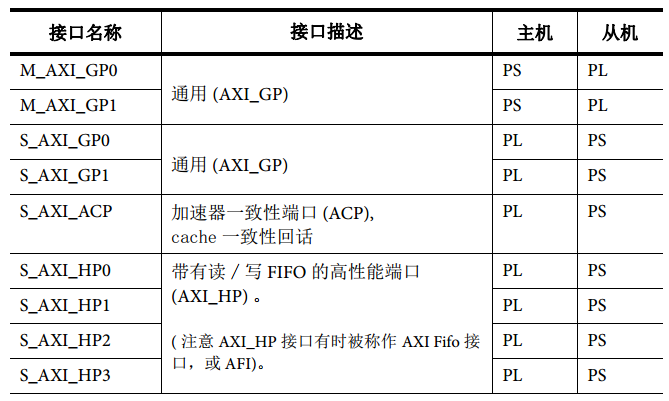

PS-PL之间的AXI 接口分为三种:

• 通用 AXI(General Purpose AXI) — 一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信。接口是透传的不带缓冲。总共有四个通用接口:两个 PS 做主机,另两个 PL 做主机。

• 加速器一致性端口(Accelerator Coherency Port) — 在 PL 和 APU 内的 SCU之间的单个异步连接,总线宽度为 64 位。这个端口用来实现 APU cache 和 PL的单元之间的一致性。PL 是做主机的。

• 高性能端口(High Performance Ports) — 四个高性能 AXI 接口,带有 FIFO缓冲来提供 “ 批量 ” 读写操作,并支持 PL 和 PS 中的存储器单元的高速率通信。数据宽度是 32 或 64 位,在所有四个接口中 PL 都是做主机的。

即:

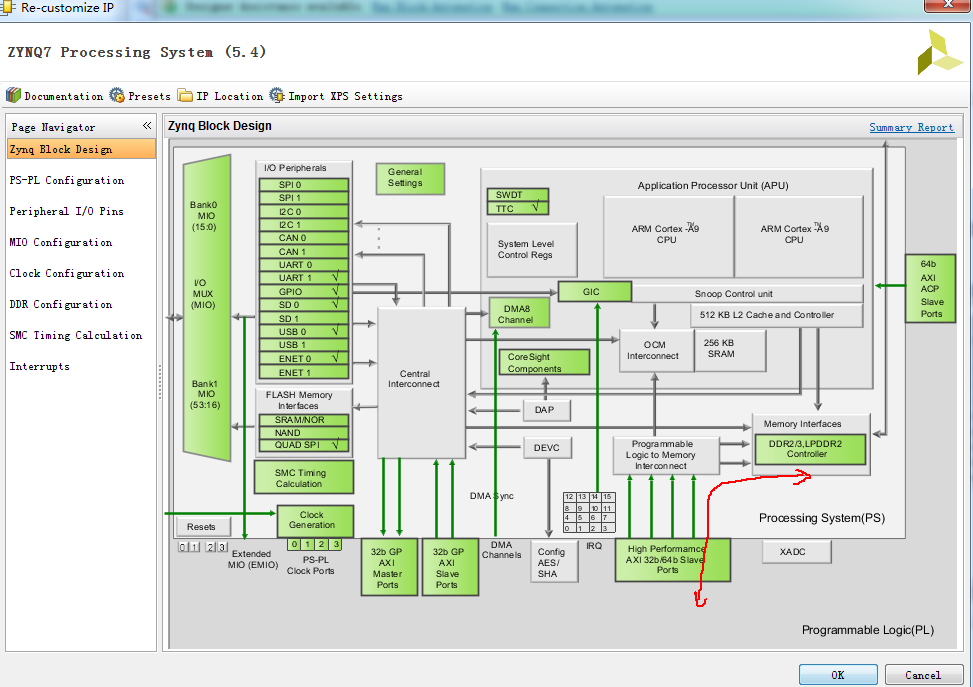

从VIVADO的配置中,我们可以看出DDR控制器是通过四个AXI HP连接到PL端的。

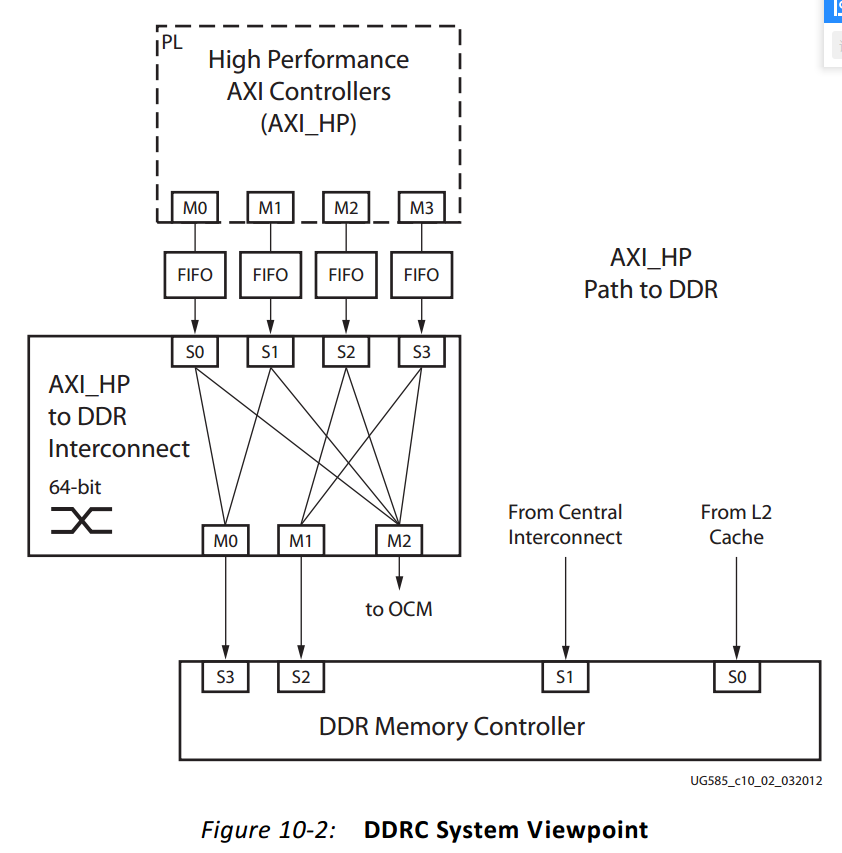

再去查阅UG585,里面有一段话是这么说的:

The four AXI_HP interfaces are multiplexed down, in pairs, and are connected to ports 2 and 3 as

shown in Figure 10-2. These ports are commonly configured for high bandwidth traffic. The path

from these four interfaces to the DDR include two ports on the DDR memory port arbiter. The

interconnect switch arbitrates back-and-forth between each of the two ports. Read and write

channels operate separately.

大致意思就是说四路HP总线通过M2连接到了片上存储器(貌似是256KB的SRAM,这个与我们现在要做的工作无关,在这里提一嘴是因为后来涉及到对DDR寻址的时候,有一部分地址是连到了这个OCM的,这一部分地址对我们暂时没用,需要避开),另外这四路总线的0和1又通过M0连到了DDR的S3端口,2和3通过M1连到了DDR的S2端口。一般推荐的方法是,同时使用HP0和HP2(或者HP1和HP3),总之就是要使用分离的通道来操作DDR,以获取较高的性能。

从上图我们也可以看到,每个 AXI_HP 接口里都有用做读写通信的 FIFO 缓冲器。在某些 Xilinx 文档中,AXI_HP接口也被叫做 AXI FIFO 接口 (AFI),来表明它们的缓冲能力。AXI_HP 接口的特性包括:

• 32 或 64 位数据主机接口,每个端口可以独立编程。

• 对于未对齐的 32 位传输,可以自动扩展传输尺寸从 32 位到 64 位。

• 写命令的可编程的阈值。

• 对于所有的 PL-PS 接口的异步时钟频率跨域。

• 读写 FIFO。

• 命令和通信数据 FIFO 填充程度计数是 PL 可见的。

zedboard如何从PL端控制DDR读写(四)的更多相关文章

- zedboard如何从PL端控制DDR读写(七)

前面已经详细介绍了从PL端如何用AXI总线去控制DDR的读写,并且从AXI_BRESP的返回值来看,我们也是成功写入了的.但是没有通过别的方式来验证写入的数据的话,总是感觉差了点什么. 今天试了一把从 ...

- zedboard如何从PL端控制DDR读写(五)

有了前面的一堆铺垫.现在终于开始正式准备读写DDR了,开发环境:VIVADO2014.2 + SDK. 一.首先要想在PL端通过AXI去控制DDR,我们必须要有一个AXI master,由于是测试,就 ...

- zedboard如何从PL端控制DDR读写(六)

上一节说到了DDR寻址的问题,如下图: 从官方文档上我们看到了DDR的地址是从0008_0000开始的,那么我们开始修改Xilinx给我们提供的IP核代码.其实很简单,上一节已经分析了地址停留在000 ...

- zedboard如何从PL端控制DDR读写(一)

看了一段时间的DDR手册,感觉大体有一点了解了,想要实际上板调试,然而实验室可用的开发板不多,拿了一块zynq板看了看,DDR确实有,但是已经集成了控制器,而且控制器还放到了PS端,PL只能通过AXI ...

- zedboard如何从PL端控制DDR读写(三)——AXI-FULL总线调试

之前的项目和培训中,都只用到了AXI-Lite或者AXI-Stream,对于AXI-FULL知之甚少,主要是每次一看到那么多接口信号就望而却步了. 现在为了调试DDR,痛下决心要把AXI-FULL弄懂 ...

- zedboard如何从PL端控制DDR读写(二)——AXI总线

虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的. AXI(Ad ...

- 第十二章 ZYNQ-MIZ702 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- 第十一章 ZYNQ-MIZ701 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- MIG IP控制DDR3读写测试

本文设计思想采用明德扬至简设计法.在高速信号处理场合下,很短时间内就要缓存大量的数据,这时片内存储资源已经远远不够了.DDR SDRAM因其极高的性价比几乎是每一款中高档FPGA开发板的首选外部存储芯 ...

随机推荐

- Genymotion--最快的安卓模拟器 测试与模拟APP应用必备

命令行工具,Eclipse插件,多操作系统 1 易于安装,易于运行 超过10个虚拟设备 您很匆忙?您想测试市场的主要设备?使用我们的虚拟设备! 2 控制功能强大的传感器来测试您的应用程序 自定义你的测 ...

- Ambari是什么?

Ambari目标 解决Hadoop生态系统部署 部署:hadoop组件间有依赖,包括配置.版本.启动顺序.权限配置等. 部署过程跟踪.能够展示出部署过程中每个步骤的状态及相关信息. 多机部署问题,当集 ...

- iOS 动画 旋转 移动简单代码

#import "ViewController.h" @interface ViewController () { UIImageView *imgView; BOOL flag; ...

- 传智播客JavaWeb day06-jstl

一.jsp标签(sun公司提供的) 二.EL表达式 三.jstl (javaserver pages standard tag library) 1.为什么要有jstl jsp标签太弱,el表达式功能 ...

- js创建对象的6种方式

一.工厂模式 function createStudent(name,age){ var o=new Object(); o.name=name; o.age=age; o.myName=functi ...

- Linux 安装 node

在 Linux 上安装 node,使用 Linux 编译后的版本最佳. 1.进入 node 官网,找到 Linux 版本下载,这里我们右键复制下载地址即可. 2.在 Linux 上,使用命令 curl ...

- lsm-tree

https://www.quora.com/How-does-the-Log-Structured-Merge-Tree-work http://blog.cloudera.com/blog/2012 ...

- 基于MVC4+EasyUI的Web开发框架形成之旅--界面控件的使用

在前面介绍了两篇关于我的基于MVC4+EasyUI技术的Web开发框架的随笔,本篇继续介绍其中界面部分的一些使用知识,包括控件的赋值.取值.清空,以及相关的使用. 我们知道,一般Web界面包括的界面控 ...

- 获取 .net framework 路径

要获取当前程序所使用的.netframework路径: System.Runtime.InteropServices.RuntimeEnvironment.GetRuntimeDirectory(); ...

- Android之旅---广播(BroadCast)

什么是广播 在Android中,Broadcast是一种广泛运用的在应用程序之间传输信息的机制.我们拿广播电台来做个比方.我们平常使用收音机收音是这样的:许许多多不同的广播电台通过特定的频率来发送他们 ...