FPGA 开发详细流程你了解吗?

FPGA 的详细开发流程就是利用 EDA 开发工具对 FPGA 芯片进行开发的过程。

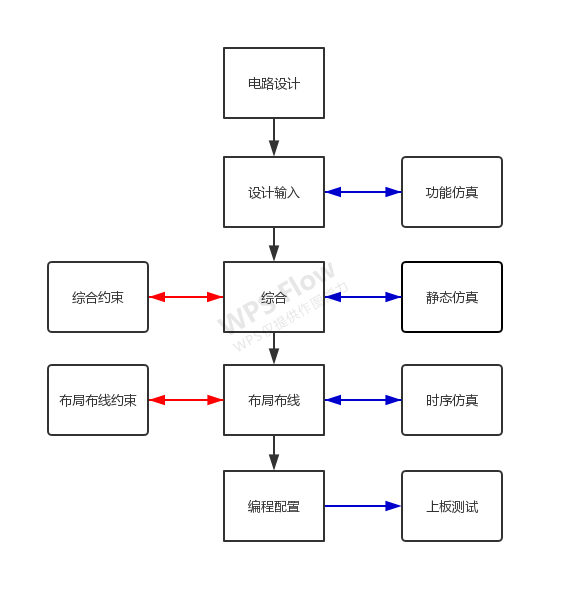

FPGA 的详细开发流程如下所示,主要包括电路设计、设计输入、综合(优化)、布局布线(实现与优化)、编程配置五大步骤,其中,还有功能仿真、静态仿真、时序仿真三大仿真,以及综合约束、布局布线约束(包括位置约束和时序约束)两大约束等等。

1、电路设计(FPGA Design)

在电路设计之前,首先要进行的是算法的设计与验证(在 Python 或 Matalb 中完成)(至于算法是怎么来的,一般是根据市场需求来开发的,这个就不在本次讨论之中了)、方案论证、架构设计和 FPGA 芯片选型等准备工作。系统工程师根据任务要求,如系统的指标和复杂度、功能性和稳定性、对工作速度(延时和工作频率)和芯片本身的各种资源、成本、功耗等等方面进行权衡,选择合理的设计方案(浮点定点、设计优化)和合适的器件类型(如一般 Artix 还是 Zynq 或者是 Zynq UltraScale + 等等)。

电路设计方法分为自底向上和自顶向下的设计方法。一般都采用自顶向下的设计方法(从系统设计开始,逐渐向模块设计、器件设计和版图设计等更物理的层次推进):从系统设计开始入手,然后把整体系统分成若干个基本单元,然后再把每个基本单元划分为下一层次的基本单元,一直这样做下去,直到可以直接使用 EDA 元件库为止。最后,才开始 Coding。

2、设计输入(Design Entry)

设计输入指的是将设计者所涉及的电路以开发软件要求的某种形式表达出来,并输入到相应的软件中的过程。最常见的设计输入的表达方式为 IP 核、原理图(Schematic)和 HDL 文本输入。

这里的 IP 按照来源的不同可以分为三类,第一种是来自前一个设计的内部创建模块(Design by Yourself),第二种是 FPGA 厂家,第三种就是来自 IP 厂商。

FPGA 厂家和 IP 厂商可以在 FPGA 开发的不同时期提供给我们不同的 IP。我们暂且知道他们分别是未加密的 RTL 级 IP、加密的 RTL 级 IP、未经布局布线的网表级 IP、布局布线后的网表级 IP。

3、综合(Synthesis)

综合一般指的是将高级抽象层次的设计描述自动转化为较低层次描述的过程。而在 FPGA 中的综合则是指自动实现如下转换的软件工具,或者说,综合器就是能够将原理图或者 HDL 文本语言、描述的电路编译成由与或阵列、RAM、触发器、寄存器等逻辑单元组成的电路结构网表的工具。

综合包括编译、映射和优化(也可以分开不被综合所包含),编译就是 HDL → 门级网表,映射就是门级网表 → LUT,优化就是优化设计( 需要说明的是在 Altera 的开发流程中,将编译、映射过程按照我们叙述的合称为综合,而在 Xilinx 的开发流程中,由设计输入得到门级网表的过程叫做综合,而映射过程归结到其叫做实现的某一子步骤中。不过这都是小问题,整体的流程还是遵循这个顺序的)。

综合的形式:

1、将算法、行为描述转换到 RTL 级(Register Transfer Level)(寄存器传输级),即从行为描述到结构描述。

2、将 RTL 级描述转换到逻辑门级(包括触发器),称为逻辑综合。

3、将逻辑门表示转换到版图表示,或者 PLD 器件的配置网表表示;根据版图信息能够进行 ASIC 生产,有了配置网表可完成基于 PLD 器件的系统实现。

软件程序编译器是将 C 或汇编语言等编写的程序编译为 0,1 代码流,而硬件综合器是将 Verilog HDL 等语言编写的程序转化为具体的电路网表结构。

在电路设计中,网表(Netlist)是用于描述电路元件相互之间连接关系的,一般来说是一个遵循某种比较简单的标记语法的文本文件。(百度百科 门级网表)。综合就是逻辑综合器根据约束条件把 Verilog HDL 或 VHDL 描述的 RTL 级设计,转换为可与 FPGA/CPLD 的门阵列基本结构相映射的网表文件。

4、布局布线(Place & Route)

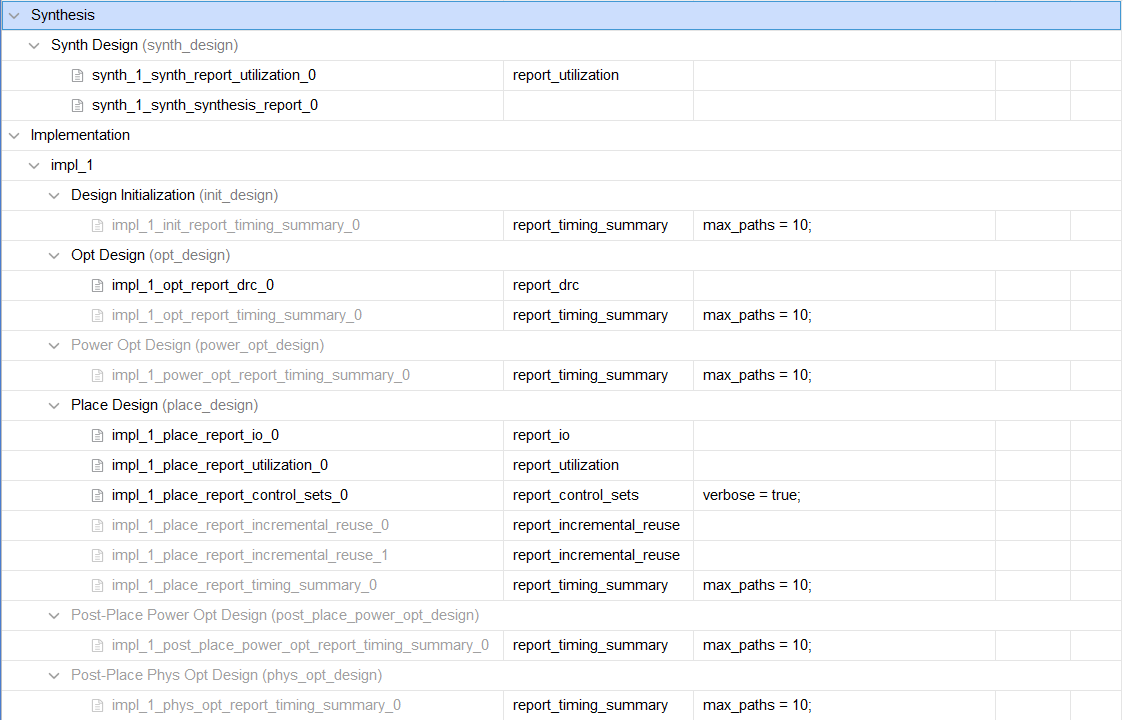

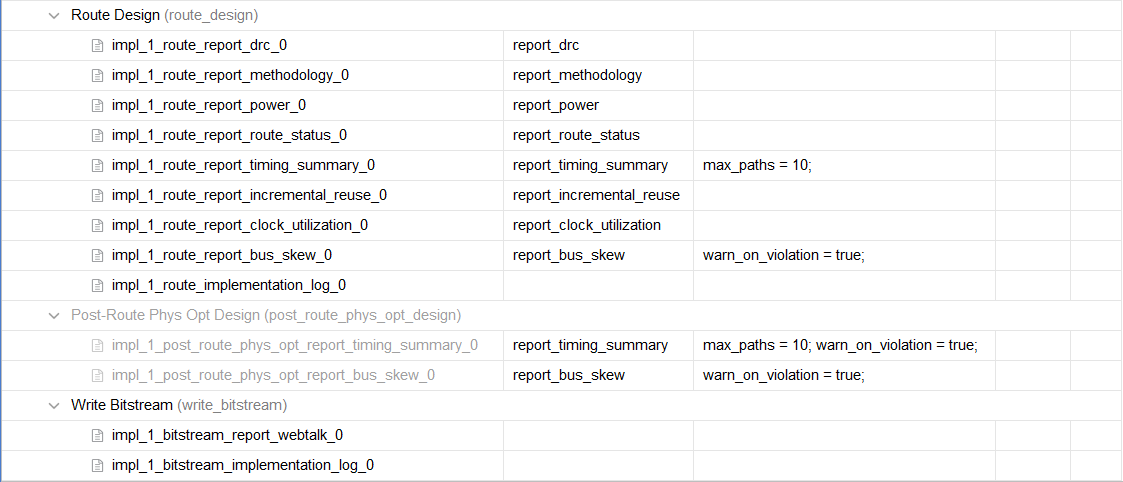

谈及布局布线之前,首先要谈到实现(Implementation)。实现就是将综合生成的逻辑网表配置到具体的 FPGA 芯片上,而布局布线就是其中最重要的过程。Vivado 中的实现具体如下所示,分为设计初始化(Design Initialization)、优化设计(Opt Design)、功耗优化设计(Power Opt Design)、布局设计(Place Design)、后布局功耗优化设计(Post-Place Power Opt Design)、后布局物理优化设计(Post-Place Phys Opt Design)、布线设计(Route Design)、后布线物理优化设计(Post-Route Phys Opt Design)、生成比特流(Write Bitstream)。

布局布线指的是将综合生成的电路逻辑网表映射到具体的目标器件中实现,并产生最终的可下载文件的过程。

布局是将已分割的逻辑小块放到器件内部逻辑资源的具体位置,并使它们易于连线;

布线则是利用器件的布线资源完成各功能模块之间和反馈信号之间的连接。

布局布线完成之后将产生如下一些重要的文件:

1、芯片资源耗用情况报告。

2、面向其他 EDA 工具的输出文件,如 EDIF 文件等。

3、产生延时网表结构,以便于进行精确的时序仿真,这时候的仿真结果能够比较精确地预测未来芯片的实际性能。如果仿真结果达不到设计要求,就需要修改源代码或者选择不同速度的器件,直至满足设计要求,例如普通加法器改为超前进位加法器,普通乘法器改为 Booth 乘法器等等,通过减少关键路径来满足时序要求。

4、器件编程文件:如用于 FPGA 配置的 SOF,JAM,BIT 等格式的文件,用于 CPLD 编程的 JEDEC,POF 等格式的文件。由于布局布线与芯片的物理结构直接相关,所以一般选择芯片制造商提供的开发工具进行此项工作。

约束(Constraint)(附加):

约束分为综合约束和布局布线约束,布局布线约束又可以分为位置约束、时序约束。约束,就是对这些操作环节定制规则,定制条件,比如引脚约束和时序约束。一般开发环境会对这些约束有个默认,这些默认的设置对大部分情况下还是适用的,但是通常布局布线约束中的 I/O 约束是我们每一个工程都必须给定的。

仿真(Simulation)(附加):

仿真指的是对所设计电路功能的验证。仿真包括(功能)RTL 仿真、(门级)静态仿真和时序仿真。

RTL 仿真就是对你的 HDL 代码仿真,对你的 RTL 级描述的设计进行测试。RTL 仿真,又叫功能仿真,也称为前仿真,是在编译之前对用户所设计的电路进行逻辑功能验证,此时的仿真没有任何延迟信息,是处于理想化状态的,仅对初步的功能进行验证。

静态仿真指对综合之后的 LUT 门级网表。静态仿真,又叫门级仿真,也称为综合后仿真,在仿真时,把综合生成的标准延时文件反标注到综合仿真模型中去,可估计门延时带来的影响,但不能估计线延时,此时的仿真也并不是十分准确,和布局布线后的实际情况还是有一定差距的。

时序仿真在选择具体器件并完成布局布线后进行的包含延时的仿真。时序仿真,又叫布局布线后仿真,是指将布局布线的延时信息反标注到设计网表中来检测有无时序违规的现象(即是否满足时序约束条件或器件固有的时序规则,如建立时间、保持时间等等。而此时,不同器件的内部延时都不太一样,不同的布局、布线方案所生成的延时也不太一样)。时序仿真包含的延迟信息最全,也最精确,能较好地反映芯片的实际工作情况。

5、编程配置(Program & Configuration)

编程配置就是生成比特流之后将比特流载入 FPGA 芯片中的一个过程。

把布局布线后生成的编程文件装入 PLD 器件中的过程称为下载。

通常将对基于 EEPROM 工艺的非易失结构 CPLD 器件的下载称为编程。一般芯片编程是指产生使用的数据文件(如比特流文件(.bit)),然后将编程数据下载到 FPGA 芯片中。

而将基于 SRAM 工艺结构的 FPGA 器件的下载称为配置。

FPGA 开发详细流程你了解吗?的更多相关文章

- [转] electron实战开发详细流程

[From] http://www.myk3.com/arc-8856.html 很久没有更新博客,人越来越懒了,唉 说好做的electron教程距离上次玩electron已经过去了好几个月了.. 这 ...

- FPGA开发流程

需求说明:Verilog设计 内容 :FPGA开发基本流程及注意事项 来自 :时间的诗 原文来自:http://www.dzsc.com/data/2015-3-16/1080 ...

- FPGA开发流程1(详述每一环节的物理含义和实现目标)

要知道,要把一件事情做好,不管是做哪们技术还是办什么手续,明白这个事情的流程非常关键,它决定了这件事情的顺利进行与否.同样,我们学习FPGA开发数字系统这个技术,先撇开使用这个技术的基础编程语言的具体 ...

- 【FPGA篇章二】FPGA开发流程:详述每一环节的物理含义和实现目标

欢迎大家关注我的微信公众账号,支持程序媛写出更多优秀的文章 FPGA的开发流程是遵循着ASIC的开发流程发展的,发展到目前为止,FPGA的开发流程总体按照下图进行,有些步骤可能由于其在当前项目中的条件 ...

- Xilinx FPGA开发环境vivado使用流程

Xilinx FPGA开发环境vivado使用流程 1.启动vivado 2016.1 2.选择Create New Project 3.指定工程名字和工程存放目录 4.选择RTL Project 5 ...

- S3C2440—3.用点亮LED来熟悉裸机开发的详细流程

文章目录 一.硬件知识 1.LED原理图 2.芯片手册 Ⅰ.找LED原理图 Ⅱ.找对应引脚 Ⅲ.在芯片手册中查找引脚信息 Ⅳ.查看寄存器说明 Ⅴ.配置寄存器 二.S3C2440框架与启动过程 三.要用 ...

- FPGA开发板

kingst.cnblogs.com 各种应用需要的接口不同: 做数字信号处理的,需要有AD/DA, 做图像处理,需要有图像接口.如果是通信的,需要有通信的接口,例如PCI/LVDS等.... 然后根 ...

- 【转】xcode APP 打包以及提交apple审核详细流程(新版本更新提交审核)

原文网址:http://blog.csdn.net/mad1989/article/details/8167529 最近项目到了最后的阶段,测试完一切ok后,准备打包以及提交,不料看到网上众教程,好多 ...

- xcode APP 打包以及提交apple审核详细流程(新版本更新提交审核)

链接地址:http://blog.csdn.net/mad1989/article/details/8167529 打包发布APP流程真机测试和APP发布流程APP提交审核流程真机测试打包发布上传出错 ...

随机推荐

- word编辑visio文件

Word文档中插入visio文件并编辑: (1)插入->对象->对象->选择“visio文件”,此种方式可插入visio文件的全部. (2)直接打开visio文件->ctrl+ ...

- Mybatis的一级缓存和二级缓存的理解以及用法

程序中为什么使用缓存? 先了解一下缓存的概念:原始意义是指访问速度比一般随机存取存储器快的一种RAM,通常它不像系统主存那样使用DRAM技术,而使用昂贵但较快速的SRAM技术.对于我们编程来说,所谓的 ...

- antd模糊搜索和远程数据的结合

//用到此方法的情景 先根据input框中的姓名模糊搜索出客户名称,当选中客户名称之后,获取ID ,根据客户的ID,去搜索数据列表. 防抖方法 let timeout; let currentVal ...

- HDU 6319

题意略. 思路:倒着使用单调队列,大的放在前,小的放在后. 详见代码: #include<bits/stdc++.h> using namespace std; typedef long ...

- Leetcode之深度优先搜索(DFS)专题-1080. 根到叶路径上的不足节点(Insufficient Nodes in Root to Leaf Paths)

Leetcode之深度优先搜索(DFS)专题-1080. 根到叶路径上的不足节点(Insufficient Nodes in Root to Leaf Paths) 这篇是DFS专题的第一篇,所以我会 ...

- CF - 1108 E 枚举上界+线段树维护

题目传送门 枚举每个点作为最大值的那个点.然后既然是作为最大值出现的话,那么这个点就是不需要被减去的,因为如果最小值也在这个区间内的话,2者都减去1,对答案没有影响,如果是最小值不出现在这个区间内的话 ...

- Codeforces Round #479 (Div. 3) B. Two-gram

原题代码:http://codeforces.com/contest/977/problem/B 题解:有n个字符组成的字符串,输出出现次数两个字符组合.例如第二组样例ZZ出现了两次. 方法:比较无脑 ...

- Codeforces Technocup 2017 - Elimination Round 2 E Subordinates(贪心)

题目链接 http://codeforces.com/contest/729/problem/E 题意:给你n个人,主管id为s,然后给你n个id,每个id上对应一个数字表示比这个人大的有几个. 最后 ...

- hdu1521 排列组合 指数型母函数模板题

排列组合 Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 65536/32768 K (Java/Others)Total Submis ...

- yzoj2057 x 题解

题意:给出一个集合,要求把这个集合分成两部分,使得一个集合中的任一元素都与另一个集合的全部元素都两两互质 暴力 枚举每个元素O(n^2)再暴力判gcd=1,如果非1就放入不同集合内,用并查集维护联通块 ...