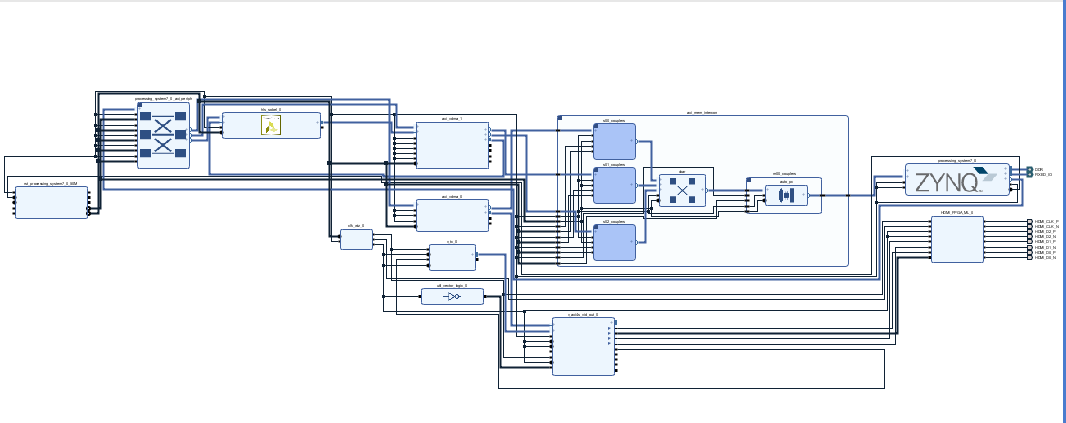

sobel算法的Soc FPGA实现之框架分析(二)

重点分析一、AXI_VDMA_1

之前一直认为这个就是内含有DDR的ip核(......最近才搞懂是个啥),后来经过对FDMA的分析发现这就是个框架,通AXI总线挂载到bus总线,可以实现PL端FPGA代码直接读写PS侧的DDR。

几个关键的AXI(AXIS)总线接口:

(1)、S_AXI_LITE接口:该接口收到ZYNQ核和GP总线控制,M_AXI_GP接口通过AXI-Lite总线控制VDMA的配置

(2)、M_AXIS_MM2S接口:本接口将从DDr中读取的数据发送到sobel处理ip

(3)、M_AXIS_S2MM接口:该接口接收sobel处理ip核的输出数据流

(4)、M_AXI_S2MM接口:该接口将数据输出到ZYNQ处理器,然后数据可以刷入DDR

(5)、M_AXI_MM2S接口:该接口接收来自DDR的像素数据

学习完FDMA之后,对VDMA才有了一个初步的了解,VDMA就是通过AXI(AXIS)总线挂载到总线的典型应用,M_AXI_MM2S接口接收到来自ps侧DDR的像素数据,然后通过M_AXI_MM2S将数据发送到sobel ip核,ip对图片数据进行处理后进行将数据转换为AXI_STREAM格式,可以在上一篇博文中看到,输出数据通过S_AXIS_S2MM进入VDMA,然后,由于在VDMA中设置的是三帧缓存,这三帧数据并不是在VDMA中缓存的,是在DDR中进行缓存。那么VDMA与三帧数据的关系是什么?参考FDMA中的设计,CDMA就是对输入数据设计了一个标志位flag,保证有三帧数据传送到DDR进行缓存。数据通过M_AXI_MM2S接口进入DDR。

那么,AXI_CONNECT1的作用中有一个S00_AXI的作用=是什么?可以看到该总线发出读请求,读取ps侧DDR缓存的像素数据。

其他分析二、AXI_VDMA

框架流程:就是将图像数据以二进制形式进行存储,ZYNQ通过AXI_GP接口对各个模块进行配置,将sobel处理的结构通过stream数据流发送到vdma0,再经过stream2video进行转换,将输出图像发送到HDMI核,video timing核的作用是进行时钟约束,其中HDMI的主时钟是74.25Mhz,除此之外还输入一个串转并数据时钟,为主时钟的5M:74.25*5Mhz。

复位管理单元的作用是将复位信号于时钟进行同步处理,所以主时钟连接到复位管理单元的同步时钟端,由ZYNQ产生的复位信号连接到ext_reset_in,就是extern外部复位信号输入。输出两个信号,一个信号用于专用于AXI总线互联模块,另一个用于模块以及AXI传输的复位信号。个人理解是这个peripheral_reset的作用是局部模块的复位信号,但是它好就好在与AXI_CLK同步,可以在AXI的局部传输中进行复位,AXI_CONNECT的总复位信号是interconnect_aresetn,在信号处理中,复位判断语句应该是(interconnect_aresetn||M02_ARESETN),此处的M02_ARESETN仅是用来举例,还可以是其他的复位信号

VDMA0为什么不用设置成可写呢?

因为数据通过MM2S仅可从GP来到VDMA0,然后经过三帧缓存之后从MM2S到stream视频流输出IP, 将HDMI核需要的信号给HDMI控制器,比较关键的一点是Video Out的vtg_ce,用于暂停时序发生器以达到同步的的目的。

sobel算法的Soc FPGA实现之框架分析(二)的更多相关文章

- PHP 面向对象及Mediawiki 框架分析(二)

mediaHandler可以理解为处理media文件的 /includes/filerepo/file/File.php /** * Get a MediaHandler instance for t ...

- 14FPGA综设之图像边沿检测的sobel算法

连续学习FPGA基础课程接近一个月了,迎来第一个有难度的综合设计,图像的边沿检测算法sobel,用verilog代码实现算法功能. 一设计功能 (一设计要求) (二系统框图) 根据上面的系统,Veri ...

- SoC FPGA JTAG电路设计 要点

JTAG协议制定了一种边界扫描的规范,边界扫描架构提供了有效的测试布局紧凑的PCB板上元件的能力.边界扫描可以在不使用物理测试探针的情况下测试引脚连接,并在器件正常工作的过程中捕获运行数据. SoC ...

- SoC FPGA开发板的FPGA配置数据下载和固化

小梅哥编写,未经许可,严禁用于任何商业用途 2018年7月2日星期一 soc fpga的烧写和固化方式与传统的纯fpga固化方式即存在形式上的相同,也存在细节上的差异,特整理此文. AC501-So ...

- Intel Cyclone SoC FPGA介绍

3.1 Intel Cyclone SoC FPGA介绍 3.1.1 SoC FPGA的基本概念 Intel Cyclone V SoC FPGA是Intel PSG(原Altera)于2013年发布 ...

- Sobel算法

最近看了一些Sobel算法,并试了一下,源码如下: private void Sobel(Bitmap img) { int width = img.Width; int height = img.H ...

- opencl+opencv实现sobel算法

这几天在看opencl编程指南.照着书中的样例实现了sobel算法: 1.结合opencv读取图像,保存到缓冲区中. 2.编写和编译内核.并保存显示处理后的结果. 内核: const sampler_ ...

- 【原创】Linux v4l2框架分析

背景 Read the fucking source code! --By 鲁迅 A picture is worth a thousand words. --By 高尔基 说明: Kernel版本: ...

- Python遗传算法工具箱DEAP框架分析

本文主要介绍python遗传算法工具箱DEAP的实现.先介绍deap的如何使用,再深入介绍deap的框架实现,以及遗传算法的各种实现算法. 代码可以参考 https://github.com/suma ...

随机推荐

- ESP8266-让灯闪烁

例子一:让板子上的LED_BUILTIN灯进行闪烁 void setup() { pinMode(LED_BUILTIN,OUTPUT); } void loop() { digitalWrite(L ...

- 弹性盒子FlexBox简介(二)

弹性盒子属性 一.align-content属性 属性作用:用于修改flex-wrap属性行为.类似于justify-content,但它不是设置弹性子元素的对齐,而是设置各个行的对齐. 属性值: f ...

- 使用HTML和CSS来实现为文字设置图片底纹

先看一下最终实现的效果 图中的hello是文本而不是图片 那么如何实现这种效果呢? HTML部分: 创建一个h1标签 ,标签内容为(hello).通过link标签链接外部样式表style.css. s ...

- django-rest-swagger 使用【转】

转自:https://www.cnblogs.com/delav/p/10242017.html Swagger是一个API开发者的工具框架,用于生成.描述.调用和可视化RESTful风格的Web服务 ...

- Codeforces Round #603 (Div. 2)F. Economic Difficulties

F. Economic Difficulties 题目链接: https://codeforces.com/contest/1263/problem/F 题目大意: 两棵树,都有n个叶子节点,一棵树正 ...

- [CSP-S模拟测试]:题(DP+数学)

题目描述 出个题就好了.这就是出题人没有写题目背景的原因.你在平面直角坐标系上.你一开始位于$(0,0)$.每次可以在上/下/左/右四个方向中选一个走一步.即:从$(x,y)$走到$(x,y+1),( ...

- C++中一些容易迷惑的语法点总结

#include<iostream> #include<cstring> using namespace std; int main(){ ][]={{,,},{,,}}; ] ...

- 麦子lavarel---10、一些第三方应用注意

麦子lavarel---10.一些第三方应用注意 一.总结 一句话总结: 其实把重要的几个功能弄一个就好了,邮箱验证,手机号验证,支付验证,都是调用第三方接口,也很简单 1.关于页面和服务端校验的看法 ...

- SQLSTATE[HY000] [2002] No such file or directory

正常的解决办法.. 只需将laravel配置文件中的host 127.0.0.1改成localhost就可以: 'mysql' => array( 'driver' ...

- Flask中的对象的配置

常用的有 1.'DEBUG': False, # 是否开启Debug模式 2.'TESTING': False, # 是否开启测试模式 3.'SECRET_KEY': None # 在启用Flask内 ...