modelsim 仿真xilinx fir ip

到现在不管fir ip 用的对不对,但是在使用modelsim是可以仿真fir ip的。

具体步骤:

1、仿真库,添加到modelsim目录配置文件:

2、将这个文件中的:

;List of dynamically loaded objects for Verilog PLI applications

;Veriuser = D:/modeltech64_10.2c/convert_hex2ver.dll

改成如下:

List of dynamically loaded objects for Verilog PLI applications

Veriuser = D:/modeltech64_10.2c/convert_hex2ver.dll

这样的目标是完成 mif 到 hex文件的转换。 前提是convert_hex2ver.dll 文件, 存放在D:/modeltech64_10.2c/ 目录下。

3、将调用 ip 时产生的 mif 文件,拷贝到 modelsim 的工作目录下。

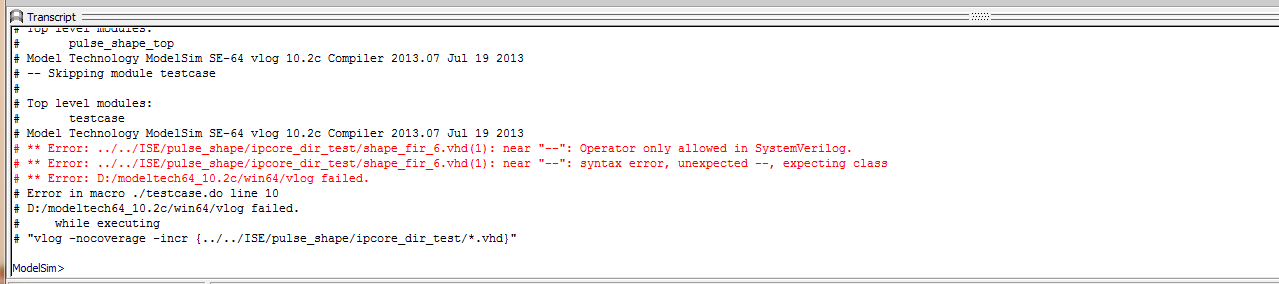

4、单独编译 .vhd 文件,因为用下面的代码无法编译 .vhd 文件。也不知道是什么问题?????????错误提示如下:

5、再加上如下的代码:

destroy .wave

quit -sim

vlib work

vmap work work

#编译上上层目录中的SRC目录下的所有.V文件

vlog -cover bces -incr {../../SRC/*.v}

#编译上层目录中的所有.v文件

vlog -nocoverage -incr {../*.v}

#vlog -nocoverage -incr {../../ISE/pulse_shape/ipcore_dir_test/*.vhd}

#-L unifast_ver -L unifast

vsim +ALL_TESTCASE -coverage -novopt -L unisims_ver -L unisim -L unimacro_ver -L unimacro -L simprims_ver -L secureip work.testcase

#vsim +UT_TESTCASE_001 -coverage work.testcase

#vsim +UT_TESTCASE_002 -coverage work.testcase

#vsim +UT_TESTCASE_003 -coverage work.testcase

do wave.do

# 此处在保持wave.do后有效

#simulates all signals including hidden signals

log -r *

run 1ms

coverage report -recursive -select bces -file Coverage.txt

coverage report -totals -file CoverageResult.txt

coverage report -lines -byinstance -select bces -file CoverageDetail.txt

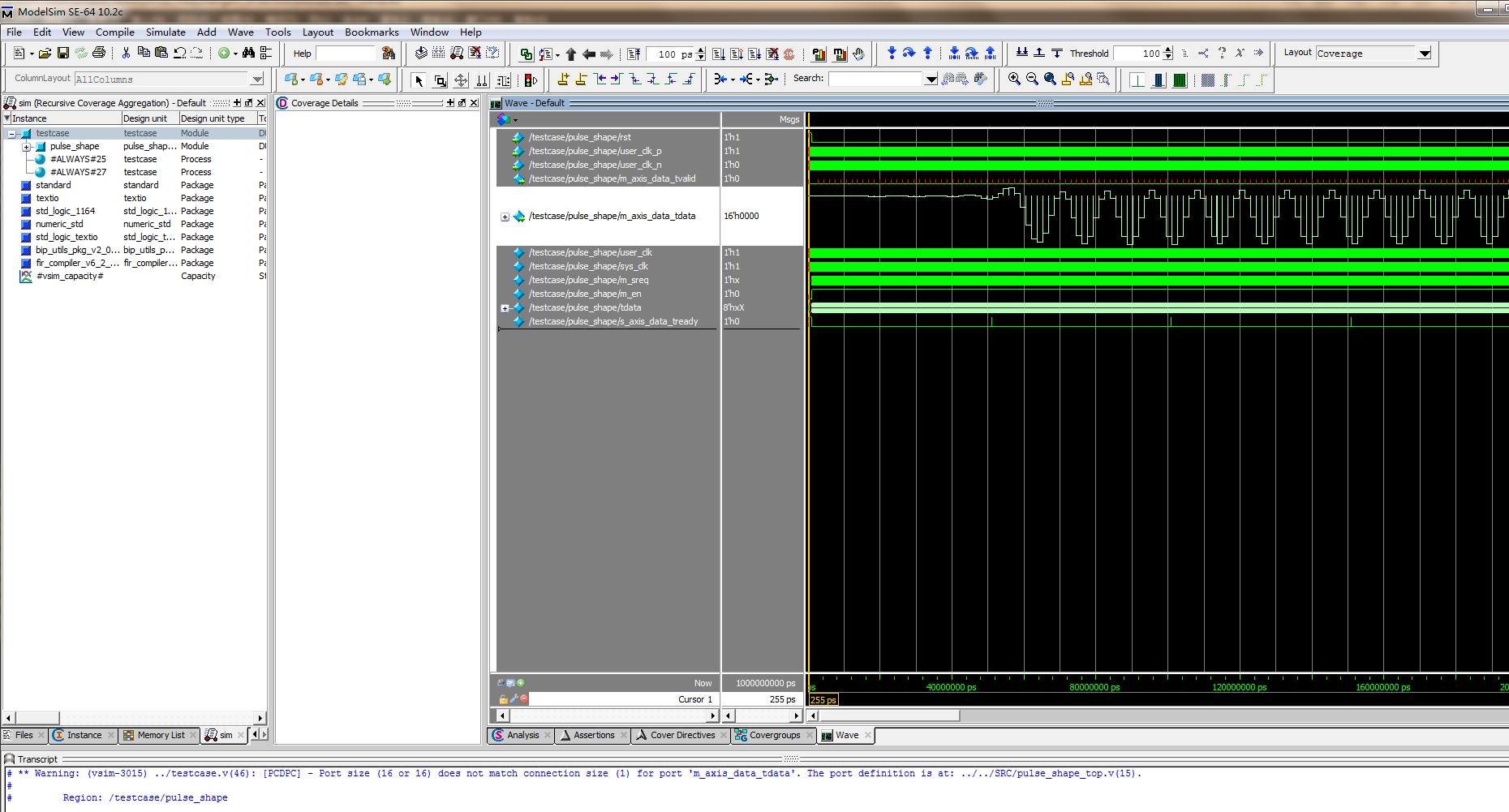

完成:

modelsim 仿真xilinx fir ip的更多相关文章

- modelsim仿真xilinx mig ip core相关问题

1.运用自动化脚本文件 do sim.do 其中不支持 .f文件 , 需要直接vlog 2.对于mig模型采用下面句型(根据example中do sim.do文件) vlog -sv +define ...

- modelsim仿真xilinx ram输出均为0

现象 在vivado2018.3下生成了RAM IP,丢到modelsim中仿真发现doutb输出均为0.调整AB端口的时钟速率,发现低于5ns不行,输出为0.但5ns以上正常. 解决方法 比对了vi ...

- 每天进步一点点------Modelsim添加Xilinx仿真库的详细步骤

Modelsim,可以选型SE和XE两个版本.Modelsim XE可以直接被ISE调用,而Modelsim SE需要手动添加仿真库.但SE版和OEM版在功能和性能方面有较大差别,比如对于大家都关心的 ...

- Modelsim se仿真Xilinx IPcore

Modelsim se仿真Xilinx IPcore 方法:先写好do文件常规框架,根据modelsim报错再添加ise IP核库仿真文件.注:记得添加并仿真glbl.v全局控制仿真文件到sim/is ...

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

- Modelsim SE 仿真 ALTERA FPGA IP

Modelsim SE 仿真 ALTERA FPGA IP 最近,有几个朋友问过我是不是有新版本的Modelsim altera,其原因是 Qii 升级为新版本的,但是没配套的modelsim,没办法 ...

- 如何用ModelSim对Xilinx ISE产生的网表进行仿真

图: 在对设计的芯片进行测试时,经常要用到FPGA,可是里面的仿真工具却不如Modelsim那么好用,且在规模比较大时,ISE在仿真时,软件经常会报告内存限制的问题,此时一般会切换到Modelsim软 ...

- Modelsim, Debussy联合仿真Xilinx

http://wenku.baidu.com/view/8363d40003d8ce2f006623e9.html 另外一个博客 生成Xilinx库 先调用ISE的simulation librar ...

- ModelSim仿真入门

ModelSim仿真入门之一:软件介绍 编写这个教程之前,为了让不同水平阶段的人都能阅读,我尽量做到了零基础入门这个目标,所有的操作步骤都经过缜密的思考,做到了详细再详细的程度. 如果您是FPGA开发 ...

随机推荐

- mongodb的安装与增删改查

mongodb是一款分布式的文件存储的数据库,注意这两个词,分布式和文件存储.mongodb支持复制和分片,可以合理的运用空间的大小,也可以达到容灾的目的.另外文件存储也是一个特点,抛弃了传统的表的概 ...

- Message: dlopen failed for module ‘x’: file not found

这是未安装bochs-x的缘故 解决方案: sudo apt-get install bochs以后接着安装bochs-x. sudo apt-get install bochs-x 2.bx_dbg ...

- display:box,按比列划分,水平均分,及垂直等高

一.按比例划分 <div class="test"> <p id="p1">Hello</p> <p id=" ...

- 【Python】解决测试依赖之 Mock模块的基本使用

什么是mock? Mock,顾名思义,模拟,在我们日常生活中或者影视作品中见得最多的可能就是预备飞行员的模拟训练,印象比较深的是电影<萨利机长>中的模拟器,经过几千次模拟,人们得出机长萨利 ...

- 雷林鹏分享:Ruby Dir 类和方法

Ruby Dir 类和方法 Dir 是一个表示用于给出操作系统中目录中的文件名的目录流.Dir 类也拥有与目录相关的操作,比如通配符文件名匹配.改变工作目录等. 类方法 序号方法 & 描述 1 ...

- django使用bootstrap快速美化 admin后台

使用django-admin-bootstrappe快速美化后台 两步: 1.pip install django-admin-bootstrapped 安装应用 2.在setting.py里面添加 ...

- java网络编程之Socket编程

概念 网络编程分为BIO(传统IO).NIO.AIO.Socket编程属于BIO这种传统IO. InetAddress java.net.InetAddress是JAVA中管理IP地址的类,常用 pu ...

- Python在七牛云平台的应用(一)

七牛云:(引用百度的介绍)七牛云是国内领先的企业级公有云服务商,致力于打造以数据为核心的场景化PaaS服务.围绕富媒体场景,七牛先后推出了对象存储,融合CDN加速,数据通用处理,内容反垃圾服务,以及直 ...

- STL中的map

map 容器 提供 1 对 1 的关系 定义方式: map<string,int>mp; 写在前面的是关键字. 数据插入: 1.使用 insert 插入 pair 数据 mp.insert ...

- 【MVC】ASP.NET MVC 4项目模板的结构简介

引言 在VS2012新建一个窗体验证的MVC 4项目后,可以看到微软已经帮我们做了很多了,项目里面该有的都有了,完全可以看成一个简单网站.作为开发,能理解里面文件结构和作用,也算是半只脚踏进M ...