Vivado 2017封装自定义IP Core

使用Vivado2017.3自定义IP Core。通常情况下,我们做设计采用模块化设计,对于已经设计好的一部分模块功能,就可以直接拿来调用,IP Core就是这样来的,一般来说我们看不到IP Core的源码,这也是Xilinx为了保护作者知识产权,对IP Core进行加密。对我们开发者而言,我们也可以自定义封装自己的IP Core,需要用的这部分功能的时候,只需要直接添加IP Core进来就行了,来一起搭起你的数字积木吧!

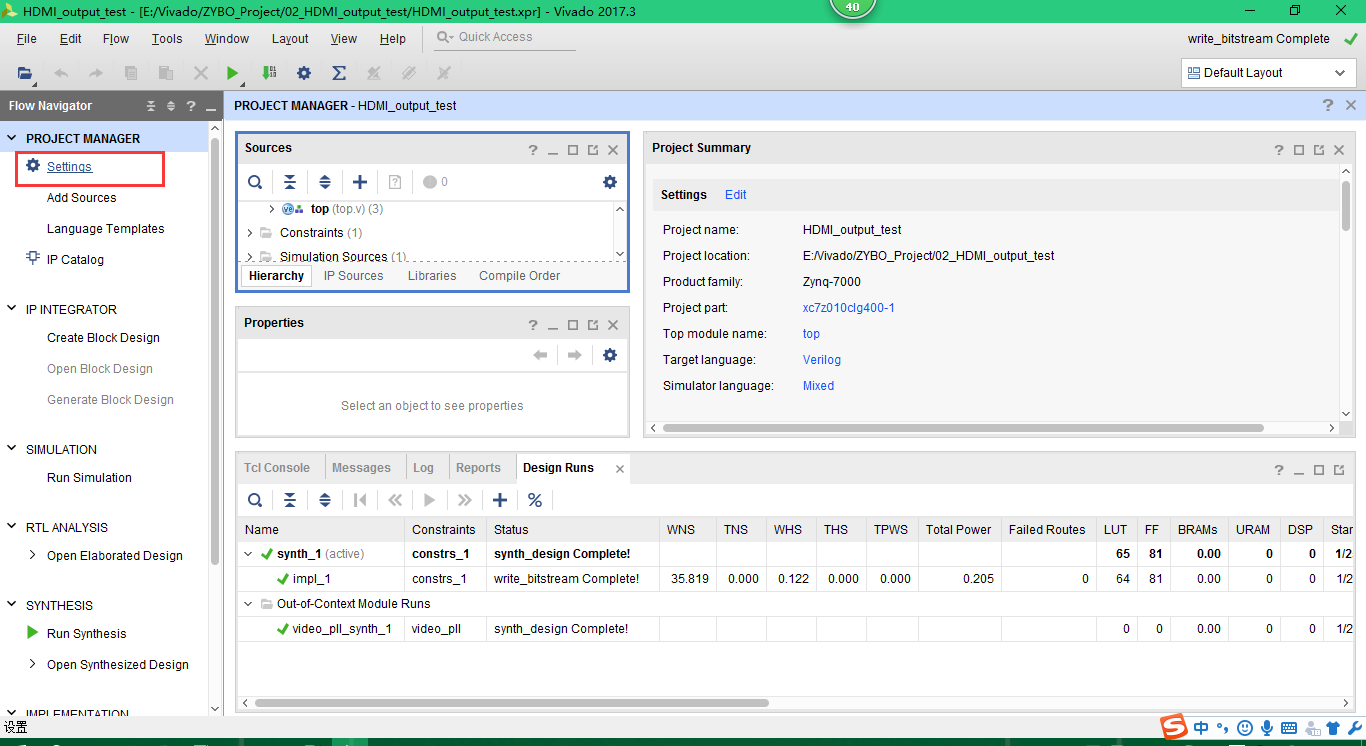

将你要封装的代码建立成一个工程,然后点击如图所示setting。

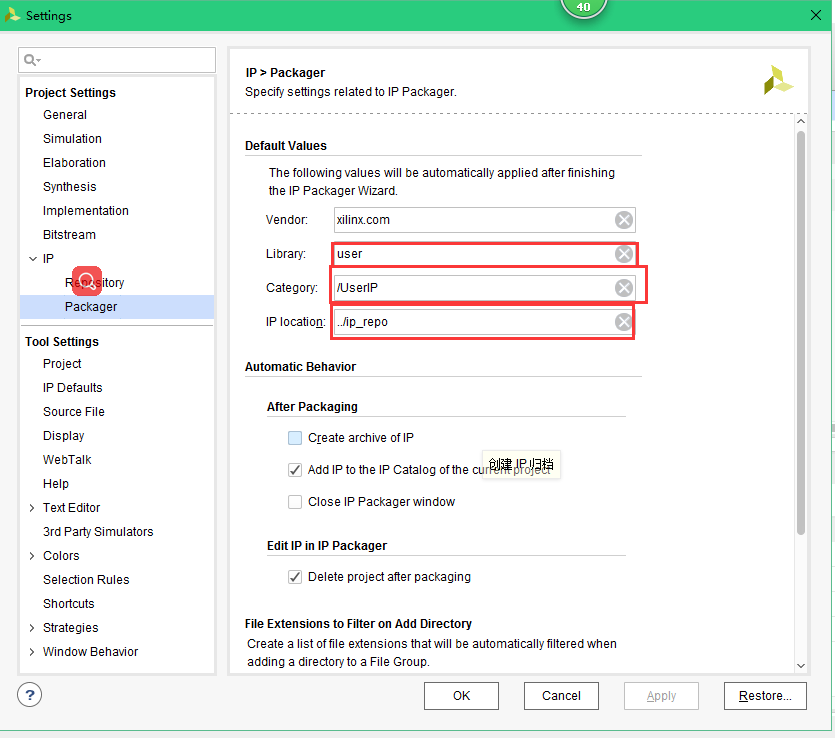

点击IP——Package,图中所标注的都是可以编辑的,这里可以自定义库名等,默认也可。

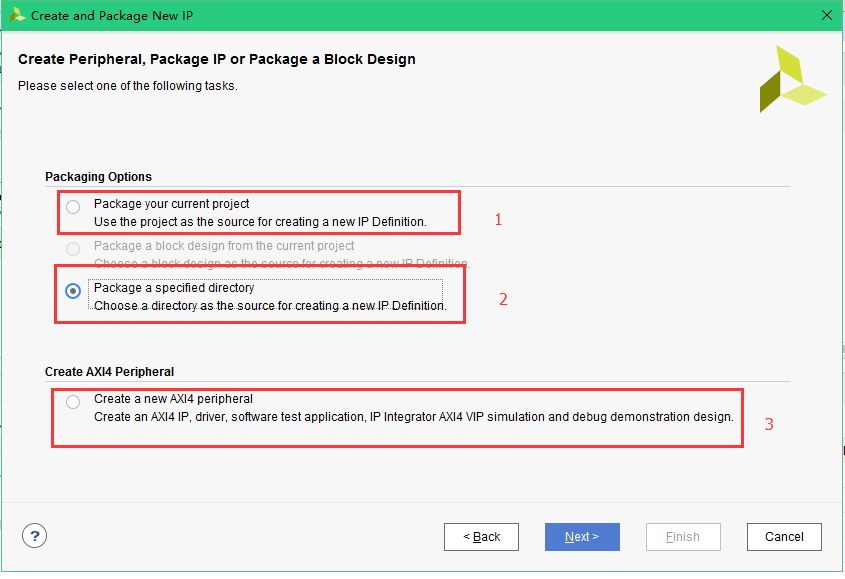

设置完成后,回到主界面,在主菜单上方点击tools——Create and Package New IP

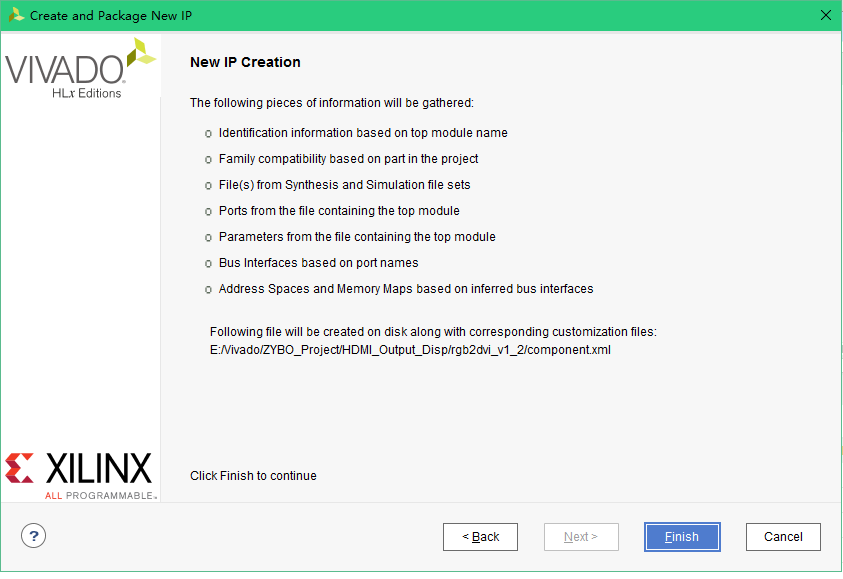

根据提示一步步走下去。

第一个是将当前工程创建成IP

第二个是将指定目录下的工程创建成IP

第三个是封装成SOC部分的IP

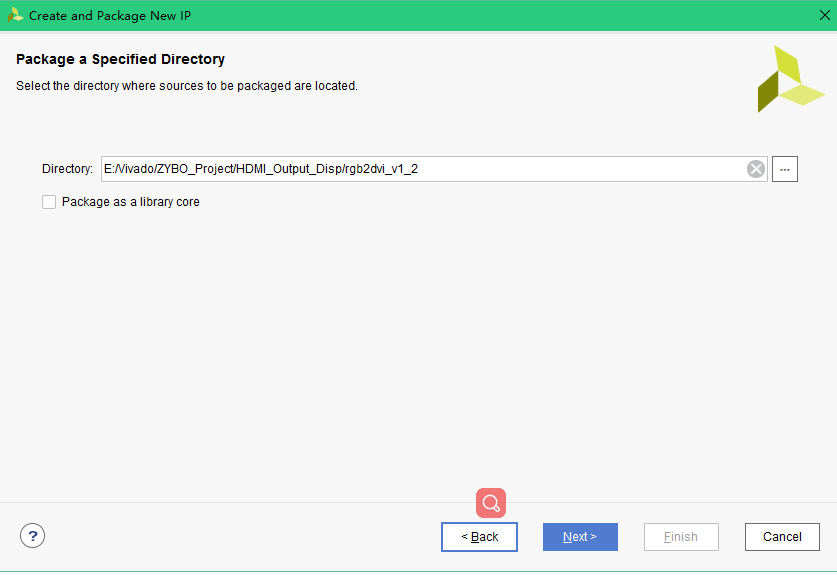

这里因为我选择的是第二个,因为的我是封装其他工程中的代码,一般情况下选择第一个。按照流程走就可以了。

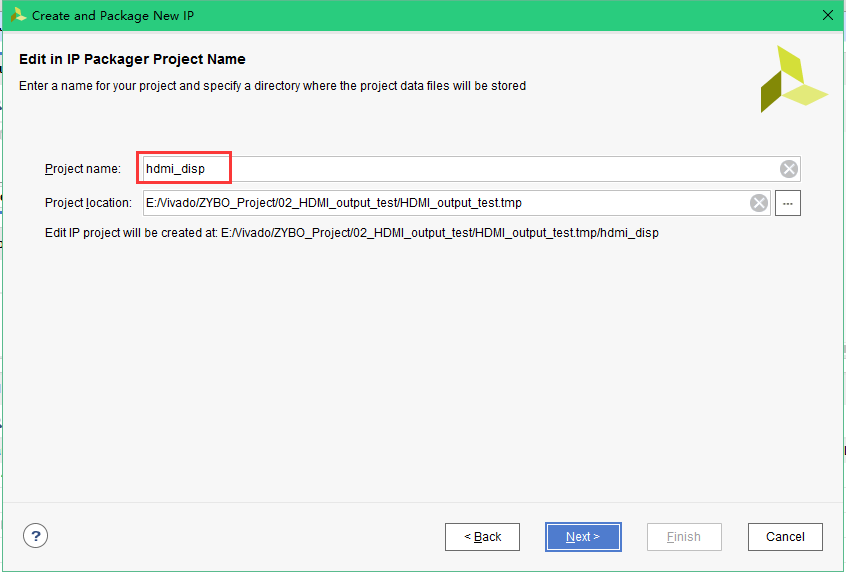

设置路径,工程名,

最后点击finish,创建工程。

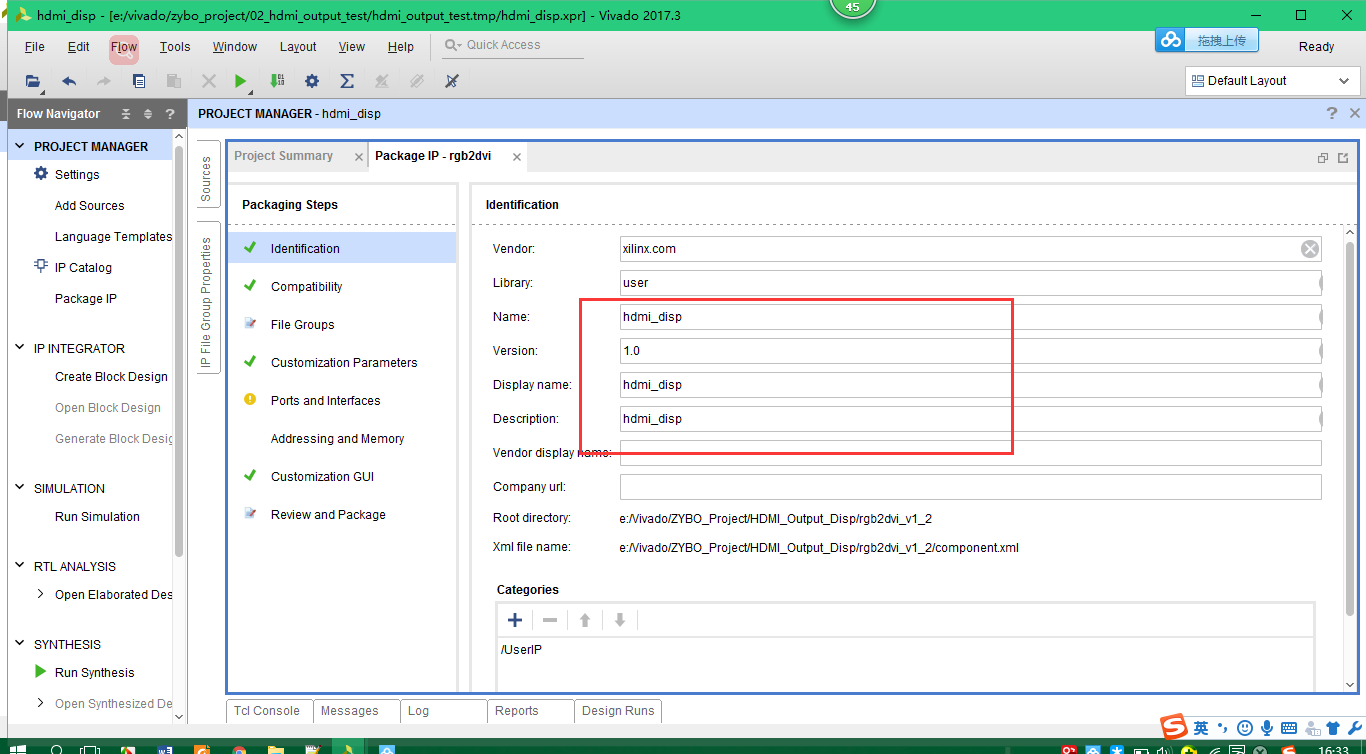

在工程主界面,点击Identification中可以设计IP Core名称和版本描述。

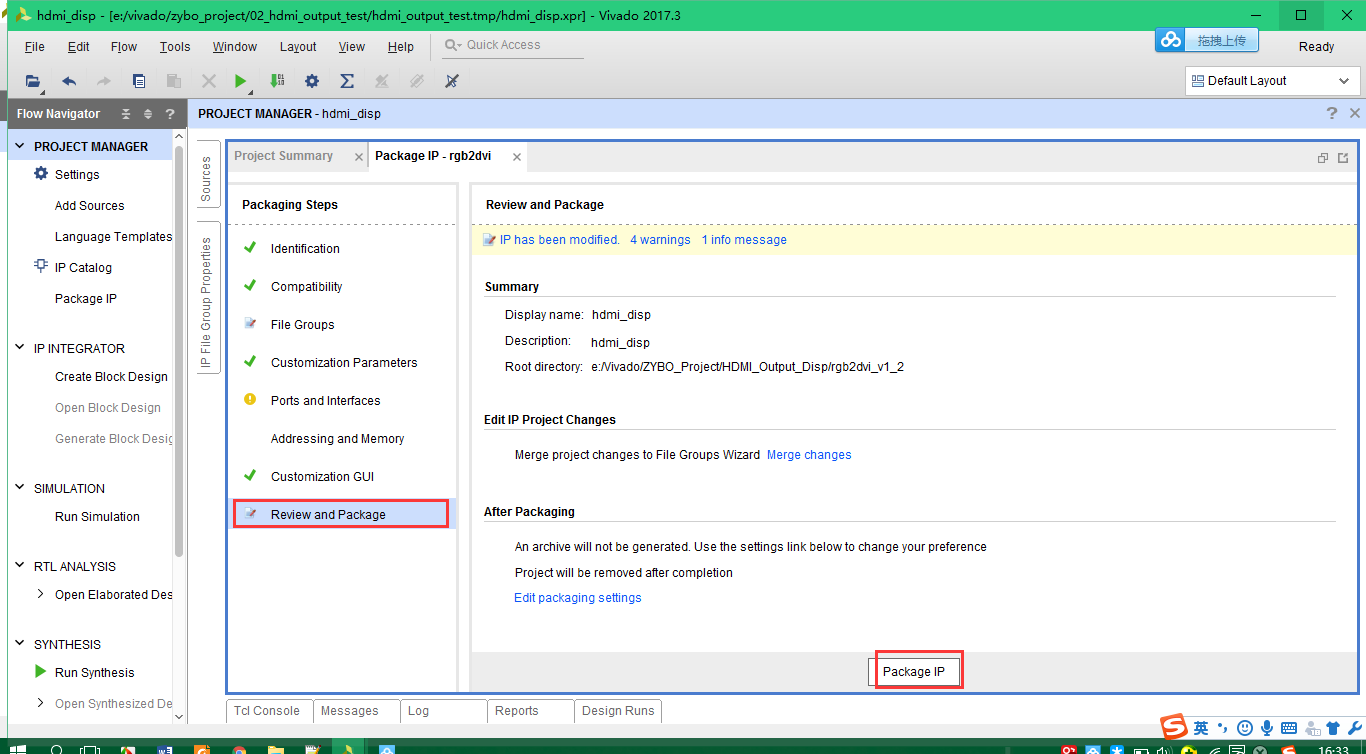

这里直接跳到最后一步,点击Package IP,然后就封装成功了。

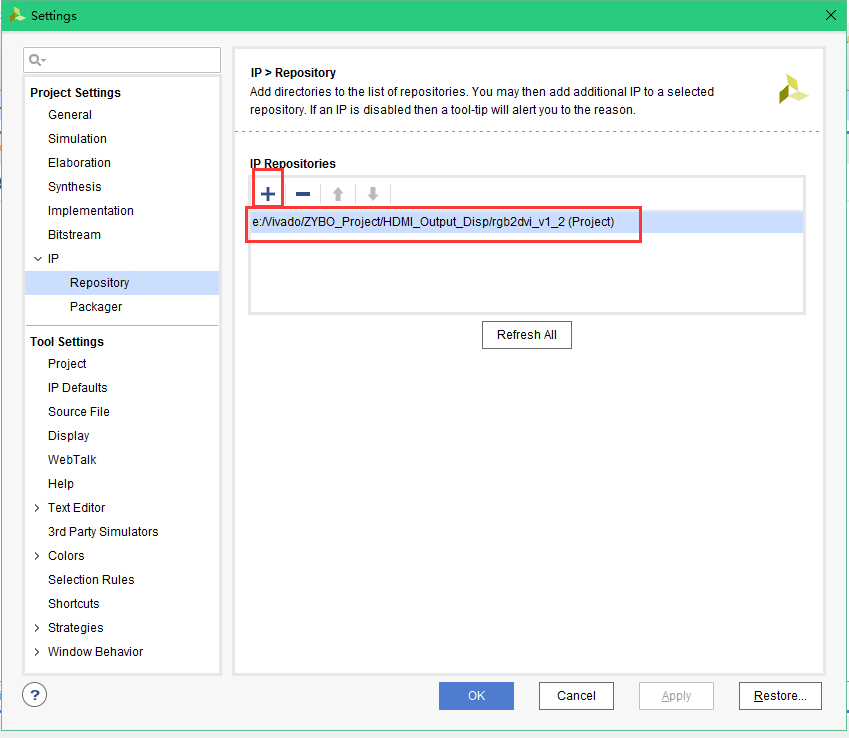

需要你封装的IP时,主界面setting——IP——Repository中添加你封装好的文件夹路径。

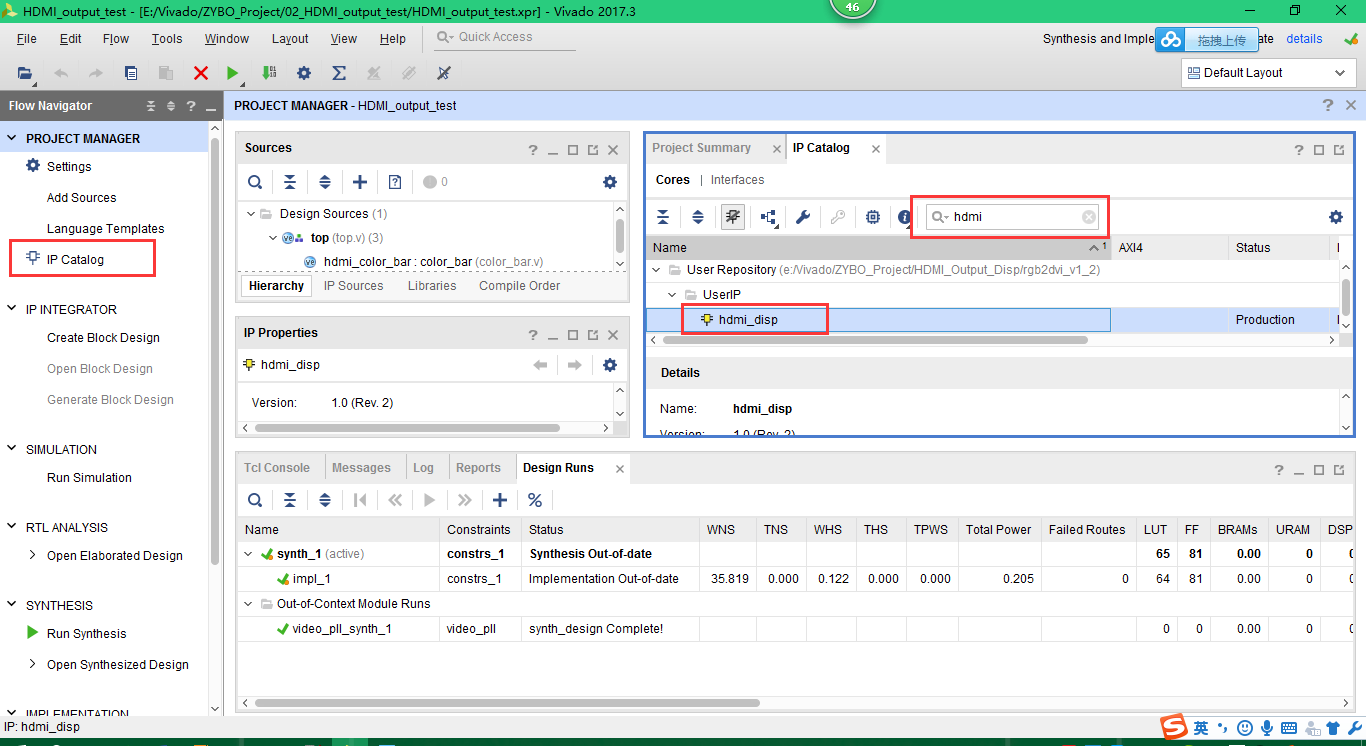

添加完成后,点击IP Catalog,搜索你的IP Core,双击就可以直接调用了。

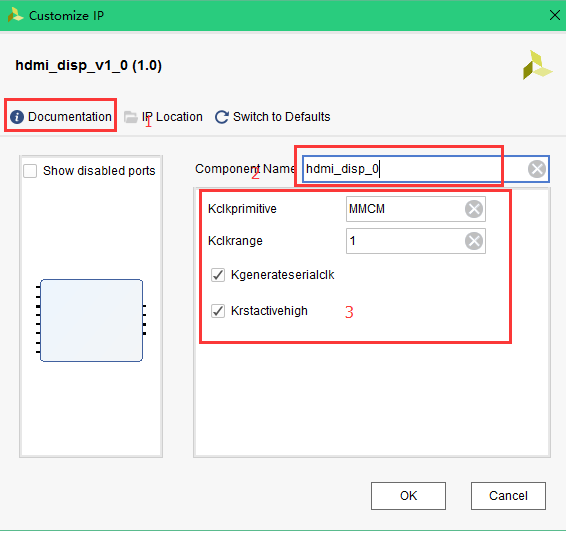

接下来的流程就和调用其他IP时候使用的相似的。我这里封装的是一个HDMI的代码,因为代码比较多,而且使用VHDL语言写的,但是在Verilog HDL的工程中也可以调用,所以为了便捷,把它封装成一个IP Core。

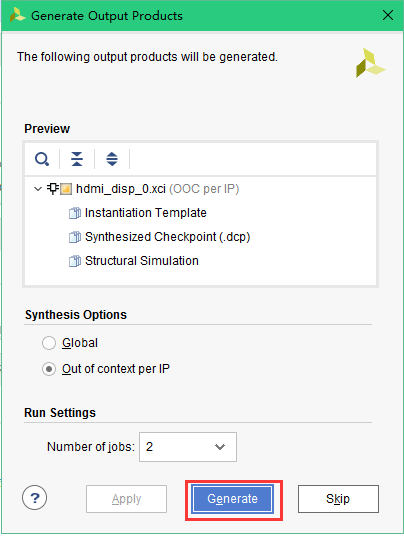

点击Generate就生成,可以直接使用了。

最后欢迎关注一亿人都想要关注的微信订阅号【开源FPGA】,总结、记录自己的学习过程,一个FPGA工程师的养成之路。欢迎加入开源FPGA-交流群-I进行讨论,群号码:677163633。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/8370843.html

Vivado 2017封装自定义IP Core的更多相关文章

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- vivado设计四:自定义IP核测试

在vivado设计三中:http://blog.chinaaet.com/detail/37177已经建立了vivado工程和封装好了自定义IP核. 那么接下来,我们对这个自定义IP核进行测试了:我们 ...

- vivado设计三:一步一步生成自己的自定义IP核

开发环境:xp vivado2013.4 基于AXI-Lite的用户自定义IP核设计 这里以用户自定义led_ip为例: 1.建立工程 和设计一过程一样,见vivado设计一http://blog. ...

- 强大的Vivado IP工具——自定义IP的使用

首先,要指出,本文不描述任何IP的功能与使用. 在开发一个大型FPGA项目时,多人协作是必不可少的.这个时候,如何提交设计给负责集成的人,是项目开发中最关键的问题之一. 常用的一个方法是,提交网表 ...

- ZYNQ笔记(7):AXI从口自定义IP封装

使用 AXI_Lite 从口实现寄存器列表的读写,并且自己封装为一个自定义 IP,以便以后使用.本次记录的是 M_AXI_GP0 接口,此接口是 ARM 作为主机,FPGA 作为从机,配置 FPGA ...

- ZYNQ笔记(6):普通自定义IP封装实现PL精准定时中断

软件的定时中断很难控制精准触发沿的位置,可以通过 PL-PS 的中断完成精准的定时中断.PL 的中断通过 Verilog 代码产生,这样紧密结合 PS-PL 的处理,发挥各自的优势. 一.PL 侧定时 ...

- Xilinx Vivado的使用详细介绍(5):调用用户自定义封装的IP核

Zedboard OLED Display Controller IP v1 介绍 Author:zhangxianhe 本文档提供了快速添加,连接和使用ZedboardOLED v1.0 IP内核的 ...

- 第三章 VIVADO 自定义IP 流水灯实验

第二章里面已经说过了,MIZ701 PL部分没有输入时钟,因此驱动PL资源必须是通过PS来提供时钟,所以这个流水灯实验也得建立一个最小系统了,然后再添加一个流水灯的自定义IP. 3.0本章难度系数★★ ...

随机推荐

- LDAP基本概念

LDAP(Lightweight Directory Access Protocol)是一种基于计算模型的客户机/服务器X.500目录服务访问协议.LDAP是从X.500目录访问协议的基础上发展过来的 ...

- java的按值传递与按引用传递

还是比较混乱 主要看怎么理解了 java没有指针一说是因为jvm将指针给隐藏了起来 说到底还是靠地址 按值传递显然直接将内存空间的内容传递给对方 之后再与传递者无关 引用是在栈空间建一个堆空间对象的映 ...

- 五、jdk工具之jmap(java memory map)、 mat之四--结合mat对内存泄露的分析、jhat之二--结合jmap生成的dump结果在浏览器上展示

目录 一.jdk工具之jps(JVM Process Status Tools)命令使用 二.jdk命令之javah命令(C Header and Stub File Generator) 三.jdk ...

- 面试总结之MISC(操作系统,网络,数学,软件开发,测试,工具,系统设计,算法)

操作系统 解释堆和栈的区别. 分配在堆的内存与分配在堆栈的内存有什么不同 分配在堆的内存要手动去释放 线程与进程的区别 多线程中栈与堆是公有的还是私有的 在多线程环境下,每个线程拥有一个栈和一个程序计 ...

- [转][Dapper]SQL 经验集

condition.Append(" AND ChineseName like @name"); p.Add("@name", "%" + ...

- [Java.web]MVC 案例-开发用户模块(注册)

代码下载 生成后的 user.xml 路径在 X:\day09_user\WebRoot\WEB-INF\classes\users.xml 使用测试 在 day09 项目上右键 -> Run ...

- php删除制定文件及文件夹

php遍历一个文件夹内的所有文件和文件夹,并删除所有文件夹和子文件夹下的所有文件的代码,通过递归方式实现达到清空一个目录的效果,代码简单实用. 用到的函数: scandir($path) 遍历一个文件 ...

- leetcode257

/** * Definition for a binary tree node. * public class TreeNode { * public int val; * public TreeNo ...

- 「小程序JAVA实战」小程序查看视频发布者信息(64)

转自:https://idig8.com/2018/09/24/xiaochengxujavashizhanxiaochengxuchakanshipinfabuzhexinxi63/ 当我们点击右下 ...

- 使用API调用外部程序并监控程序状态

Public Type SHELLEXECUTEINFO cbSize As Long fMask As Long hwnd As Long lpVerb As String ...