《FPGA全程进阶---实战演练》第八章之程序架构格式说明

首先在书写程序时必须有的部分,就是模块module部分,整体的架构如图8.1所示。

图8.1 程序整体架构

首先要声明模块名,在module后面加上模块名,这里最好以所建立模块要实现的功能去命名此模块,因为这样在查阅时方便去寻找此模块的功能,一目了然。紧接着在方框内要列出所有的输入和输出信号,都要在方框中写出。作为一个整体的模块,凡事出现module的部分一定要加上endmodule才算完整,这是一个完整的模块。

在输入信号中,有两个信号是一定要加上去的,就是时钟信号和复位信号,要做到对整体设计可控,全局时钟信号和复位信号必须加上。在声明括号对输入和输出信号列写完毕之后,还要在module内部再次声明到底哪个是输入信号,哪个是输出信号,这就有了124行到128行的声明。在always语句中用到的一些变量需要定义为reg类型,也就是寄存器类型,方可在always中使用,wire类型不可以在always语句中使用。

我们在看别人写的代码时常常看到类似于130行到153行所示的结构,这是怎么回事?这是要做什么?这就要利用我们数电知识里面的组合逻辑和时序逻辑的比较了,在要求对变量存储的场合,需要时序逻辑,组合逻辑只能输出数据,但是不能存储。当然还有组合逻辑是电平触发,而时序逻辑是时钟沿触发。所以130行到153行构建了一个庞大的锁存器,构成时序逻辑电路。对于130行小括号内部的属于敏感型变量,即发生变化时,会带动整个always 语句进行更新变化。其中rst_n(这个是复位信号,可以按自己的习惯去定义。)也定义为边沿敏感型变量,但是在always语句中的内部又出现了rst_n,这是为什么呢?一个信号如果是时钟信号,那么必定不会出现在always语句中,可见rst_n不是时钟信号。那么综合器会不会认为rst_n是一个时钟信号呢?

对于边沿触发型时序模块的verilog设计,有以下规律可循:

(1)若敏感型变量定义为时钟信号,不要在always语句中再出现。

(2)若某信号定义为相对于时钟的电平敏感的异步控制信号,除了在敏感型变量表中列出,还要在always语句中指出其逻辑行为。

(3)若某信号是相对于时钟的同步控制信号,不能出现在敏感型变量表中。

由上面的程序结构,为rst_n指定了if语句,会导致所有未能进入敏感信号的变量都必须是相对于时钟同步的。可见这是独立于主时钟的时序或组合逻辑,属于第二种情况。

(4)敏感型变量表中不允许出现混合信号。

always@(posedge clk or rstn) 或 always@(posedge clk or negedge rstn or a)

上述结构都是不允许的,在综合时会出现 双边沿敏感信号的错误。

(5)不允许在敏感型列表中出现除时钟和异步控制信号之外的其他信号,一般的逻辑控制信号不允许出现在敏感型列表中,always@(posedge clk or negedge a)

其中a的作用同rstn,但是a不能用于其他逻辑行为 。如q = a & b;

可见verilog 描述敏感型时序电路较多的依赖于语法的规定和表述的规则

If语句中对异步控制信号rst_n进行判断,然后对数据进行初始化,初始化完成之后在执行其他条件,else if......else,其中的begin....end是针对于条件语句中有多步执行程序时,构建成一个整体,隶属于else if语句或者else语句。

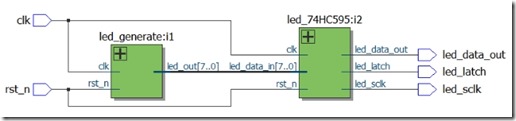

155行到157行对于用户所使用的输出信号进行赋值。以上是针对单个module的建立,若是只是建立单个module,在建立工程时必须将module的名字和工程名字一致,如图8.2所示,否则会出错。对于多个模块构建,需要建议一个顶层模块,然后将各个子模块进行连接,这时用到了wire变量,如图8.3所示,注意wire类型的LED信号,起到连接各个模块的作用。图8.4是多个模块的RTL视图部分,可以看到wire的作用。

图8.2 单个模块命名

图8.3 多个模块命名

图8.4 RTL视图

TESTBENCH格式说明

当逻辑部分创作完成后,需要对逻辑程序进行行为仿真,那么就需要写仿真程序。

`timescale 1 ns/ 1 ns

module led_source_tst();

//----------------------------------------------

//-----------description of input signal--------

reg clk;

reg rst_n;

//clk 和rst_n是全局的时钟和复位信号

//----------------------------------------------

//-----------description of output signal--------

wire [3:0] led_out;

Wire .....

Wire .....

//在modelsim仿真时,.v文件中的input在modelsim中用reg类型,如clk是input,

//上面modelsim是用reg,.v文件中的输出,即output,在modelsim中是wire,这一点要牢记

//----------------------------------------------

//-----------description of each module-------------------------

led_source

#(.LED_WIDTH(4))

i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

//.cnt1(cnt1),

//.flag_cnt1(flag_cnt1),

.led_out(led_out),

//.led_out_cnt1(led_out_cnt1),

.rst_n(rst_n)

);

//这一部分是对建立的.v文件中的模块声明部分,led_source就是.v文件中的模块名字

//------------------------------

//generate clock

localparam PERIOD = 20; //50MHz

initial

begin

clk = 0 ;

forever #(PERIOD / 2) clk = ~clk;

end

//上面这一段是针对clk信号做的模拟仿真;

//------------------------------

//task reset

task task_reset;

begin

rst_n = 0 ;

repeat(2) @(negedge clk);

rst_n = 1 ;

end

endtask

//上面一部分是针对复位信号,也就是rst_n。

//一开始也是赋初值rst_n = 0 ;然后利用repeat重复执行命令;

initial

begin

$monitor($time,"led_value = %04b\n", led_out); //just test the changing of led_out //value

task_reset;

end

//上面这一部分就是对上面的task模块进行调用和对输入信号进行仿真,当然这一部分并没有用到用 //户输入信号。

endmodule

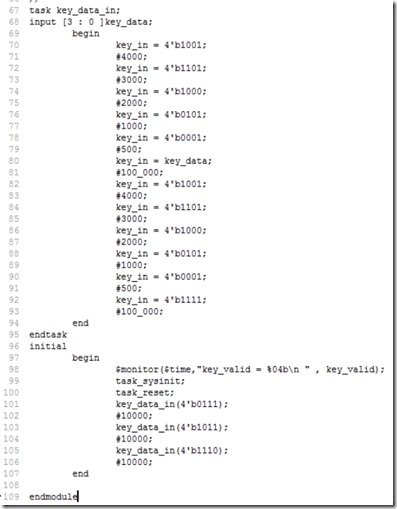

图8.5是对于按键的仿真程序,将输入也定义为一个task,然后在101行到105行进行任务的调用,清楚明了。

图8.5 输入信号的调用

《FPGA全程进阶---实战演练》第八章之程序架构格式说明的更多相关文章

- 《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新<FPGA全程进阶---实战演练&g ...

- 《FPGA全程进阶---实战演练》第四章之实验平台软硬件使用简介

本章主要是讲解读者在进行FPGA逻辑设计之前的准备工作,需要下载Quartus II软件和 Modelsim 软件,一个是用来进行FPGA逻辑设计,一个是用来对逻辑进行理论分析与验证. 1.1 qua ...

- 《FPGA全程进阶---实战演练》第十二章 二进制码与格雷码PK

大家在写程序的时候,可能会听闻,什么独热码,什么格雷码,什么二进制码等等,本节意在解释这几种编码之间的区别和优势以及用verilog怎么去实现,下面先介绍这几种编码的区别. 1 基础理论部分 1.1 ...

- 《FPGA全程进阶---实战演练》第二章之焊接板子及调试注意事项

1.若是读者第一次做板子,强烈建议画完PCB板后将PCB图打印出来,然后对照你买的芯片将芯片放置对 应的位置,然后查看所有的封装格式适不适合,否则等你做出板子来后再试,为时晚矣.笔者虽然知道要这么 做 ...

- 《FPGA全程进阶---实战演练》第七章 让按键恢复平静

1基础理论部分 A:“怎么按键按下去之后,结果不正常?”,B:“按键你消抖了吗?”A:“消什么抖,还要消抖?”, B:“先检测按键变化,然后消抖过滤波动信号,最后输出稳定信号”,A:“我好像漏掉了什 ...

- 《FPGA全程进阶---实战演练》第五章 基于74HC595的LED操作

1基础理论部分 1.1分频 分频,是的,这个概念也很重要.分频是指将一单一频率信号的频率降低为原来的1/N,就叫N分频.实现分频的电路或装置称为“分频器”,如把33MHZ的信号2分频得到16.5MHZ ...

- 《FPGA全程进阶---实战演练》第十一章 VGA五彩缤纷

1基础理论部分 VGA(video graphics array)即视频图形阵列,是IBM在1987年随PS/2一起推出的使用模拟信号的一种视频传输标准.VGA相比与现在的视频传输接口来说已经过时,不 ...

- 《FPGA全程进阶---实战演练》第九章 计数器要注意

本小节我们来做一个好玩的事情,就是计数器,还记得在做LED自加实验时我们就曾经提到过关于计数器的相关议题,那么这节我们就来讨论讨论. 探讨一下如下的问题:请用verilog记八个数的写法,分析这个可以 ...

- 《FPGA全程进阶---实战演练》第一章之如何学习FPGA

对于很多初学者,大部分都是急于求成,熟不知越是急于求成,最终越是学无所成,到头来两手空空,要学好FPGA,必须弄懂FPGA本质的一些内容. 1.FPGA内部结构及基本原理 FPGA是可以编程的,必须通 ...

随机推荐

- 【Unity】第10章 Mecanim动画系统

分类:Unity.C#.VS2015 创建日期:2016-05-02 一.简介 Unity提供了两种动画系统:一种是早期版本提供的旧版(Legacy)动画系统,旧版本(Legacy)以后将逐步被淘汰掉 ...

- 【Unity】9.3 粒子系统生成器详解

分类:Unity.C#.VS2015 创建日期:2016-05-02 一.简介 上一节已经介绍过了在Unity 5.x中两种创建粒子效果的方式(方式1.方式2). 这一节我们主要学习第2种方式的基本概 ...

- 如何将git本地创建的项目推送到github仓库

除了集中式的版本控制系统CVS和SVN外,还有目前世界上最先进的分布式版本控制系统Git,它的创始人是创建了linux的大神 - linus.GitHub网站与2008年开始服役,为开源项目免费提供G ...

- [Windows Azure] Create a Virtual Network in Windows Azure

Create a Virtual Network in Windows Azure This tutorial walks you through the steps to create a basi ...

- [Windows Azure] How to use the Table Storage Service

How to use the Table Storage Service version 1.7 version 2.0 This guide will show you how to perform ...

- 【Android】输入设备配置文件(.idc文件)

何为idc idc(Input Device Configuration)为输入设备配置文件,它包含设备具体的配置属性,这些属性影响输入设备的行为. 对于touch screen设备,总是需要一个id ...

- vue中创建全局单文件组件/命令

1.在 vue中如果我们使用基于vue.js编写的插件,我们可以使用Vue.use() 如在main.js中: 2.添加全局命令,让每个vue单文件组件都可以使用到: 第一步:最好建一个全局的命令文件 ...

- LeetCode: Balanced Binary Tree 解题报告

Balanced Binary Tree Given a binary tree, determine if it is height-balanced. For this problem, a he ...

- 2. EM算法-原理详解

1. EM算法-数学基础 2. EM算法-原理详解 3. EM算法-高斯混合模型GMM 4. EM算法-高斯混合模型GMM详细代码实现 5. EM算法-高斯混合模型GMM+Lasso 1. 前言 概率 ...

- oc调javascript方法(evaluateJavaScript:)&&js给oc发通知

在ios8中引入了WKWebView控件,通过在头文件引用 #import <WebKit/WebKit.h>来使用该控件, 这个控件与oc的原生控件uiwebview很相似,它更方便oc ...