Verilog HDL组合电路的行为级建模

主要使用关键词initial或always定义的两种结构类型的描述语句,initial主要用于面向仿真的过程语句,不能用来描述硬件逻辑电路的功能。

1.always结构型说明语句

用法:

always @(事件控制表达式)

begin:块名

块内局部变量的定义;

一条或者多条过程赋值语句;

end

不停的循环执行其内部的过程赋值语句,直到仿真过程结束。always语句主要对硬件电路的行为功能进行描述,也可以再测试模块中对时钟信号进行描述。

其中“事件控制表达式”又叫敏感事件表,只要里边的某一条件发生改变,则执行always语句,“过程赋值语句”的左值必须是reg(连续赋值语句assign左值必须是wire类型),右边没有要求。

begin与end包起来就是一个块,里边的语句按顺序执行,其实就相当于C语言的{} 。

在always与initial中定义新变量时,begin后必须要加冒号加块名,否则报错,不定义新变量加上块名也是好习惯。

例子:2线-4线译码器。

module Decoder2x4_gates(

input [1:0]A,

input En,

output [3:0]Y);

always @ (A or En) //input与output如果不声明就默认是wire。

begin:Decoder

Y[0] = ~(~A[1] & ~A[0] & En);

Y[1] = ~(~A[1] & A[0] & En);

Y[2] = ~(A[1] & ~A[0] & En);

Y[3] = ~(A[1] & A[0] & En);

end

endmodule

2.条件语句

其实与C语言用法一样,如果是多条语句就记得加begin,end,相当于C语言用{}包起来。

3.多路分支语句

case,但语法不同。

用法:

case(case_expr)

item_expr1: statement1;

item_expr2: statement2;

......

default:default_statement;

endcase

如果是多条语句,还是要加begin,end,如果判断到与某一分支值相同,那么case语句直接执行结束。

case还有两种变体,casez与casex,casez语句中,将z视为无关值,即如果比较双方有一方的有一位的值是z,那么该位不予考虑,比较结果永远为真;casex就是把z和x全视为无关值,都不考虑,比较结果永远为真。

5.循环语句

for、repeat、while和forever,里边可以包含延时控制。只能在initial或always内部使用。多条语句依然要使用begin与end包起来。

(1)for循环语句

用法:

for (表达式1;条件表达式2;表达式3) 语句块

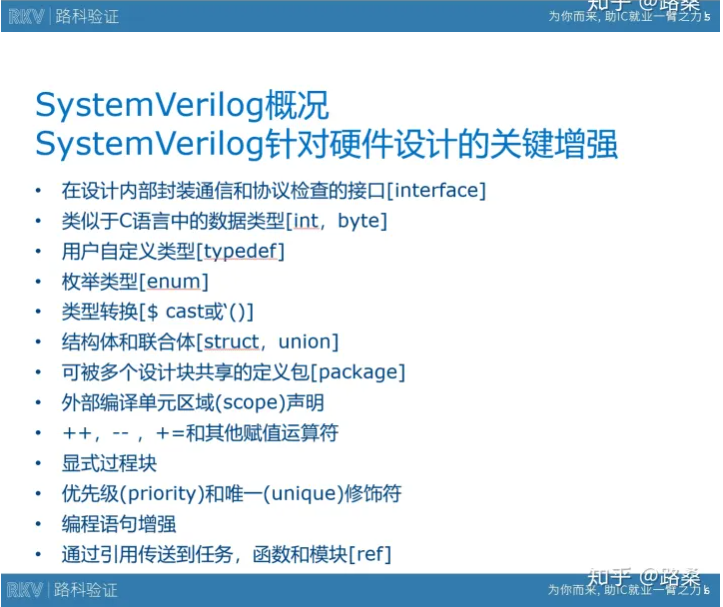

与C语言类型,关于表达式3,verilog是没有自增自减运算符的,所以只能写i = i + 1或者i = i - 1之类的,但是SystemVerilog中支持了++与--。

图引用自什么场合下会用到systemverilog? - 路桑的回答 - 知乎。

其实verilog与SystemVerilog就像是C与C++的区别,能被大多数综合综合语句支持,也能用于仿真测试,下边其他三条基本用于仿真测试了。

(2)while循环

与C语言相同,主要用于仿真测试。

(3)repeat循环语句

用法:

repeat(循环次数表达式)语句块

可以指定循环次数,如果循环次数表达式值不确定,按x与z处理,则循环次数按0处理,主要用于仿真测试。

(4)forever循环语句

无限循环,如果不使用某种形式的时序控制,就无限执行,后边的语句永远不会被执行。

initial

begin

CP = 1'b1;

#50 forever

#25 CP=~CP;

end

上边例子的含义就是,CP在0时刻初始化为1,一直保持到第50个时间单位。然后以后每25个ns,CP反相一次,直到300ns,这个语句主要用于仿真测试。

Verilog HDL组合电路的行为级建模的更多相关文章

- 【转】Verilog HDL常用建模方式——《Verilog与数字ASIC设计基础》读书笔记(四)

Verilog HDL常用建模方式——<Verilog与数字ASIC设计基础>读书笔记(四) Verilog HDL的基本功能之一是描述可综合的硬件逻辑电路.所谓综合(Synthesis) ...

- Verilog门级建模

门级建模就是将逻辑电路图用HDL规定的文本语言表示出来,即调用Verilog语言中内置的基本门级元件描述逻辑图中的元件以及元件之间的连接关系. Verilog语言内置了12个基本门级元件模型,如下表所 ...

- 【黑金教程笔记之003】【建模篇】akuei2的Verilog hdl心路

Verilog hdl不是“编程”是“建模” Verilog hdl语言是一种富有“形状”的语言. 如果着手以“建模”去理解Verilog hdl语言,以“形状”去完成Verilog hdl语言的设计 ...

- Verilog HDL的程序结构及其描述

这篇博文是写给要入门Verilog HDL及其初学者的,也算是我对Verilog HDL学习的一个总结,主要是Verilog HDL的程序结构及其描述,如果有错,欢迎评论指出. 一.Verilog ...

- 自己动手写处理器之第二阶段(2)——Verilog HDL简单介绍

将陆续上传本人写的新书<自己动手写处理器>(尚未出版),今天是第六篇.我尽量每周四篇 2.3 Verilog HDL简单介绍 本书实现的OpenMIPS处理器是使用Verilog HDL编 ...

- Verilog HDL设计规范及经验谈(转载)

1. 规范很重要 工作过的朋友肯定知道,公司里是很强调规范的,特别是对于大的设计(无论软件还是硬件),不按照规范走几乎是不可实现的.逻辑设计也是这样:如果不按规范做的话,过一个月后调试时发现 ...

- 写自己的第二级处理器(3)——Verilog HDL行为语句

我们会继续上传新书<自己动手写处理器>(未公布),今天是第七章,我每星期试试4 2.6 Verilog HDL行为语句 2.6.1 过程语句 Verilog定义的模块一般包含有过程语句,过 ...

- 关于Verilog HDL的一些技巧、易错、易忘点(不定期更新)

本文记录一些关于Verilog HDL的一些技巧.易错.易忘点等(主要是语法上),一方面是方便自己忘记语法时进行查阅翻看,另一方面是分享给大家,如果有错的话,希望大家能够评论指出. 关键词: ·技巧篇 ...

- verilog HDL -模块代码基本结构

1--verilog HDL 语言的预编译指令作用:指示在编译verliog HDL源代码前,需要执行哪些操作. 2--模块内容是嵌在module 和endmodule两个语句之间.每个模块实现特定的 ...

- 【Verilog HDL】赋值语句之阻塞赋值方式与非阻塞赋值方式

刚开始接触Verilog HDL语言时,这种硬件描述语言有一点与软件的程序设计语言直观上的最大区别大概就是这个赋值语句了(这里只是强调直观上的最大区别,事实上的最大区别并非如此). Verilog H ...

随机推荐

- quarkus依赖注入之二:bean的作用域

欢迎访问我的GitHub 这里分类和汇总了欣宸的全部原创(含配套源码):https://github.com/zq2599/blog_demos 关于bean的作用域(scope) 官方资料:http ...

- 微服务项目使用RabbitMQ

微服务项目使用RabbitMQ 很久未用RabbitMQ了,根据网上的Demo,大多数是一个服务包含所有的生产者和消费者和配置,当自己去搭建服务的时候,还需要一些思考各种包的划分.无法无脑CV大法,所 ...

- C++欧几里得算法求最大公约数和最小公倍数

定义 最大公约数即为 Greatest Common Divisor,常缩写为 gcd. 一组整数的公约数,是指同时是这组数中每一个数的约数的数. 一组整数的最大公约数,是指所有公约数里面最大的一个. ...

- ctfshow--web入门--XXE

ctfshow--web入门--XXE web373 源码 <?php error_reporting(0); libxml_disable_entity_loader(false); //允许 ...

- 微信小程序预览时显示有图片未上传

最近在做小程序项目,在项目里面加了几个图片.在预览调试时出现弹窗显示"文件未上传",但是在左侧的模拟器上却是能正常显示的. 解决思路: 图片在本地和模拟器上显示正常,表示图片本身没 ...

- 《Kali渗透基础》15. WEB 渗透

@ 目录 1:WEB 技术 1.1:WEB 攻击面 1.2:HTTP 协议基础 1.3:AJAX 1.4:WEB Service 2:扫描工具 2.1:HTTrack 2.2:Nikto 2.3:Sk ...

- DAY005_异或运算

运算规则 二进制:相同为0 相异为1 十进制:相同为0 任何数字和0异或都是它本身 不利用额外变量交换两个数 数组中一种数字出现了奇数次,其他数都出现了偶数次,怎么得到这个出现了奇数次的数 将所有的数 ...

- Dubbo3应用开发——架构的演变过程

Dubbo3应用开发--架构的演变过程 什么是Dubbo 早期Dubbo的定位: 基于Java的高性能,轻量级的RPC框架:SOA[Service-Oriented Architecture ⾯向服务 ...

- 前端远程调试方案 Chii 的使用经验分享

前端远程调试方案 Chii 的使用经验分享 Chii 是与 weinre 一样的远程调试工具 ,主要是将 web inspector 替换为最新的 chrome devtools frontend 监 ...

- 织梦DEDEBIZ调用全站文章数量

织梦DEDEBIZ如何调用全站文章数量{dede:sql sql="select count(*) as c from biz_archives} 共有文章:[field:c/] 篇 {/d ...