VHDL之concurrent之operators

Using operators

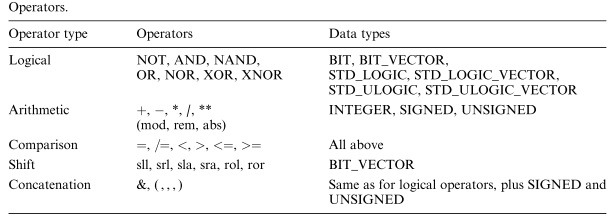

Operators can be used to implement any combinational circuit. However, as will become apparent later, complex circuits are usually easier to write using sequential code, even if the circuit does not contain sequential logic.

Example Multiplexer

---------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

---------------------------------------

ENTITY mux IS

PORT ( a, b, c, d, s0, s1: IN STD_LOGIC;

y: OUT STD_LOGIC);

END mux;

---------------------------------------

ARCHITECTURE pure_logic OF mux IS

BEGIN

y <= (a AND NOT s1 AND NOT s0) OR

(b AND NOT s1 AND s0) OR

(c AND s1 AND NOT s0) OR

(d AND s1 AND s0);

END pure_logic;

---------------------------------------

Miscellaneous operators

** Exponentiation

abs Absolute value

The exponentiation operator has two operands. This operator is defined for any integer or floating point number. The right operand (exponent) must be of integer type. When the exponent is the positive integer, then the left operand is repeatedly multiplied by itself. When the exponent is the negative number, then the result is a reverse of exponentiation with the exponent equal to the absolute value of the right operand. If the exponent is equal to 0 the result will be 1.

The abs operator has only one operand. It allows defining the operand's absolute value. The result is of the same type as the operand.

2 ** =

3.8 ** = 54.872

** (-) = / (**) = 0.0625

VHDL之concurrent之operators的更多相关文章

- VHDL之concurrent之generate

GENERATE It is another concurrent statement (along with operators and WHEN). It is equivalent to the ...

- VHDL之concurrent之when

WHEN (simple and selected) It is one of the fundamental concurrent statements (along with operators ...

- VHDL之concurrent之block

1 Simple BLOCK The simple block represents only a way of partitioning the code. It allows concurrent ...

- Concurrent.Thread.js

(function(){ if ( !this.Data || (typeof this.Data != 'object' && typeof this.Data != 'functi ...

- how to forget about delta cycles for RTL design

A delta cycle is a VHDL construct used to makeVHDL, a concurrent language, executable on asequential ...

- VHDL基础1

Description Structure 一个可综合的VHDL描述中一般由3部分组成:LIBRARY declarations.ENTITY.ARCHITECTURE Library(库)用来设计重 ...

- ConCurrent in Practice小记 (3)

ConCurrent in Practice小记 (3) 高级同步技巧 Semaphore Semaphore信号量,据说是Dijkstra大神发明的.内部维护一个许可集(Permits Set),用 ...

- ConCurrent in Practice小记 (2)

Java-ConCurrent2.html :first-child{margin-top:0!important}img.plugin{box-shadow:0 1px 3px rgba(0,0,0 ...

- 让WPS支持VHDL的关键词加粗

WPS的VBA在这里下载:http://bbs.wps.cn/forum.php?mod=viewthread&tid=22347925 语法高亮是参考Word的,这篇文章:http://bl ...

随机推荐

- gitblit 搭建本地git服务器

本文主要描述gitblit搭建本地服务器

- 【模板】可持久化Treap

洛谷3835 #include<cstdio> #include<algorithm> #include<cstdlib> #define ls (a[u].l) ...

- ssm 数据库连接池配置

1.工程引入druid-1.1.2.jar包2.修改spring-common.xml文件 <!-- 1. 数据源 : DruidDataSource--> <bean id=&qu ...

- javascript 闭包笔记

先来解释一下闭包: 1.闭包就是函数嵌套函数 2.内部函数可以引用外部函数的参数和变量 3.参数和变量不会被垃圾回收机制所收回( 垃圾回收机制就是用完变量之后就在内存中释放 ) 使用闭包的好处: ...

- time库

简介 返回系统当前时间戳(正常的生活时间) 返回格林威治时间戳对应的struct_time对象 本地时间的struct_time对象 当前时间戳对应的易读格式字符串时间(周几,月份,号数,时,分,秒, ...

- UVa - 11452 - Dancing the Cheeky-Cheeky

先上题目: F. Dancing the Cheeky-Cheeky Context The Cheeky-Cheeky is a new song. They dance it in Mula, ...

- 网页title上面添加图片

1.效果:

- http-runtime属性

配置httpRuntime也可以让FileUpload上传更大的文件,不过设置太大了会因用户将大量文件传递到该服务器而导致的拒绝服务攻击(属性有说明) 属性 属性 选项 说明 appRequestQu ...

- Machine_learning--score

辛苦了2个半月,终须学完了machine-learning watermark/2/text/aHR0cDovL2Jsb2cuY3Nkbi5uZXQvY2hyaXN0cHJpbmNlMDA3/font ...

- Effective Java:对于全部对象都通用的方法

前言: 读这本书第1条规则的时候就感觉到这是一本非常好的书.可以把我们的Java功底提升一个档次,我还是比較推荐的.这里我主要就关于覆盖equals.hashCode和toString方法来做一个笔记 ...