FPGA驱动VGA显示静态图片

一 、前言

本文设计思想采用明德扬至简设计法。VGA是最常见的视频显示接口,时序也较为简单。本文从利用显示屏通过VGA方式显示测试图案及静态图片着手带大家接触图像显示应用,算是为后续VGA显示摄像头采集图像以及HDMI高清数字显示方式打个基础。

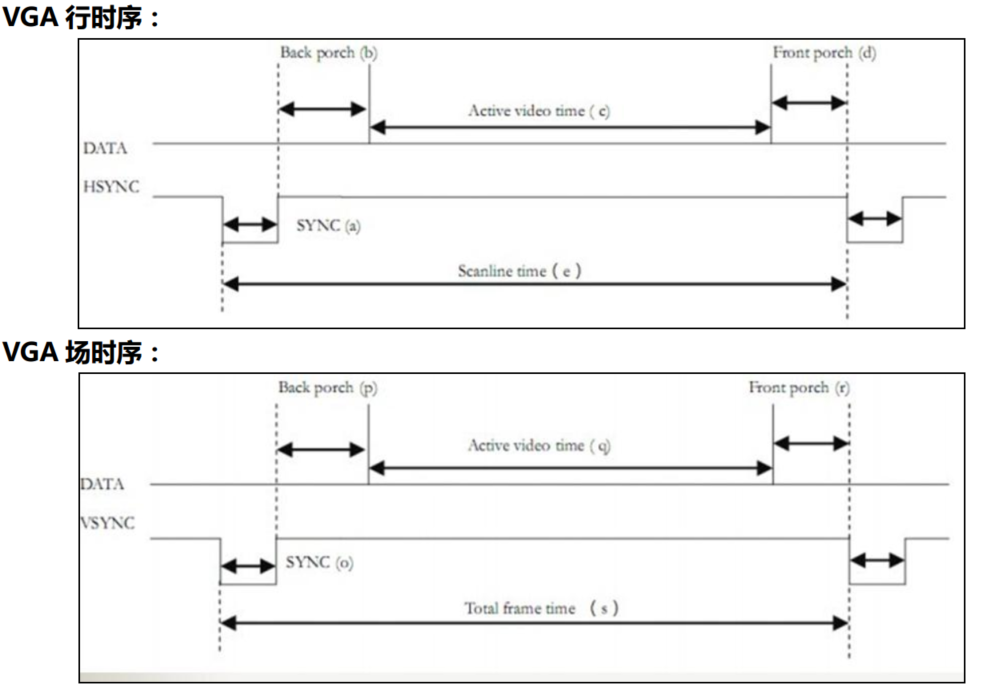

二、VGA显示原理

关于VGA的详细解释可查看参考文献1,这里主要讲解下根据VGA的分辨率计算时钟频率的方式。以本文使用到的1024*768@60HZ为例。

一帧图像显示周期为Tv,在这段时间内VGA需要扫描806行,每行1344个点。所以每个点的持续周期为:Ts=Tv/(n*m),故时钟频率:fs = n*m*fv=806*1344*60=65MHz。因此设计下来其实非常简单,PLL产生65MHz工作时钟信号,利用两个计数器分别计数行列值,之后根据计数器数值产生行场同步信号以及相应的RGB图像数据即可。有一点需要注意:VGA显示标准规定行场同步脉冲均为负脉冲,意思是只有同步脉冲阶段拉低,其他时刻为高电平。

三、静态图片显示

VGA显示基本原理和设计方式确定后,显示图片也不是什么难事。可以将图片以.coe形式保存在FPGA内部BRAM中,通过VGA接口模块循环读取RAM数据方式来显示图片。FPGA片内BRAM的存储容量一般在kbit量级,存储640*480*24bit真彩色图像捉襟见肘,因此这里仅显示320*240*16bit图像用于测试。把图片格式设定为.coe文件的方法:一是可以利用些小的软件工具,此处先用img2Lcd软件将图片调整为合适的分辨率,再用BMP2Mif软件生成.coe文件初始化BMG IP核(见参考文献2);第二就是自己写一段软件脚本来转换。

测试需求:VGA接口以1024*768分辨率,60Hz帧频,在显示屏中央位置显示一幅320*240图片,其他位置左右各一半分别显示白色和红色。

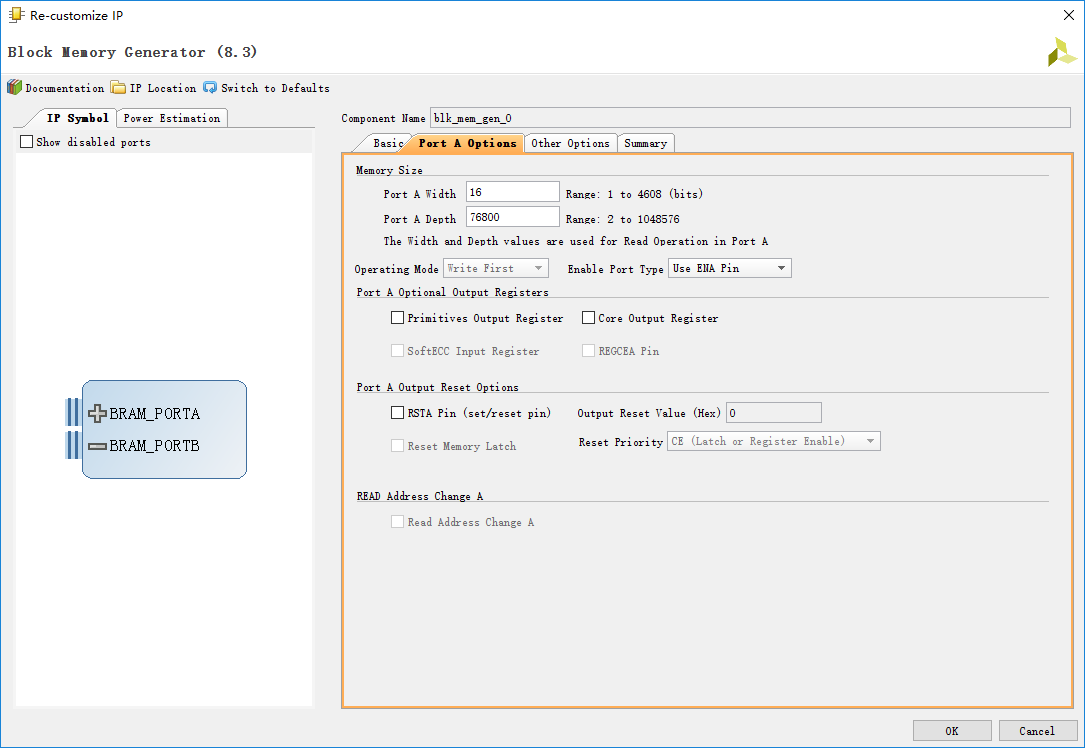

BMG IP核配置:

第一页选择单口ROM模式,其他保持默认。主要第二页的位宽和深度设置正确,另外取消掉输出寄存器选择匹配时序。

四、显示硬件方案

大多数VGA显示采用电阻网络分压代替DA过程,这种方案成本较低,能满足大多数显示需求。当对分辨率要求较高时,采用专用显示芯片来完成R G B三路同步数模转换,本文采用ADI公司的ADV7123芯片,内含有三路10位DAC,最高支持1080p@60Hz图像输出。硬件中将每路低两位拉低,仅提供高8位接口可满足8*8*8 = 24bit真彩色显示需求。上升沿采样数据,为方便处理和代码规范,FPGA逻辑在PLL时钟上升沿驱动,输出显示芯片工作采样时钟为PLL产生时钟信号取反,如此可保证满足显示芯片建立保持时间需求。

五、逻辑代码设计

VGA显示接口代码如下:

`timescale 1ns / 1ps module vga_interface#(

parameter DATA_W = )

(

input clk,//65MHz

input rst_n, output vga_clk,

output reg vga_en, //input [DATA_W-1:0] din_r,

//input [DATA_W-1:0] din_g,

//input [DATA_W-1:0] din_b,

output [DATA_W-:] vga_r,

output [DATA_W-:] vga_g,

output [DATA_W-:] vga_b,

output reg vga_hs,

output reg vga_vs

); /*********************************参数******************************************/

//VGA:1280*768@60HZ

//行参数

localparam H_A = , //同步脉冲

H_B = , //显示后沿

H_C = , //显示时段

H_D = ; //显示前沿

//场参数

localparam V_A = , //同步脉冲

V_B = , //显示后沿

V_C = , //显示时段

V_D = ; //显示前沿 //有效区域边界

localparam X0 = H_A+H_B, //136+160=296

X1 = H_A+H_B+H_C, //136+160+1024=1320

Y0 = V_A+V_B, //6+29=35

Y1 = V_A+V_B+V_C; //6+29+768=803 localparam COL_NUM = H_A+H_B+H_C+H_D,//

ROW_NUM = V_A+V_B+V_C+V_D;//806 //显示中心位置

localparam X_CENTER = (X0+X1)/,//

Y_CENTER = (Y0+Y1)/;//419 //显示图片分辨率及位置

localparam PIC_H = ,

PIC_V = ; localparam PIC_H_LB = X_CENTER-PIC_H/,

PIC_H_RB = X_CENTER+PIC_H/,

PIC_V_UB = Y_CENTER-PIC_V/,

PIC_V_DB = Y_CENTER+PIC_V/; /*********************************信号定义******************************************/

reg [ (-):] cnt_hs ;

wire add_cnt_hs ;

wire end_cnt_hs ;

reg [ (-):] cnt_vs ;

wire add_cnt_vs ;

wire end_cnt_vs ;

wire valid_area;

wire left_half;

wire picture_area;

reg [DATA_W-:] r_reg,g_reg,b_reg; wire ena;

wire [:] douta;

reg [ (-):] cnt_addr ;

wire add_cnt_addr ;

wire end_cnt_addr ;

wire [:] addra;

reg ram_vld;

/*********************************计数器******************************************/ always @(posedge clk or negedge rst_n) begin

if (rst_n==) begin

cnt_hs <= ;

end

else if(add_cnt_hs) begin

if(end_cnt_hs)

cnt_hs <= ;

else

cnt_hs <= cnt_hs+ ;

end

end assign add_cnt_hs = ;

assign end_cnt_hs = add_cnt_hs && cnt_hs == (COL_NUM)- ; always @(posedge clk or negedge rst_n) begin

if (rst_n==) begin

cnt_vs <= ;

end

else if(add_cnt_vs) begin

if(end_cnt_vs)

cnt_vs <= ;

else

cnt_vs <= cnt_vs+ ;

end

end

assign add_cnt_vs = (end_cnt_hs);

assign end_cnt_vs = add_cnt_vs && cnt_vs == (ROW_NUM)- ; /*********************************BRAM相关信号******************************************/

//BRAM读取地址计数器

always @(posedge clk or negedge rst_n) begin

if (rst_n==) begin

cnt_addr <= ;

end

else if(add_cnt_addr) begin

if(end_cnt_addr)

cnt_addr <= ;

else

cnt_addr <= cnt_addr+ ;

end

end assign add_cnt_addr = (ena);

assign end_cnt_addr = add_cnt_addr && cnt_addr == * - ; assign addra = cnt_addr;

assign ena = picture_area; //BRAM数据有效指示

always @(posedge clk or negedge rst_n)begin

if(rst_n=='b0)begin

ram_vld <= ;

end

else begin

ram_vld <= ena;

end

end

/*********************************VGA输出信号******************************************/

//行场同步信号

always @(posedge clk or negedge rst_n)begin

if(rst_n=='b0)begin

vga_hs <= ;

end

else if(add_cnt_hs && cnt_hs == H_A-)begin

vga_hs <= ;

end

else if(end_cnt_hs)

vga_hs <= ;

end always @(posedge clk or negedge rst_n)begin

if(rst_n=='b0)begin

vga_vs <= ;

end

else if(add_cnt_vs && cnt_vs == V_A-)begin

vga_vs <= ;

end

else if(end_cnt_vs)

vga_vs <= ;

end //R G B寄存器信号

always @(posedge clk or negedge rst_n)begin

if(rst_n=='b0)begin

r_reg <= ;

g_reg <= ;

b_reg <= ;

end

else if(valid_area && !picture_area)begin

if(left_half)begin //彩条测试 左半屏幕显示白色

r_reg <= 'b1111_1111;

g_reg <= 'b1111_1111;

b_reg <= 'b1111_1111;

end

else begin //右半屏幕显示红色

r_reg <= 'b1111_1111;

g_reg <= ;

b_reg <= ;

end

end

else begin//无效区域显示黑色

r_reg <= ;

g_reg <= ;

b_reg <= ;

end

end assign valid_area = cnt_hs >= X0 && cnt_hs < X1 && cnt_vs >= Y0 && cnt_vs < Y1;

assign left_half = cnt_hs >= X0 && cnt_hs < X_CENTER;

assign picture_area = cnt_hs >= PIC_H_LB && cnt_hs < PIC_H_RB

&& cnt_vs >= PIC_V_UB && cnt_vs < PIC_V_DB; assign vga_r = ram_vld ? {douta[:],'b0} : r_reg;//5bit

assign vga_g = ram_vld ? {douta[:],'b0} : g_reg;//6bit

assign vga_b = ram_vld ? {douta[:],'b0} : b_reg;//5bit //输出控制信号

assign vga_clk = ~clk; always @(posedge clk or negedge rst_n)begin

if(rst_n=='b0)begin

vga_en <= ;

end

else if(valid_area)begin

vga_en <= ;

end

else

vga_en <= ;

end /*********************************子模块例化 BRAM******************************************/ blk_mem_gen_0 bram (

.clka(clk), // input wire clka

.ena(ena), // input wire ena

.addra(addra), // input wire [16 : 0] addra

.douta(douta) // output wire [15 : 0] douta

); endmodule

vga_driver

这里VGA接口代码包含了显示内容,在实际应用中要去掉显示部分逻辑和BRAM的例化,添加用户侧接口及逻辑。测试工程顶层:

`timescale 1ns / 1ps module vga_test_top(

input sys_clk_p,

input sys_clk_n,

input rst_n, output vga_hs,

output vga_vs,

output vga_clk,

output vga_en,

output [-:] vga_r,

output [-:] vga_g,

output [-:] vga_b

); wire clk;

wire sys_clk_ibufg;

wire locked; IBUFGDS #

(

.DIFF_TERM ("FALSE"),

.IBUF_LOW_PWR ("FALSE")

)

u_ibufg_sys_clk

(

.I (sys_clk_p),

.IB (sys_clk_n),

.O (sys_clk_ibufg)

); clk_wiz_0 pll

(

// Clock out ports

.clk_out1(clk), // output clk_out1

// Status and control signals

.resetn(rst_n), // input resetn

.locked(locked), // output locked

// Clock in ports

.clk_in1(sys_clk_ibufg)); // input clk_in1 vga_interface#(.DATA_W())

vga_interface

(

.clk (clk) ,//65MHz

.rst_n (rst_n) ,

.vga_clk (vga_clk) ,

.vga_en (vga_en) ,

.vga_r (vga_r) ,

.vga_g (vga_g) ,

.vga_b (vga_b) ,

.vga_hs (vga_hs) ,

.vga_vs (vga_vs)

); endmodule

vga_test_top.v

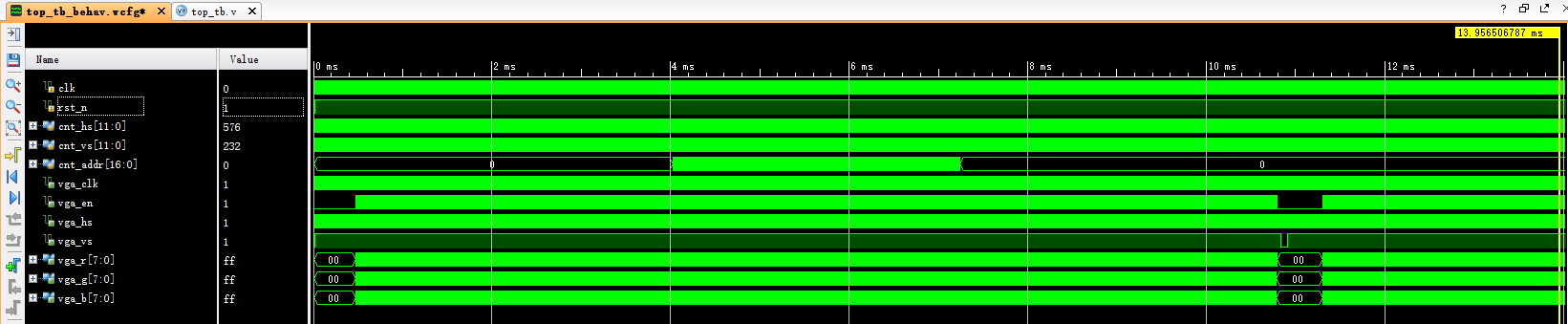

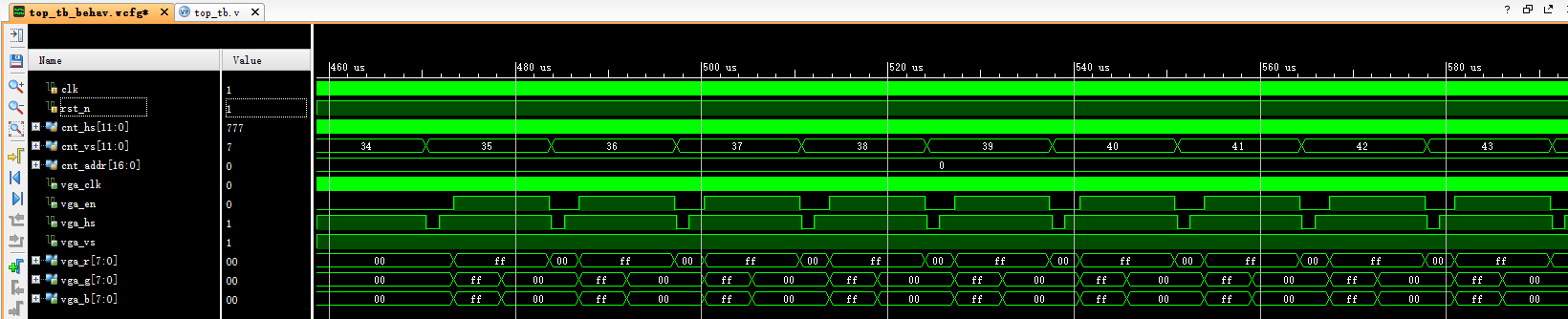

六、仿真及板级测试

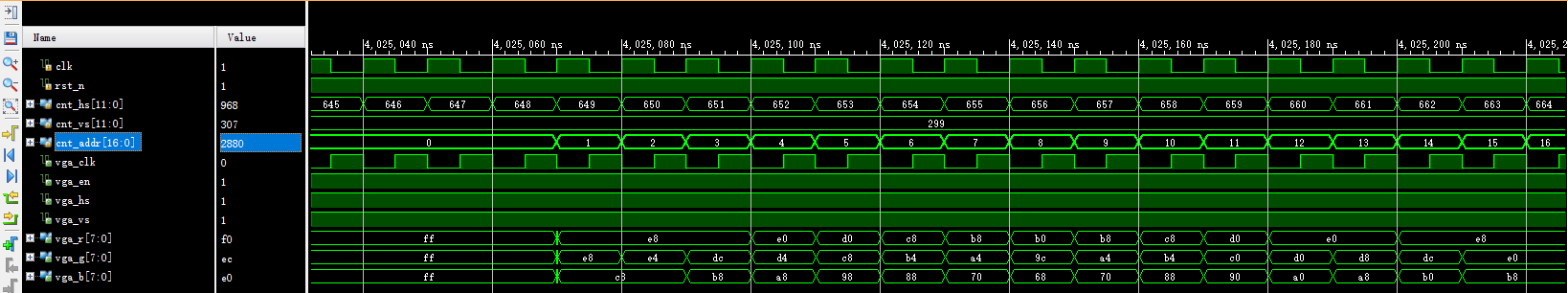

为了方便仿真,只将vga_interface作为uut。查看行为仿真波形:

可见行场计数器及同步脉冲按照预期工作,在显示图片区域地址计数器递增。现在我们看看实际上板后的显示效果:

和原始图片对比下

由于原始图片是24位真彩图,且在VGA显示接口模块中进行了R G B低位填充导致些许失真,不过整体显示正确。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

参考文献:

1 [笔记]VGA时序及其原理 - LiangXuan - 博客园 https://www.cnblogs.com/spartan/archive/2011/08/16/2140546.html

2 【原创】bmp转mif、coe或hex软件发布及使用介绍-crazybird-电子技术应用-AET-北大中文核心期刊-最丰富的电子设计资源平台 http://blog.chinaaet.com/crazybird/p/5100000224

FPGA驱动VGA显示静态图片的更多相关文章

- 基于FPGA的VGA显示静态图片

终于熬到暑假了,记过三四周的突击带考试,终于为我的大二画上了一个完整的句号,接下来终于可以静心去做自己想做的事情了,前一阵子报了一个线上培训班,学学Sobel边缘检测,之前一直在学习图像处理,但是因为 ...

- 基于FPGA驱动VGA显示图片的小问题

学习VGA显示图片的过程中,遇到了一个小问题,我在显示屏上开了一个60x60的框,放了一张图片进去显示,但是最终的结果如下图所示. 出现了一个竖黑边,看了看代码,分析了一下逻辑没问题,然而看这个显示那 ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

- 基于FPGA的VGA显示实验设计

基于FPGA的VGA显示实验设计 成果展示(优酷视频): 视频: 基于FPGA的VGA显示技术(手机控制) http://v.youku.com/v_show/id_XNjk4ODE3ODUy.htm ...

- mfc显示静态图片最简单的方法

一致都是研究如何调用opencv显示动态图片,但是很多时候在显示图标的时候,都是需要显示静态图片,现在将最简单的方法总结下: 1.添加picture控件 2.添加资源,要求为bmp 3.修改属性 结果 ...

- Android 加载gif图片强大框架(支持预加载、缓存,还支持显示静态图片,一行代码全搞定)

之前项目中没有涉及到显示gif图片的功能,也没有着重研究过,最近项目中要用到显示gif图片,于是就在网上一顿搜,用过之后发现如下几个缺点. 1.加载大的gif图片会出现oom. 2.没有预加载和缓存功 ...

- 基于FPGA的VGA显示设计(一)

前言 FPGA主要运用于芯片验证.通信.图像处理.显示VGA接口的显示器是最基本的要求了. 原理 首先需要了解 : (1)VGA接口协议:VGA端子_维基百科 .VGA视频传输标准_百度 引脚1 RE ...

- FPGA驱动LCD显示红绿蓝彩条

实验目的:先简单熟悉LCD灯的驱动和时序图的代码实现.设计功能是让LCD显示红绿蓝三种颜色,即三个彩带.本次实验比较容易实现,主要是对LCD驱动时序图的理解和时序参数的配置. 实验条件:1.LCD原理 ...

- MFC入门--显示静态图片及调用本地软件

MFC是微软开发的基础类库,主要用来开发图形界面应用程序,在学习中,我们要验证算法好坏,一般需要对结果进行可视化. OpenCV是计算机视觉中的开源算法库,集成了很多先进算法,现在想将MFC与Open ...

随机推荐

- linux系统安装cdcfordb2udb

最近接触到db2数据库实时复制的解决方案InfoSphere CDC(Change Database Capture) .主要是通过读取源端的日志信息对目标端进行数据的增删改,从而尽量减少对源端资源的 ...

- 【Spark篇】---Spark中Shuffle机制,SparkShuffle和SortShuffle

一.前述 Spark中Shuffle的机制可以分为HashShuffle,SortShuffle. SparkShuffle概念 reduceByKey会将上一个RDD中的每一个key对应的所有val ...

- .NET Core实战项目之CMS 第十五章 各层联动工作实现增删改查业务

连着两天更新叙述性的文章大家可别以为我转行了!哈哈!今天就继续讲讲我们的.NET Core实战项目之CMS系统的教程吧!这个系列教程拖得太久了,所以今天我就以菜单部分的增删改查为例来讲述下我的项目分层 ...

- java多线程(6)---ThreadLocal

ThreadLocal 什么是ThreadLocal? 顾名思义它是local variable(线程局部变量).它的功用非常简单,就是为每一个使用该变量的线程都提供一个变量值的副本,是每一个线程都可 ...

- H5本地存储sessionStorage和localStorage的区别

sessionStorage用于本地存储一个会话(session)中的数据,这些数据只有在同一个会话中的页面才能访问并且当会话结束后数据也随之销毁.因此sessionStorage不是一种持久化的本地 ...

- IdentityServer4之Client Credentials(客户端凭据许可)

IdentityServer4之Client Credentials(客户端凭据许可) 参考 项目创建:0_overview,1_client_credentials 概念:客户端凭据许可 认证服务端 ...

- C++版 - Lintcode 77-Longest Common Subsequence最长公共子序列(LCS) - 题解

版权声明:本文为博主Bravo Yeung(知乎UserName同名)的原创文章,欲转载请先私信获博主允许,转载时请附上网址 http://blog.csdn.net/lzuacm. C++版 - L ...

- Chapter 4 Invitations——19

After I hung up, I tried to concentrate on dinner — dicing the chicken especially; I didn't want to ...

- Java开发知识之Java的枚举

Java开发知识之Java的枚举 一丶什么是枚举 枚举可以理解为就是常量,在Java中我们定义常量.都是用 final语句. C++中都是用const关键字. 枚举跟C++概念都是一样的.就是特定的常 ...

- SmartSql = Dapper + MyBatis + Cache(Memory | Redis) + ZooKeeper + R/W Splitting + ......

SmartSql Why 拥抱 跨平台 DotNet Core,是时候了. 高性能.高生产力,超轻量级的ORM.156kb (Dapper:168kb) So SmartSql TargetFrame ...