《FPGA全程进阶---实战演练》第二章之硬件平台的搭建

学习FPGA,多多少少应该要懂得硬件电路的设计,这样不单单增加了自己的技能,而且还能够对FPGA的硬件实现有更好的了解。

1 模块划分

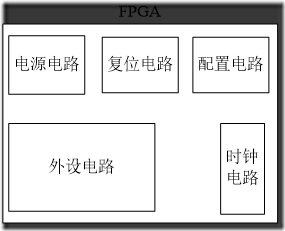

对于一个基本的FPGA硬件平台,常用的几个电路部分:(1)电源电路;(2)复位电路;(3)时钟电路;(4)外设电路;(5)配置电路。如图2.1所示。

图2.1 常用电路模块

1.1电源电路

电源电路是FPGA的核心,是“心脏”,若是电源电路设计的不合理,很可能导致整个系统的溃败,不能正常运行或者失败。对于FPGA来说,基本上包括三类电压:(1)核心电压;(2)I/O电压;(3)辅助电压;

(1) 核心电压是保证FPGA正常工作的基本电压,属于FPGA内部系统电压。

(2) I/O电压是FPGA的I/O引脚工作所需的参考电压。不同bank的I/O所需要的电压不尽相同,对于一些LVDS的I/O电压,可能会需要1.5V,这就不同于LVTTL电平的I/O口。

(3) 除了上述之外的部分的电压,称为辅助电压,例如一些PLL电路的设计等。

需注意以下情况:

(1)器件需要几档电压,电压值分别为多少;

(2)不同档最大电流是多少;

(3)不同档是否有上电要求;

(4)电源的去耦电容如何分配和排布;

(5)电源电压是否需要设计特殊的去耦电路;

(6)个别芯片需要注意接地问题,FPGA的地信号通常是和电压配对的,一般应用中,统一共地是没有问题的。但个别芯片底部中央有个接地焊盘,这个地信号是连接FPGA内部的很多中间信号的地端,它并不和FPGA的其他地信号直接导通,要注意中间接地焊盘。

1.2 时钟电路

FPGA的时钟信号源一般来自外部,在大规模的FPGA内部会带有PLL或DLL等可以对时钟信号进行倍频或分频。由于FPGA内部有大量的寄存器资源,而往往在做逻辑使用时,大量的寄存器会有同一个时钟源,由于时钟到达每一个寄存器所需要的时间不一样,这就导致延迟,若到达寄存器的延迟过大的话,会导致系统混乱,不能正常工作,所以FPGA内部设计了“全局时钟网络”的走线池,通过这种专用走线,可以将同一时钟到达寄存器的时间差控制到最小的范围之内。只需将外部晶振的引脚接到FPGA专用引脚上面即可,EDA软件会自动识别此类信号,并将此信号分配到全局时钟网络上。

需注意以下情况:

(1)系统运行的最高时钟频率是多大;

(2)时钟走线尽可能短,有条件可以做包地处理;

(3)尽可能选择专用的时钟输入引脚;

(4)是否有可用的内部时钟管理模块,(PLL或者DLL,通常是有的)其输入频率是多少(查器件手册,有一个范围);

1.3 配置电路

FPGA芯片的配置是通过JTAG实现在线可编程,当断电时SRAM数据丢失,不能恢复,因此FPGA通常需要外挂一个用于保存当前配置数据流的PROM或Flash芯片,通常称为“配置芯片”。CPLD大多都是基于PROM或Flash来实现可编程特性,对它们进行编程时就已经配置好数据流固化好了,重新上电还能够运行固有的配置数据,CPLD不需要配置芯片。

需注意以下情况:

(1)配置芯片尽量离FPGA近些;

(2)尽量使用官方指定的电路和引脚;

(3)必要时增加阻抗匹配电阻;

1.4复位电路

复位电路的设计,尽量采用专用引脚。FPGA内部大量的寄存器在上电工作之前需要有一个确定的初始状态以确保正常运行。而上电时间对于FPGA的复位来说也至关重要,FPGA是基于SRAM结构,若上电复位时间较短,那么FPGA器件内部很可能没有复位完成,若上电复位时间较长,对于用户交互使用会有一定的影响,所以上电复位时间要确定好。

需注意以下情况:

(1)使用FPGA专用引脚;

(2)上电复位时间要确定;

(3)尽可能选择专用的时钟输入引脚;

《FPGA全程进阶---实战演练》第二章之硬件平台的搭建的更多相关文章

- 《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新<FPGA全程进阶---实战演练&g ...

- 《FPGA全程进阶----实战演练》第二章之系统搭建

1 系统方案 对于设计一款硬件平台,首先要确定整体框架,确定各个模块所需要的芯片以及电压分配情况.图2.6是笔者曾经设计的硬件平台系统. 图2.6系统框图 对于选定一个系统方案之后,接下来做的要先去查 ...

- 《FPGA全程进阶---实战演练》第二十一章 电源常用类型:LDO和 DCDC

高速电路中的电源设计 高速电路中的电源设计大概分为两种,一种是集总式架构,一种是分布式架构.集总式架构就是由一个电源输入,然后生成多种所需要的电压.如图1所示.这种架构会增加多个DC/DC模块,这样成 ...

- 《FPGA全程进阶---实战演练》第二十一章之 几种常用电平分析及特性

TTL,CMOS以及LVTTL,LVCMOS TTL和CMOS是数字电路中两种常见的逻辑电平,LVTTL和LVCMOS是两者低电平版本.TTL是流控器件,输入电阻小,TTL电平器件速度快,驱动能力大, ...

- 《FPGA全程进阶---实战演练》第二十一章 细说低速与高速电路设计之电阻 电容 电感 磁珠

1.1 什么是高速电路 信号的最高频率成分是取决于有效频率,而不是周期频率. 高速电路的定义是根据信号的有效频率来计算的,在现实世界中,任何信号都是由多个频率分量的正弦波叠加而成的.定义各正弦波分 ...

- 《FPGA全程进阶---实战演练》第二章之焊接板子及调试注意事项

1.若是读者第一次做板子,强烈建议画完PCB板后将PCB图打印出来,然后对照你买的芯片将芯片放置对 应的位置,然后查看所有的封装格式适不适合,否则等你做出板子来后再试,为时晚矣.笔者虽然知道要这么 做 ...

- 《FPGA全程进阶---实战演练》第二章之PCB layout注意事项以及投板几点说明

上一篇博客讲述了各个部分的原理图,那么根据原理图画出PCB,其实PCB是一门很大的学问,想要掌握谈何容易.就笔者在画PCB时的一些注意事项做一些说明. 1.电源部分的电源线 ...

- 《FPGA全程进阶---实战演练》第四章之实验平台软硬件使用简介

本章主要是讲解读者在进行FPGA逻辑设计之前的准备工作,需要下载Quartus II软件和 Modelsim 软件,一个是用来进行FPGA逻辑设计,一个是用来对逻辑进行理论分析与验证. 1.1 qua ...

- 《FPGA全程进阶---实战演练》第一章之FPGA介绍

1 什么是FPGA FPGA也即是Field Programmable Gate Array的缩写,翻译成中文就是现场可编程门阵列.FPGA是在PAL.GAL.CPLD等可编程器件的基础上发展起来的新 ...

随机推荐

- ZOJ 1654 Place the Robots建图思维(分块思想)+二分匹配

题目链接:http://acm.zju.edu.cn/onlinejudge/showProblem.do?problemId=654 AC一百道水题,不如AC一道难题来的舒服. 题意:一个n*m地图 ...

- Python isspace() 方法

描述 Python isspace() 方法检测字符串是否只由空格组成. 语法 isspace() 方法语法: S.isspace() 参数 无. 返回值 如果字符串中至少有一个字符,并且所有字符都是 ...

- Java JNI的具体介绍

JNI就是Java Native Interface的简称,也就是java本地接口.它提供了若干的API实现了和Java和其它语言的通信(主要是C&C++).也许不少人认为Java已经足够强大 ...

- 中国计算机学会CCF推荐国际学术期刊会议(最新版)

中国计算机学会推荐国际学术期刊会议 2014年12月,中国计算机学会(CCF)启动新一轮<)计算机体系结构/高性能计算/存储系统: )计算机网络:)网络与信息安全:)软件工程/系统软件/程序设计 ...

- mod_fastcgi和mod_fcgid的区别

mod_fcgid是一个跟mod_fastcgi二进制兼容的Apache module. 原 来的mod_fastcgi因为实现方式的限制,所以可能会创建了很多不必要的进程,而实际上只需要更少的进程就 ...

- 基于PCIe的高速接口设计

基于PCIe的高速接口设计 由 judyzhong 于 星期四, 03/03/2016 - 13:49 发表 作者:李晓宁,姚远程,秦明伟 2016年微型机与应用第1期 摘要:PCIe总线是第三代I/ ...

- 【Android】4.3 屏幕布局和旋转

分类:C#.Android.VS2015:创建日期:2016-02-06 为了控制屏幕的放置方向(纵向.横向),可以在Resource下同时定义两种不同的布局文件夹:layout和layout-lan ...

- 五个你必须知道的javascript和web debug技术

转:http://js8.in/2013/11/20/%E4%BA%94%E4%B8%AA%E4%BD%A0%E5%BF%85%E9%A1%BB%E7%9F%A5%E9%81%93%E7%9A%84j ...

- HDU 4565 So Easy!(公式化简+矩阵)

转载:http://www.klogk.com/posts/hdu4565/ 这里写的非常好,看看就知道了啊. 题意很easy.a,b,n都是正整数.求 Sn=⌈(a+b√)n⌉%m,(a−1)2&l ...

- C++面向对象程序设计的一些知识点(1)

1.函数重载而不出错是有条件的: (1).这些函数位于同一域内,如同一类中.同一文件中. (2).这些同名函数具有不同的参数特征标(特征标是指形參的个数.类型.排列顺序等). 2.引用特性(与指针对比 ...