数字IC设计入门必备——VIM自定义模板调用与VCS基本仿真操作示例

一、前言

毕业论文答辩结束,闲下来写篇文章。芯片研发人员都在Linux系统下借助各种EDA工具和代码语言完成工作,因此提高代码开发效率,熟练运用开发工具是十分必要的。本文讲述VIM编辑神器的verilogHDL自定义模板调用以及VCS仿真软件的基本使用方式。

二、VIM编辑器自定义模板调用

在之前的博文中谈到过GVIM编辑器中可以通过调用模板来生成重复性代码,但没有介绍自定义模板的方式。关于VIM的安装与配置详细内容,见参考文献1。这里主要用到VIM的用户配置文件:.vimrc(若没有新建该文件并编辑),我们在用户目录下使用ls -al命令可以看到该文件:

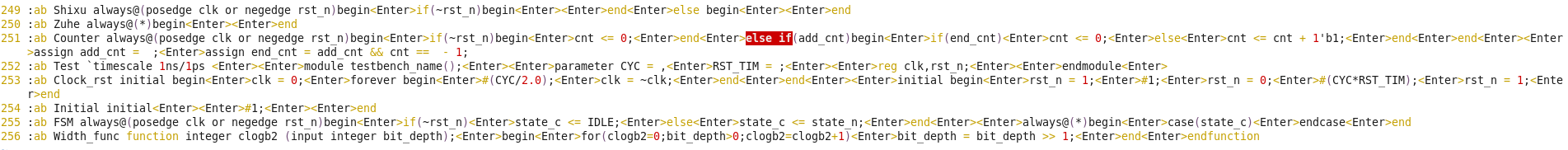

使用VIM编辑器打开VIM配置文件,以下部分是在文件底部自行添加的命令:

自定义模板的格式为 :ab <com> <code>

其中com是调用指令,code是当前指令生成的代码。我们新建一个.v文件测试下就能看出模板调用的妙处了。

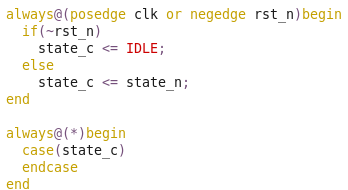

编辑(插入)模式下,输入Shixu后按下回车生成:

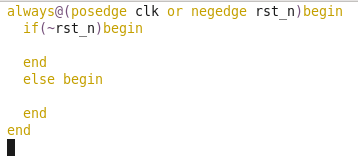

输入Zuhe后按下回车生成:

输入Counter后按下回车生成:

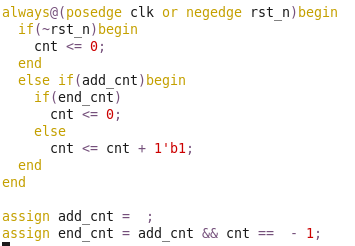

这三个是最常用到的代码,三者相互组合可以完成很多功能了。但若状态或工作模式较多,一般采用状态机完成。输入FSM后按下回车生成:

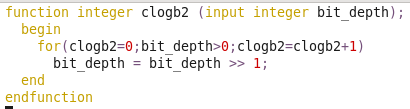

在设计时,经常要根据数值范围设定变量的位宽。此时经常用到一个位宽计算到函数。输入Width_func后按下回车生成:

在设计文件里常用的重复性代码基本就这些了,可以根据自己的coding style灵活调整。接下来说说testbench部分。输入Test后按下回车生成:

里边包括了testbench中的时钟和复位相关的参数与信号定义。实际上时钟和复位信号的产生也是可以复用的。输入Clock_rst后按下回车生成:

自定义模板还没有灵活到可以生成模块例化代码,这一部分功能得借助其他脚本语言完成了,笔者还没有尝试过。

三、VCS软件仿真

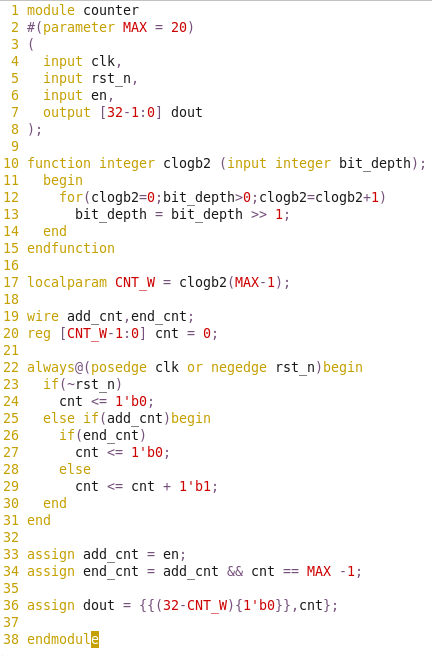

光说这个软件没什么意思,我们来举个栗子~设计一个计数器,输出位宽固定32位。当使能信号拉高则开始从0计数直到最大值后再次从0开始递增。设计代码counter.v:

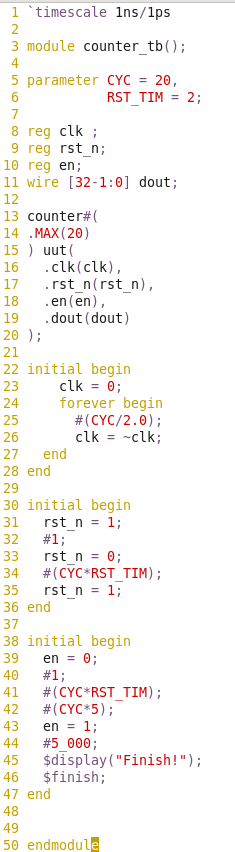

测试代码 counter_tb.v:

VCS仿真大体分为三步:编译、仿真以及调试。编译命令:vcs *.v -debug_all 命令行界面会显示些信息:

之后文件夹内会生成simv文件,执行该文件进行仿真。./simv -gui 这里使用-gui选项打开DVE图形界面。

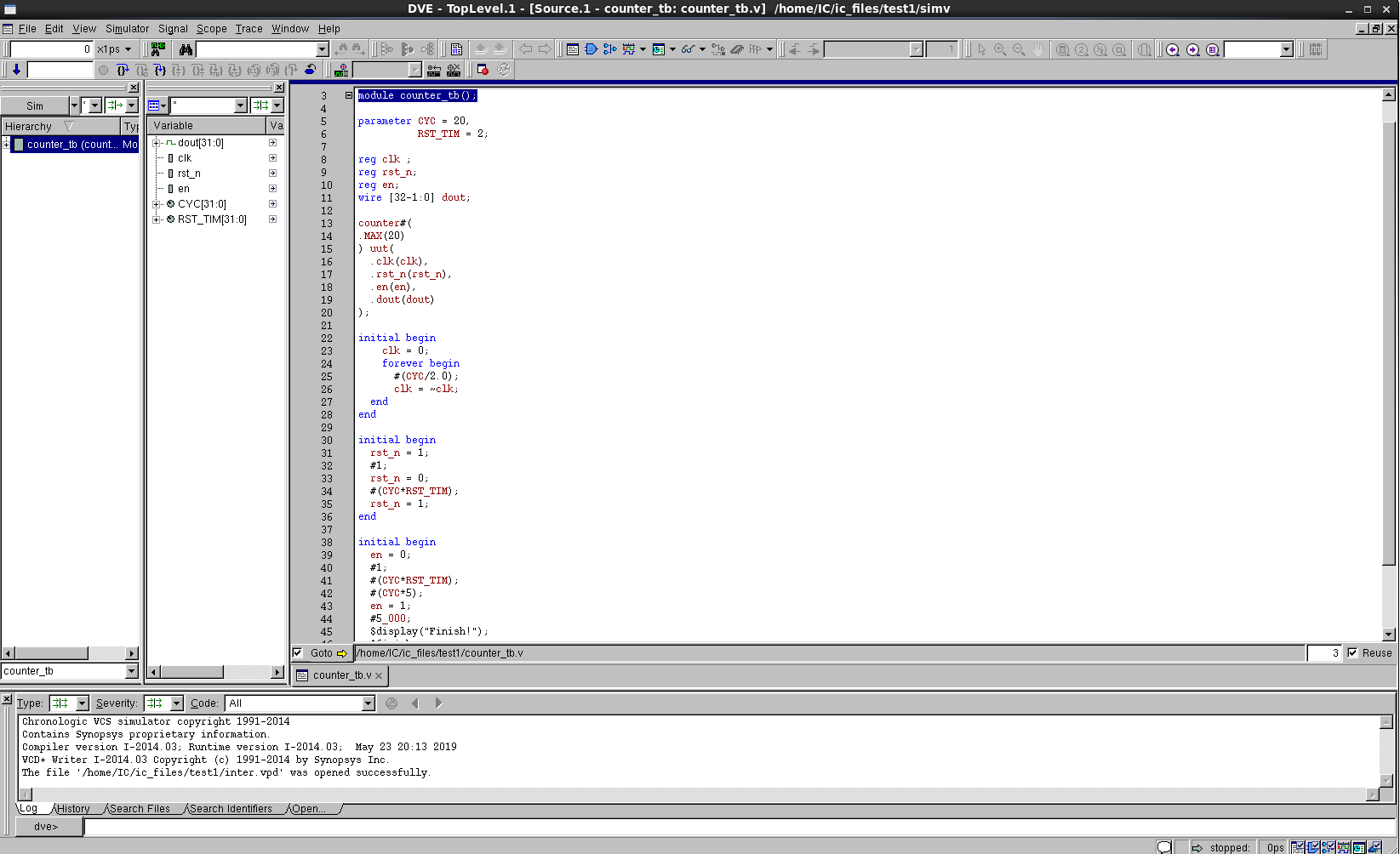

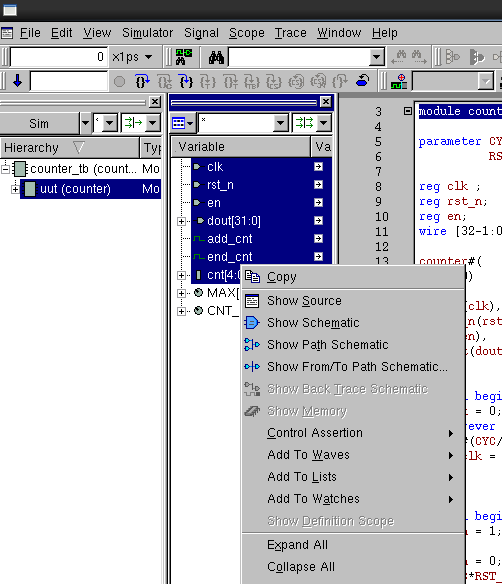

接下来的操作和常用的Modelsim差不多了。把要观测的信号添加到波形窗口:

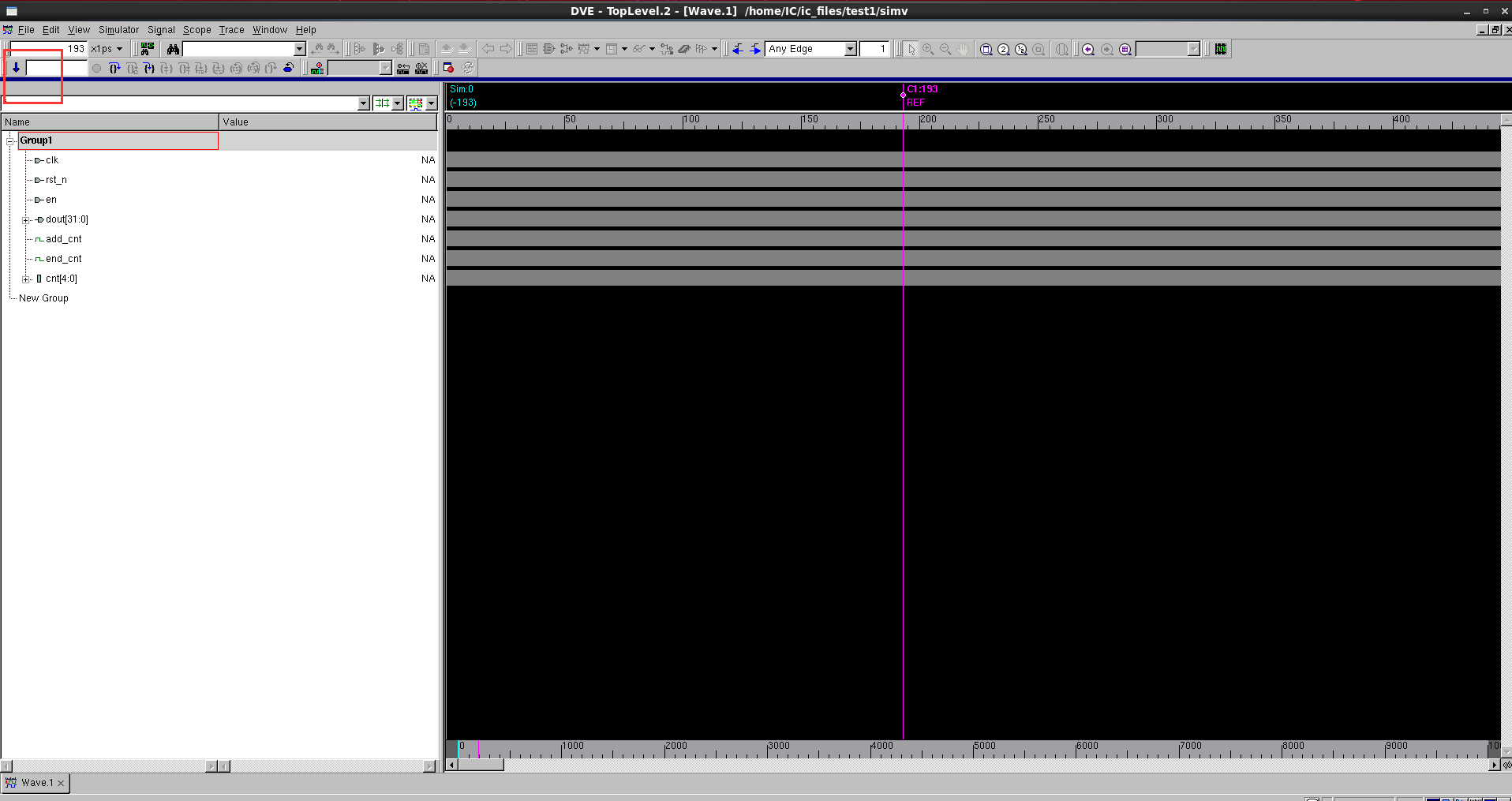

点击左上角按钮运行仿真:

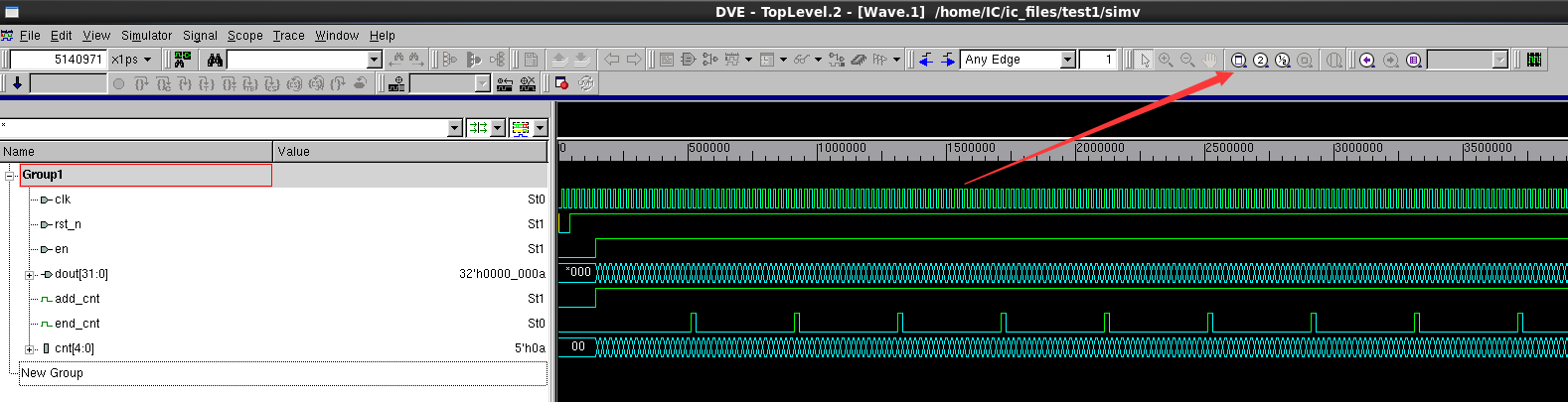

按下红色箭头所指位置观察全局波形:

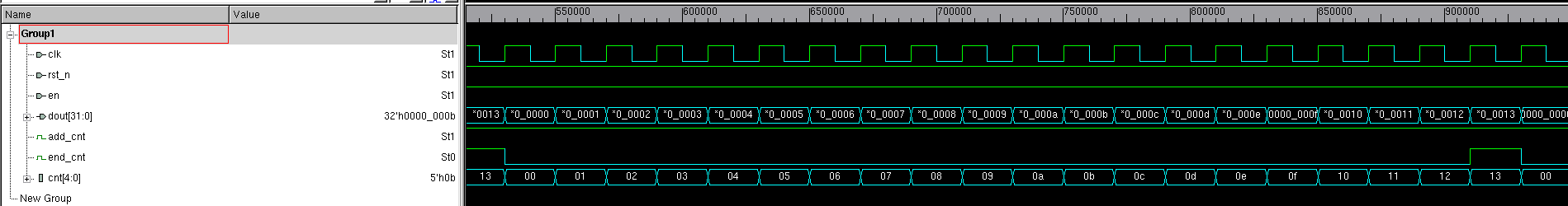

按住鼠标左键拖动来局部放大数据波形,计数器与输出从0到19周期性递增,功能正确。

复杂的操作后续用到再学。

参考文献

1 vim 的安装及配置 - QIYUEXIN - 博客园 https://www.cnblogs.com/qiyuexin/p/6398606.html

2 VCS使用学习 - IC_SOC_ARM - CSDN博客 https://blog.csdn.net/ic_soc_arm_robin/article/details/44262063

3 VCS-DVE - 百度文库 https://wenku.baidu.com/view/f5f7ce8f69eae009591becc1.html

4 数字芯片实验室的个人空间 - 哔哩哔哩 ( ゜- ゜)つロ 乾杯~ Bilibili https://space.bilibili.com/87907395/channel/detail?cid=64692

数字IC设计入门必备——VIM自定义模板调用与VCS基本仿真操作示例的更多相关文章

- 数字IC设计入门书单

首发于观芯志 写文章 数字IC设计入门书单 Forever snow 1 年前 作者:Forever snow链接:你所在领域的入门书单? - 知乎用户的回答来源:知乎著作权归作者所有,转 ...

- 数字IC设计工程师的知识结构

刚毕业的时候,我年少轻狂,以为自己已经可以独当一面,庙堂之上所学已经足以应付业界需要.然而在后来的工作过程中,我认识了很多牛人,也从他们身上学到了很多,从中总结了一个IC设计工程师需要具备的知识架构, ...

- VerilogHDL概述与数字IC设计流程学习笔记

一.HDL的概念和特征 HDL,Hard Discrimination Language的缩写,翻译过来就是硬件描述语言.那么什么是硬件描述语言呢?为什么不叫硬件设计语言呢?硬件描述语言,顾名思义就是 ...

- 【转载】数字IC设计流程及开发工具

原文链接:https://www.zhihu.com/question/28322269/answer/42048070 Design Flow &lt;img src="h ...

- 数字IC设计-15-DPI(延续)

简介 供SV,无论是构建测试激励,或模拟硬件的并行行为,DPI这是非常方便.上次我们介绍SV内通"import"导入和电话C性能. 在本节,通过一个简单的例子来说明C什么语言的函数 ...

- 数字IC设计工程师成长之路

学习的课程 仿真工具VCS实践学习 2019年12月9日-2019年12月23日

- 数字IC前后端设计中的时序收敛(五)--Max Transition违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程> 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程. 考虑到微信公众 ...

- 数字IC前后端设计中的时序收敛(四)--Max Capacitance违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程> 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程. 考虑到微信公众 ...

- 数字IC前后端设计中的时序收敛(三)--Hold违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程>(二维码见博文底部) 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教 ...

随机推荐

- javase(10)_多线程基础

一.排队等待 1.下面的这个简单的 Java 程序完成四项不相关的任务.这样的程序有单个控制线程,控制在这四个任务之间线性地移动.此外,因为所需的资源 ― 打印机.磁盘.数据库和显示屏 -- 由于硬件 ...

- LeetCode 数组中的第K个最大元素

在未排序的数组中找到第 k 个最大的元素.请注意,你需要找的是数组排序后的第 k 个最大的元素,而不是第 k 个不同的元素. 示例 1: 输入: [3,2,1,5,6,4] 和 k = 2 输出: 5 ...

- UVa-227-谜题

这题的话,我们读入的时候,可以用scanf单个读入字符,也可以用getchar函数来读入. scanf scanf读入串字符的时候,遇到空格.回车和TAB等空白字符就会停止读入,但是如果读入单个字符就 ...

- NOIP 2017 D2T1 奶酪

#include<iostream> #include<cstdio> #include<cstdlib> #include<algorithm> #i ...

- MySql的基操勿六

2018/12/6 星期四 19:34:07 authot by dabaine 数据库注释; -- 这就是注释 /*.....*/ 这也是注释 创建库; create databse [if not ...

- MySQL binlog-server搭建

MySQL binlog-server搭建 binlog在备份中起着至关重要的作用,备份binlog文件时,只能先在本地备份,然后才能传送到远程服务器上.从MySQL5.6版本后,可以利用mysqlb ...

- ssh 免密码登录 与 密钥公钥原理讲解

前言 由于最近频繁需要登录几个服务器,每次登录都需要输入密码,故相对麻烦. 由于个人服务器用于实验,故对安全性要求不是很高,故想实现ssh免密登录. 通过阅读ssh 公钥私钥认证操作及原理以及ssh公 ...

- Linux基础学习-基本命令

基本命令 date命令 参数 作用 %t 跳格 %H 小时(00-23) %I 小时(00-12) %M 分钟(00-59) %S 秒(00-59) %j 今年中的第几天 [root@qdlinux ...

- 《Spring源码深度解析》第二章 容器的基本实现

入门级别的spring配置文件 <beans xmlns="http://www.springframework.org/schema/beans" xmlns:xsi=&q ...

- IE6,7,8,9还有火狐浏览器的兼容

/*FF.Opear等支持Web标准的浏览器*/#header { margin-top: 23px; margin-bottom: 23px;}/*IE6浏览器*/*ht ...