(原创)Verilog三段式状态机

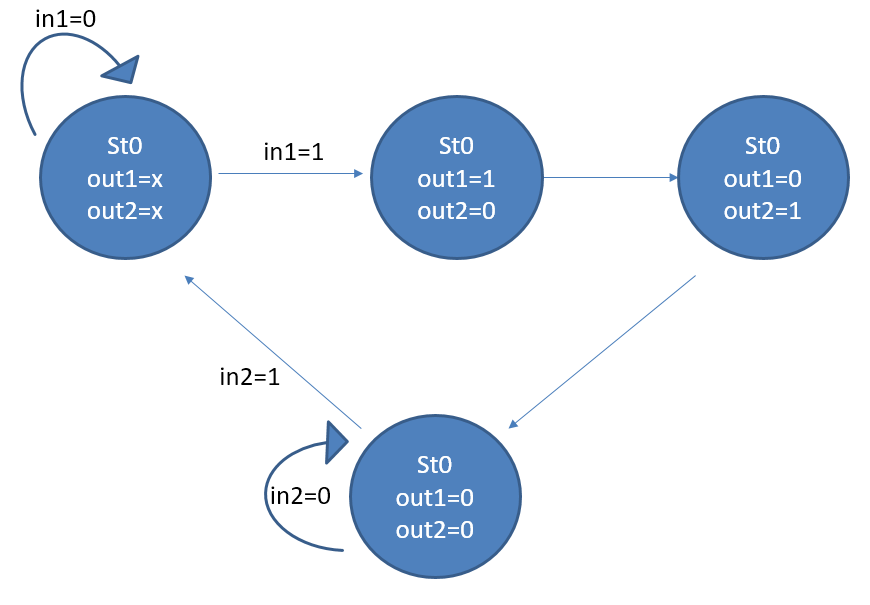

下面以上图一个简单的FSM说明三段式Verilog状态机范式:

`timescale 1ns / 1ps

module FSM(

clk,rst_n,

in1,in2,

out1,out2,

CS,NS

);

input clk,rst_n;

input in1,in2;

output out1,out2;

output [:] CS,NS; reg [:] CS,NS;

reg out1,out2; parameter St0 = 'b00,

St1 = 'b01,

St2 = 'b10,

St3 = 'b11; // 1、状态切换

always @(posedge clk or negedge rst_n)

if(!rst_n)

begin

CS<=St0;

end

else

CS<=NS; // 2、次态转移

always @ (*)

begin

case(CS)

St0:

begin

if(in1=='b1) NS=St1;

else NS=St0;

end

St1:

begin

NS=St2;

end

St2:

begin

NS=St3;

end

St3:

begin

if(in2=='b1) NS=St0;

else NS=St3;

end

default:NS=St0;

endcase

end //3、输出逻辑

always @(*)

begin

if(CS==St1) out1='b1;

else out1='b0;

if(CS==St2) out2='b1;

else out2='b0;

end endmodule

(原创)Verilog三段式状态机的更多相关文章

- Verilog三段式状态机描述

时序电路的状态是一个状态变量集合,这些状态变量在任意时刻的值都包含了为确定电路的未来行为而必需考虑的所有历史信息. 状态机采用VerilogHDL语言编码,建议分为三个always段完成. 三段式建模 ...

- verilog 三段式状态机的技巧

三段式代码多,但是有时钟同步,延时少,组合逻辑跟时序逻辑分开并行出错少. (1)同步状态转移 (2)当前状态判断接下来的状态 (3)动作输出 如果程序复杂可以不止三个always .always ...

- 10010序列检测器的三段式状态机实现(verilog)

序列检测器是时序数字电路设计中经典的教学范例,夏宇闻的<verilog数字系统设计教程>一书中有这个例子,用verilog设计一个“10010”序列的检测器.看完后我觉得F和G两个状态多余 ...

- Verilog笔记.三段式状态机

之前都是用的一段式状态机,逻辑与输出混在一起,复杂点的就比较吃力了. 所以就开始着手三段式状态机. 组合逻辑与时序逻辑分开,这样就能简单许多了. 但是两者在思考方式上也有着很大的区别. 三段式,分作: ...

- 简单三段式状态机实验2-LCD12864

此实验是在“基于I2C EPPRPM(AT24C02B) + LCD12864实验”基础上,把LCD模块里的一段式状态机改成三段式,I2C EPPROM模块暂时未改出来,一步一步来吧,改完后代码下载到 ...

- 简单三段式状态机实验1-SOS

一直想从一段式状态机切换到三段式状态机,从书上和网上不断搜寻三段式案例及方法,感觉很简单,就想拿之前做过的实验把一段式改成三段式,可是写起来并非那么简单,很棘手,改完后也没有成功,尤其状态机里面的计数 ...

- FPGA三段式状态机的思维陷阱

用三段式描述状态机的好处,国内外各位大牛都已经说的很多了,大致可归为以下三点: 1.将组合逻辑和时序逻辑分开,利于综合器分析优化和程序维护; 2.更符合设计的思维习惯; 3.代码少,比一段式状态机更简 ...

- 基于FPGA的三段式状态机

状态机分类: 通常, 状态机的状态数量有限, 称为有限状态机(FSM) .由于状态机所有触发器的时钟由同一脉冲边沿触发, 故也称之为同步状态机. 根据状态机的输出信号是否与电路的输入有关分为 Meal ...

- 三段式状态机 [CPLD/FPGA]

状态机的组成其实比较简单,要素大致有三个:输入,输出,还有状态. 状态机描述时关键是要描述清楚前面提高的几个状态机的要素,即如何进行状态转移:每个状态的输出是什么:状态转移是否和输入条件相关等. 有人 ...

随机推荐

- Oracle解决ora-01653 无法通过1024扩展

综合上述检查结果,可断定遇到的问题是因为可能性1—表空间不足导致.解决办法也就是扩大表空间 扩大表空间的四种方法: 1.增加数据文件 ALTER TABLESPACE ***_TRD ADD DATA ...

- php(一)搭建php开发环境

1.下载php语言包 php作为一门语言,本身可以是一个纯绿色版的"文件夹"——称之为"php语言包".windows版的下载地址:https://window ...

- 移动端遇到的问题小结--video

本篇主要是针对Android系统,所遇到的问题. 1. video的全屏处理: 这里说的全屏是指针对浏览器的全屏,而不是整个手机的全屏.要想全屏效果只需对video标签加 webkit-plays ...

- Scala映射与元组篇

*Scala有十分易用的语法来创建.查询和便利映射 *你需要从可变的和不可变的映射中做出选择 *默认情况下,你得到的是一个哈希映射,不过你也可以指明要树形映射 *你可以很容易地在Scala映射和Jav ...

- pc端结合canvas实现简单签名功能

需求:业务员做提交时要签名... 代码不多简单易懂,直接看代码 <!DOCTYPE html> <html> <head> <meta charset=&qu ...

- mongodb数据库操作方法

// Schema.Model.Entity或者Documents的关系请牢记,Schema生成Model,Model创造Entity,Model和Entity都可对数据库操作造成影响,但Model比 ...

- java ssl 连接AD域

1.安装证书服务和IIS服务,不需要启动asp.(其会在c盘生成一个crt文件)2.获取crt证书文件 windows 2003:文件位于系统盘根目录 windows 2008: 文件位于C:\Win ...

- Python用起来极度舒适的强大背后

当你使用len(a)获取a的长度,使用obj[key]获取一个key的值时的畅快和舒适,在于Python庞大的设计思想(Pythonic). 而obj[key]背后其实是__getitem__方法,P ...

- lnamp环境搭建博客、论坛

实验环境:Centos6.5 源码安装Nginx yum安装Apache.php.Mysql Mysql: yum -y install mysql-server 安装Mysql数据库 /etc/i ...

- Intellij Idea 解决字符乱码、设定颜色主题、字体

1.写入字符编码设置 2.调整mintty 字体.主题