FPGA在电平接口领域的应用

电子技术的发展,产生了各种各样的电平接口。

TTL电平:

TTL电平信号之所以被广泛使用,原因是因为:通常我们采用二进制来表示数据。而且规定,+5V等价于逻辑“1”,0V等价于逻辑“0”。这样的数据通信及电平规定方式,被称做TTL(晶体管-晶体管逻辑电平)信号系统。这是计算机处理器控制的设备内部各部分之间通信的标准技术。

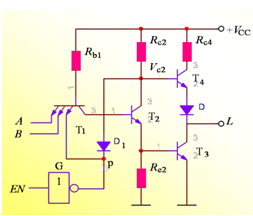

TTL三态门

CMOS电平:

CMOS电平逻辑电平电压接近于电源电压,0 逻辑电平接近于 0V。而且具有很宽的噪声容限。

CMOS电路由于输入太大的电流,内部的电流急剧增大,除非切断电源,电流一直在增大。这种效应就是锁定效应。当产生锁定效应时,COMS的内部电流能达到40mA以上,很容易烧毁芯片。

防御措施:

- 在输入端和输出端加钳位电路,使输入和输出不超过规定电压。

- 芯片的电源输入端加去耦电路,防止VDD端出现瞬间的高压。

- 在VDD和外电源之间加限流电阻,即使有大的电流也不让它进去。

- 当系统由几个电源分别供电时,开关要按下列顺序:开启时,先开启CMOS电路的电源,再开启输入信号和负载的电源;关闭时,先关闭输入信号和负载的电源,再关闭CMOS 电路的电源。

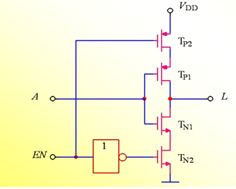

CMOS三态门

TTL电路与CMOS电路比较:

TTL电路是电流控制器件,而CMOS电路是电压控制器件。

TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。

CMOS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。

CMOS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。

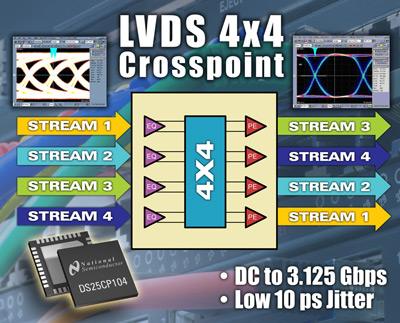

LVDS电平:

LVDS(Low Voltage Differential Signal)即低电压差分信号,其特性如下:

低摆幅(约为350 mV)。低电流驱动模式意味着可实现高速传输。ANSI/TIA/EIA644建议了655 Mb/s的最大速率和1.923 Gb/s的无失真通道上的理论极限速率。

低压摆幅。恒流源电流驱动,把输出电流限制到约为3.5 mA左右,使跳变期间的尖峰干扰最小,因而产生的功耗非常小。这允许集成电路密度的进一步提高,即提高了PCB板的效能,减少了成本。

具有相对较慢的边缘速率(dV/dt约为0.300 V/0.3 ns,即为1 V/ns),同时采用差分传输形式,使其信号噪声和EMI都大为减少,同时也具有较强的抗干扰能力。

所以,LVDS具有高速、超低功耗、低噪声和低成本的优良特性。

LVDS应用

典型LVDS电路

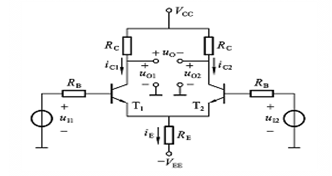

PECL电平:

PECL,指的是正射极耦合逻辑电平。 在电子技术中,PECL代表正射极耦合逻辑电平。如果省掉ECL电路中的负电源,采用正电源的系统(+5 V),可将VCC接到正电源而VEE接到零点。这样的电平通常被称为PECL(Positive Emitter Coupled Logic)。如果采用+3.3 V供电,则称为LVPECL。

ECL(EmitterCoupled Logic)即射极耦合逻辑,是带有射随输出结构的典型输入输出接口电路,ECL电路的最大特点是其基本门电路工作在非饱和状态,因此ECL又称为非饱和性逻辑。也正因为如此,ECL电路的最大优点是具有相当高的速度。这种电路的平均延迟时间可达几个ns数量级甚至更少。

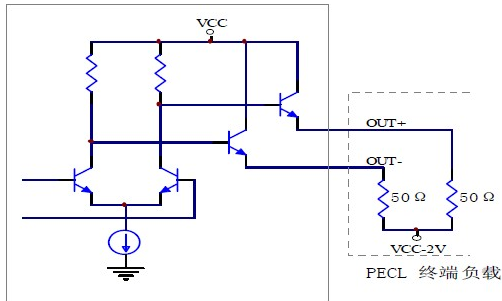

PECL输出结构

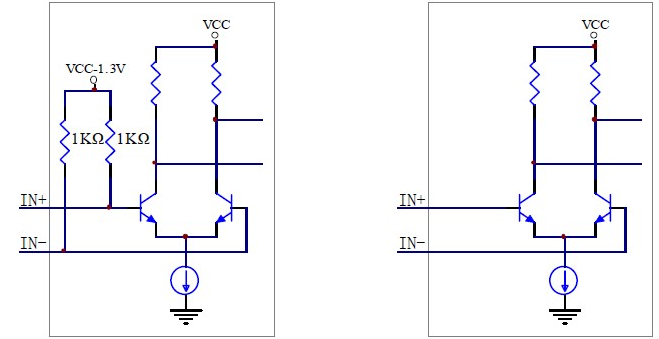

PECL 片内偏置输入 PECL 片外偏置输入

HSTL电平:

HSTL(High Speed Transceiver Logic)是一种技术独立的数字集成电路接口标准,为了实现电压扩展和技术独立I/O结构而开发的。

此标准所要求的I/O结构是差分放大输入(一个输入内部关联成一个用户提供的输入参考电压,此电压用于单端输入)和使用Vcco的输出。所谓技术独立,实际上指用来做输入参考和输出Vcco的电压,与器件本身的供电电压不同。

HSTL最主要的应用是可以用于高速存储器(SDRAM、DDR SDRAM)读写。传统的慢速存储器访问时间阻碍了高速处理器的运算操作。在中频区域(100MHz和180MHz之间),可供选择基于单端信号的I/O结构有:HSTL、GTL/GTL+、SSTL和低压TTL(LVTTL)。在180MHz以上的范围,HSTL标准是唯一可用的单端I/O接口。利用HSTL的速度,快速I/O接口明显地提高了整个系统的性能。HSTL是高速存储器应用的I/O接口选择,同时也很完美地提供了驱动多个内存模块地址总线的能力。

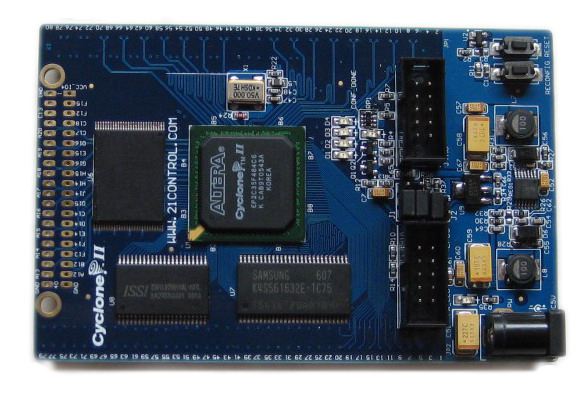

FPGA+SDRAM

GTL/GTL+电平:

GTL:类似CMOS的一种结构,输入为比较器结构,比较器一端接参考电平,另一端接输入信号。1.2V电源供电。 Vcc=1.2V;VOH>=1.1V;VOL<=0.4V;VIH>=0.85V;VIL<=0.75V ,PGTL/GTL+:Vcc=1.5V;VOH>=1.4V;VOL<=0.46V;VIH>=1.2V;VIL<=0.8V 。

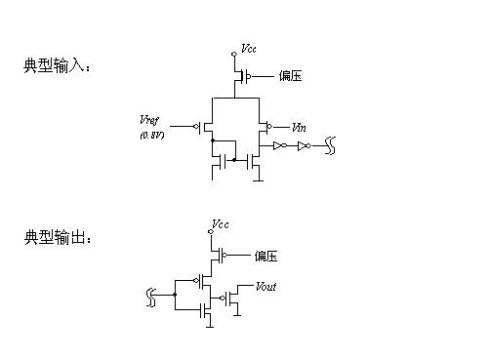

GTL输入与输出

SSTL电平:

SSTL(Stub Series Terminated Logic)接口标准也是JEDEC所认可的标准之一。该标准专门针对高速内存(特别是SDRAM)接口。SSTL规定了开关特点和特殊的端接方案,它是为了在高速存储总线上提高信号完整性的目的而创建的。SSTL_3是3.3V标准;SSTL_2是2.5V标准,SSTL_18是1.8V标准。

它与LVTTL和LVCMOS的不同在于SSTL是传输线终端匹配的。因此SSTL具有输出阻抗和匹配方法的要求,这使其在高速信号传输时降低了EMI,改善建立时间。SSTL的输入是一个差分对比电路,一端为输入,另一端为参考电压VREF,DDR应用SSTL电平比较多。

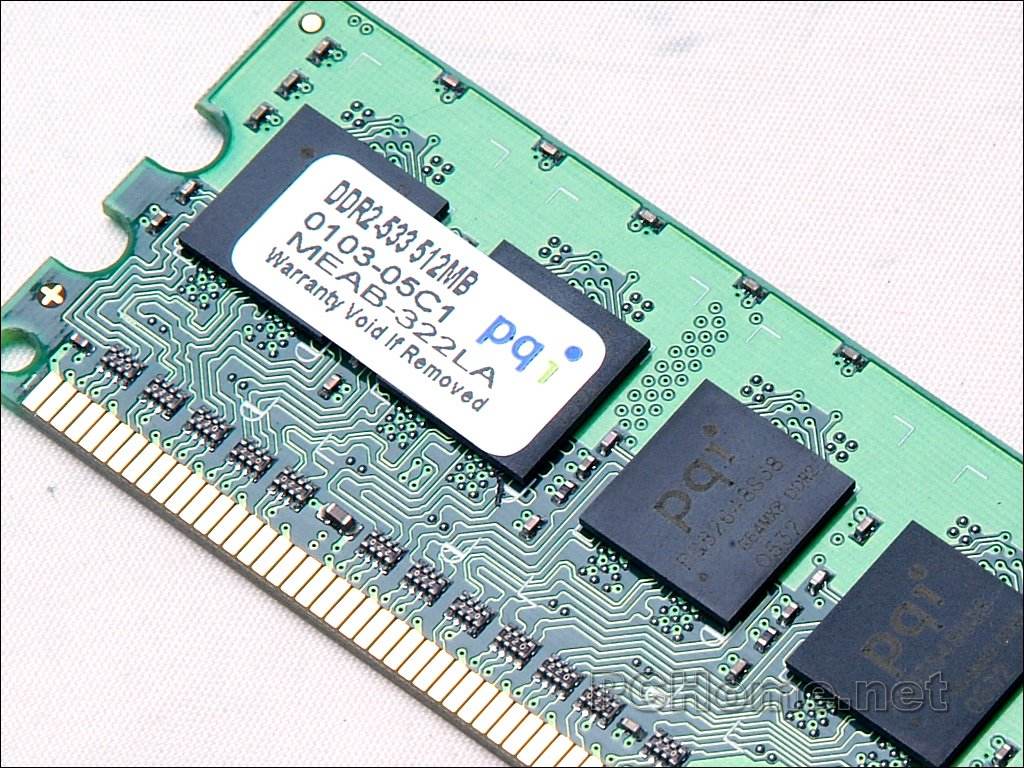

DDRII SDRAM 内存条

在这样的混合电平环境里面,如果用传统的电平转换器件实现接口会导致电路复杂性提高。利用FPGA支持多电平共存的特性,可以大大简化设计方案,降低设计风险。

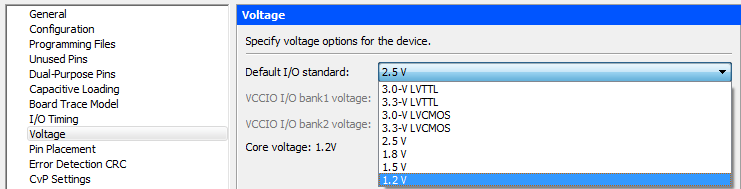

FPGA IO电压配置

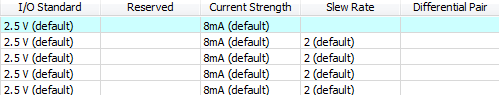

FPGA IO电压配置,电流配置以及翻转速率

这只是FPGA应用领域的冰山一角,如今FPGA应用于各个技术领域。

版权所有权归卿萃科技,转载请注明出处。

作者:卿萃科技ALIFPGA

原文地址:卿萃科技FPGA极客空间 微信公众号

扫描二维码关注卿萃科技FPGA极客空间

FPGA在电平接口领域的应用的更多相关文章

- 基于FPGA的PCIe接口实现(具体讲解了数据流向)

时间:2014-12-09 来源:西安电子科技大学电子工程学院 作者:姜 宁,陈建春,王 沛,石 婷 摘要 PCI Express是一种高性能互连协议,被广泛应用于网络适配.图形加速器.网络存储.大数 ...

- FPGA控制RGMII接口PHY芯片基础

一.前言 网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG.但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统.这类接口总线位宽小 ...

- FPGA与安防领域

安防主要包括:闭路监控系统.防盗报警系统.楼宇对讲系统.停车厂管理系统.小区一卡通系统.红外周界报警系统.电子围栏.巡更系统.考勤门禁系统.安防机房系统.电子考场系统.智能门锁等等. 在监控系统中,F ...

- FPGA高速ADC接口实战——250MSPS采样率ADC9481

一.前言 最近忙于硕士毕业设计和论文,没有太多时间编写博客,现总结下之前在某个项目中用到的一个高速ADC接口设计部分.ADC这一器件经常用于无线通信.传感.测试测量等领域.目前数字系统对高速数据采集的 ...

- 【转载】 Jointwave零延时视频传输for FPGA/ASIC进入军工领域

半导体知识产权H.264/H.265 硅IP核供应商Jointwave公司的发布了一系列视频编解码RTL IP核,已经成功应用于军事工业领域的指挥作战,无人机UAV控制,航空和航天摄像机,视频记录黑匣 ...

- FPGA学习-VGA接口

一般FPGA开发板的VGA会向用户暴露两共五个种接口,第一种是时序信号,用于同步传输和显示:第二种是色彩信号,用于随着时序把色彩显示到显示器上 时序接口 行同步信号-用于指示一行内像素的显示 场同步信 ...

- 基于FPGA的VGA接口使用

前言 什么是VGA? VGA(视频图形阵列)是IBM公司制定的一种视频数据传输标准. 接口信号主要有5个:R(Red),G(Green),B(Blue),HS(Horizontal synchroni ...

- fpga xilink 电平

- FPGA学习-PS2接口

选自http://m.elecfans.com/article/774143.html

随机推荐

- [译] 反思 1 号进程 / Rethinking PID 1

By Lennart Poettering 译 SReadFox 原文链接:http://0pointer.de/blog/projects/systemd.html 译注:笔者大约在 2011 年读 ...

- UCOS-II学习记录

本文主要记录使用UCOS II的相关内容.包括如何完成第一个UCOS II应用程序,和如何创建任务,如何获取系统时间,和利用i3086 驱动完成时间获取,屏幕显示,按键驱动,信号量等内容. UCOS- ...

- Kendo UI 使用小知识点汇总

本攻略适用于了解的kendo UI 的基本语法的人使用.如果还不了解Kendo UI的基本语法,请大力观摹Demo ,并自己动用写几个控件. 1.获取Kendo UI的控件实体,不必存成全局变量. ...

- NHibernate教程(18)--对象状态

本节内容 引入 对象状态 对象状态转换 结语 引入 在程序运行过程中使用对象的方式对数据库进行操作,这必然会产生一系列的持久化类的实例对象.这些对象可能是刚刚创建并准备存储的,也可能是从数据库中查询的 ...

- 【深入Java虚拟机】之八:Java垃圾收集机制

转载请注明出处:http://blog.csdn.net/ns_code/article/details/18076173 对象引用 Java中的垃圾回收一般是在Java堆中进行,因为堆中几乎存放了J ...

- 201521123065《Java程序设计》第六周学习总结

1. 本周学习总结 1.1 面向对象学习暂告一段落,请使用思维导图,以封装.继承.多态为核心概念画一张思维导图,对面向对象思想进行一个总结. 1.2 可选:使用常规方法总结其他上课内容. 1.publ ...

- 201521123071 《JAVA程序设计》第十四周学习总结

第14周作业-数据库 1. 本周学习总结 1.1 以你喜欢的方式(思维导图.Onenote或其他)归纳总结多数据库相关内容. 1.使用JDBC将Java程序与数据库连接 1.1注册驱动 Class.f ...

- 201521123073 《Java程序设计》第12周学习总结

1. 本周学习总结 1.1 以你喜欢的方式(思维导图或其他)归纳总结多流与文件相关内容. 2. 书面作业 将Student对象(属性:int id, String name,int age,doubl ...

- 201521123075 《Java程序设计》第13周学习总结

1. 本周学习总结 协议 网络中为了进行数据交换(通信)而建立的规则.标准或约定(=语义+语法+规则),比如http, ftp等 IP层协议(Internet Protocol) Internet上的 ...

- 201521123096《Java程序设计》第十三周学习总结

1. 本周学习总结 以你喜欢的方式(思维导图.OneNote或其他)归纳总结多网络相关内容. 2. 书面作业 1. 网络基础 1.1 比较ping www.baidu.com与ping cec.jmu ...