用FPGA设计LCD 转 VGA

这个东西其实是在上一个冬天就做完了,而且似乎已经产业化了,当时是为一位朋友做的,这个朋友再卖给产业化的人,就像流于俗套的故事一样,这个朋友拿到了钱,不过不像项目开始时说的那样与我有关。想想多年前一起吃喝拉撒的场景,叹了一口气抹去那些记忆,也只能算了。现在把这个设计写在博文博文中,一方面可以回忆回忆当时的设计思路,也希望可以为其他设计FPGA的兄弟姐妹们提供一点参考。

当时的写的ppt文档可在下列地址下载:

http://blogimg.chinaunix.net/blog/upfile2/101222213657.pdf

这个板子其实就是在烂大街的S3C2410的板子上加一片FPGA EP2C5,SDRAM和ADV7123。由于2410有LCD控制器,在LCD接口的外面加一片Video DAC,这个板子上的ADV7123就可以输出VGA信号,就可以接显示器了。但是当输出的分辨率过高,比如1024x768甚至更高的时候,LCD接口要求的带宽过高,这样就会影响2410上面的应用的运行速度。

因此就产生了这个设计,这个设计的目的就是让2410输出高分辨率低帧率的信号,比如1024x768@20HZ,通过FPGA把输出的图像保存在其控制的SDRAM中,然后FPGA中的图像产生部分再把这些数据读出来,按照1024x768@60HZ的速度输出到ADV7123上。

这个设计对于心电监护这样的设备已经够用了,因为心电信号的更新低于20HZ,其实它适用于所有刷新率要求不高但是要接VGA显示器的场合。

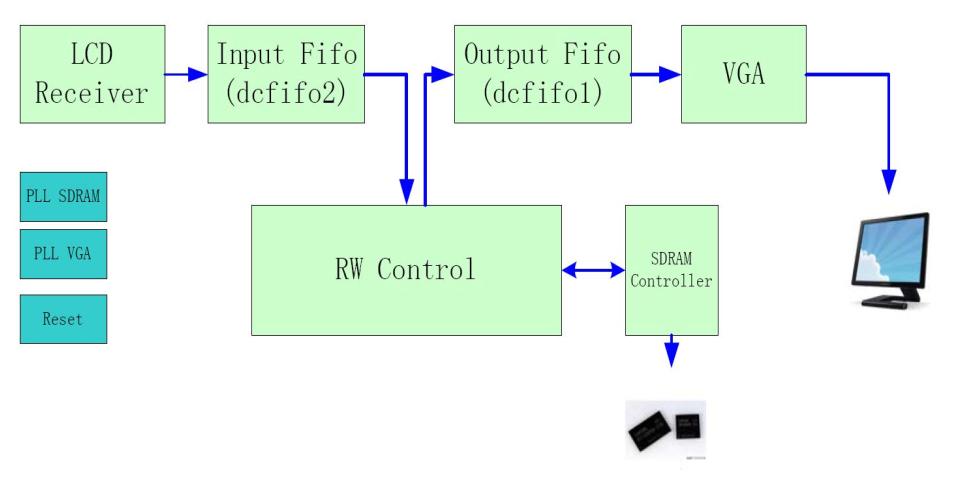

系统的框架大概就是上面这个样子的了,LCD Receiver是从2410LCD接口接收数据的了,其实就是检测到HSYNC,VSYNC,VDEN后通过CLK将数据采集进来,然后存储到FIFO中,这部分的逻辑需要根据2410的LCD时序进行设计。使用FIFO有两个用处,一方面是匹配读写的速度,一方面是转换数据宽度,因为只是用2410 LCD输出数据中的8bit数据,即RGB332, 而SDRAM和RW Control 模块都是按照16bit进行操作的,因此可以通过一个8bit输入16bit输出的FIFO进行转换。

RW Control模块顾名思义,主要是进行SDRAM读写控制了,当收到dcfifo2的Almost Full的时候读取dcfifo2将其写入SRAM,当收到dcfifo1的Almost Empty的时候,读取SDRAM中的数据将其写入dcfifo1供VGA模块转换。dcfifo1是一个16bit输入8bit输出的FIFO,其功能和dcfifo2 正好相反。

其中的PLL、FIFO模块用的就是Altera Quartus中的现成模块,SDRAM用的也是altera的开源模块,就是ref-sdr-sdram-verilog.zip,在google搜索有一大堆,只要把其中定义总线宽度的地方改一改就差不多可以用了,其它的关于刷新时间之类的SDRAM的初始化参数则是在RW Control模块启动的时候发出命令,再让SDRAM控制模块传给SDRAM芯片的。

VGA产生模块从dcfifo1读取图像数据,产生相应的信号控制Video DAC。主要是要搞清楚前肩,后肩的概率,其实就是每一行(或一帧)后面和前面的间隙时间。输出的时钟频率尽量符合标准的规范。

就像所有的开发一样,设计只是其中很小的一部分,最大的一部分是调试。Altera SignalTrap相当于是一个免费的逻辑分析仪,虽然其存储深度和芯片内部的存储器大小相关,但是还是相当方便的。如何使用可以参考altera的application note。

参考资料

http://item.taobao.com/item.htm?spm=a1z10.5-c.w4002-2613737244.20.P9tQJG&id=43634840829

用FPGA设计LCD 转 VGA的更多相关文章

- FPGA驱动LCD显示红绿蓝彩条

实验目的:先简单熟悉LCD灯的驱动和时序图的代码实现.设计功能是让LCD显示红绿蓝三种颜色,即三个彩带.本次实验比较容易实现,主要是对LCD驱动时序图的理解和时序参数的配置. 实验条件:1.LCD原理 ...

- 02-FPGA设计流程介绍——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线——普利斯队长精心奉献 课程目标: 1.了解并学会FPGA开发设计的整体流程 2.设计一个二选一选择器并进行功能仿真.时序仿真以及板级验证 实验平台:芯航线FPGA开发板.杜邦线 实验内容: 良 ...

- 【转】 FPGA设计的四种常用思想与技巧

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作.串并转换.流水线操作.数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作 ...

- 5.防止FPGA设计中综合后的信号被优化

随着FPGA设计复杂程度越来越高,芯片内部逻辑分析功能显得越来越重要.硬件层次上的逻辑分析仪价格十分昂贵,而且操作比较复杂.目前,FPGA芯片的两大供应商都为自己的FPGA芯片提供了软件层面上的逻辑分 ...

- 【转载】如何在FPGA设计环境中添加加时序约束

转自:http://bbs.ednchina.com/BLOG_ARTICLE_198929.HTM 如何在FPGA设计环境中加时序约束 在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序 ...

- 至芯FPGA培训中心-1天FPGA设计集训(赠送FPGA开发板)

至芯FPGA培训中心-1天FPGA设计集训(赠送开发板) 开课时间2014年5月3日 课程介绍 FPGA设计初级培训班是针对于FPGA设计技术初学者的课程.课程不仅是对FPGA结构资源和设计流程的描述 ...

- FPGA 设计流程,延迟,时间

FPGA 设计流程,延迟,时间 流程:每个时钟周期可以传输的数据比特. 延迟:从输入到时钟周期的输出数据需要经验. 时间:两个元件之间的最大延迟,最高时钟速度. 1 採用流水线能够提高 流量: 比如计 ...

- FPGA设计思想与技巧(转载)

题记:这个笔记不是特权同学自己整理的,特权同学只是对这个笔记做了一下完善,也忘了是从那DOWNLOAD来的,首先对整理者表示感谢.这些知识点确实都很实用,这些设计思想或者也可以说是经验吧,是很值得每一 ...

- 【重新发布,代码开源】FPGA设计千兆以太网MAC(1)——通过MDIO接口配置与检测PHY芯片

原创博客,转载请注明出处:[重新发布,代码开源]FPGA设计千兆以太网MAC(1)——通过MDIO接口配置与检测PHY芯片 - 没落骑士 - 博客园 https://www.cnblogs.com/m ...

随机推荐

- UNIX env查找技巧

在一些UNIX系统上,也许可以避免硬编码Python解释器的路径,而可以在文件特定的第一行注释中这样写: #!/usr/bin/env python ... script goes here ... ...

- web自动化测试启示篇

1.首先,对于想学自动化测试的朋友,那么你得懂一种语言,常用的比如Java或者Python.因为没有语言基础,你是写不出自动化脚本的. 我个人选择java 2.有了开发语言的铺垫,那么开始入手Sele ...

- css未知高度垂直居中

<!doctype html> <html lang="en"> <head> <meta charset="utf-8&quo ...

- PHP-会话控制Cookie和Session

会话控制:就是为了我们在访问页面和页面之间的跳转是,能够识别到你的登录状态,已经你的登录时长等 在php的会话控制当中,涉及到两个概念Cookie和Session Cookie 会话控制 原理:在登录 ...

- PowerMock学习(五)之Verifying的使用

前言 Verifying是一个非常强大的测试工具,在mock系列框架中使用广泛,主要用于验证方法是否被调用,下面将举例说明. 场景 模拟这样一个场景,通过Dao查询学生,如果存在更新原来学生,不存在则 ...

- mysql锁简谈

1.mysql锁, 作用:解决因资源共享而造成的并发问题. 实例:买最好一件衣服X A: X 买: X加锁----->试衣服……下单……付款……打包….------>X解锁 B: X 买: ...

- Spring Boot (一) 校验表单重复提交

一.前言 在某些情况下,由于网速慢,用户操作有误(连续点击两下提交按钮),页面卡顿等原因,可能会出现表单数据重复提交造成数据库保存多条重复数据. 存在如上问题可以交给前端解决,判断多长时间内不能再次点 ...

- 20191010-9 alpha week 1/2 Scrum立会报告+燃尽图 07

此作业要求参见https://edu.cnblogs.com/campus/nenu/2019fall/homework/8752 一.小组情况 队名:扛把子 组长:迟俊文 组员:宋晓丽 梁梦瑶 韩昊 ...

- python3 之 面向对象(类)、继承、派生和多态

类提供了一种 组合数据和功能 的方法.创建一个新类意味着:创建一个新 类型 的对象,从而允许创建一个该类型的新 实例. 每个类的实例可以拥有: 保存自己状态的属性. 一个类的实例也可以有改变自己状态 ...

- JavaScript笔记八

1.原型(prototype) - 创建一个函数以后,解析器都会默认在函数中添加一个数prototype prototype属性指向的是一个对象,这个对象我们称为原型对象. - 当函数作为构造函数使用 ...