Timing path

Timing path:从register clock/input port开始,经过一些combinational logic,终止在register data/output port。

PT以path grouping为单位来分析和报告timing。

DC,每个path group可以指定一个weight,来尽力做design optimizaiton,但是这个weight在PT中并没有用。

每个create clock命令都会生成一个对应的path group。

PT中还有自己的default group:clock_gating_default**:path以combinational element为终点。

async_default*:path以async的preset和clear为终点。

*default*:剩下的所有clock,如以output为终点的clock。

也可以自己定义group_path:group_path -name out1bus -to [get_ports OUT_1*] 然后可以报告该path group的timing。

report_timing命令中的属性:

Number of paths:-nworst 显示每个end point最worst的N条path,-max_paths 显示整个group的worst path的个数

Types of paths:-path_type full -delay_type max

Amount of detail

Startpoints,endpoint

-path_type full_clock/full_clock_expanded 显示完整的data path和clock path

full 显示完整data path

short 只显示一条data path的startpoint和endpoint

-transition_time 报告路径的transition time

-capacitance 报告路径的capacitance

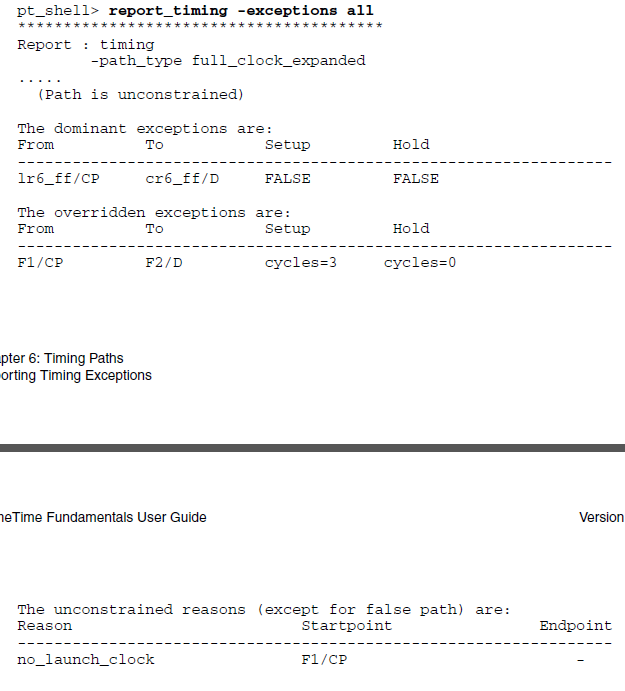

对于exception timing的rpt:

1)-exceptions dominant 报告路径中的exception constrained

2)-exceptions overridden 报告路径中被覆盖的exception constrained

3)-exceptions all 报告所有的exception path,包括unconstrained startpoint 和unconstrained endpoint

exceptions path的三种属性:方便进行filter

dominant_exception timing path的类型:false path, min_delay, max_delay, multicycle_path

endpoint_unconstrained_reason:no_capture_clock, dangling_end_point(floating point no timing constraints), danin_of_disable(disable timing arc)

startpoint_unconstrained_reason:no_launch_clock,dangling_start_point,fanout_of_disable

filter_collection $path {defined(dominant_exception)}

filter_collection $path {undefined(dominant_exception)}

get_timing_path更好的删选timing path

set x [get_timing_paths -from A -through B -to C]

report_timing $x -exceptions all

Path Sepecification Methods

-from $startpoint

-to $endpoint

-through

report_timing -from [get_clocks ...] -though $startpoint

report_timing -through $endpoint -to [get_clocks ...]

report_timing -through {B1 B2}

更加精细的方式:

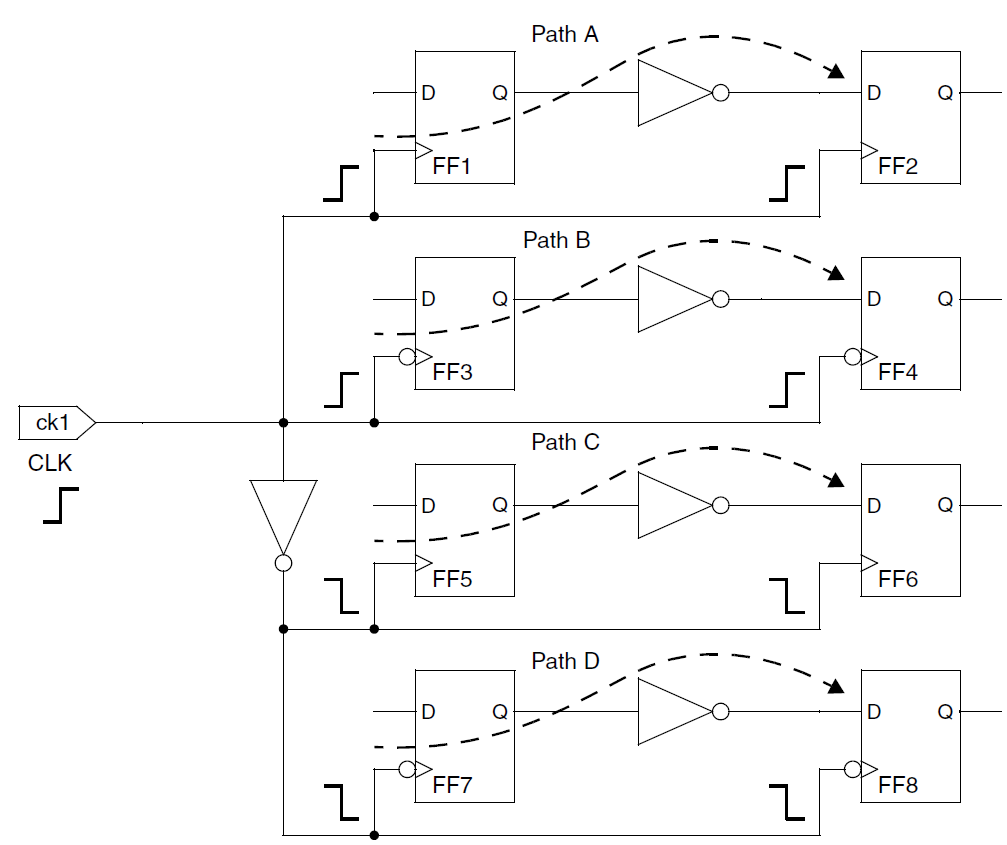

-rise_from/-rise_to

-fall_from/-fall_through...

set_false_path -to [get_clocks CLK] :取以CLK为终点的timing path,data端的FF的clock是CLK

path:a,b,c,d有效

set_false_path -rise_from [get_clocks CLK] :以CLK为起点,且data端以clock的rising edge来触发

path:a,d有效

report_timing -rise_from [get_clock clk] -nworst 100

对于delay的report:

report_delay_calculation -from BLK1/A -to BLK1/z

Timing path的更多相关文章

- standard cell timing model

standard cell timing model 主要包括两方面的信息: Cell Delay calculation Output Transition calculation 首先,cel ...

- 读懂timing report

三部分:表头/launch path /capture path 1.表头 1) 工具版本信息:如示例中的18.10-p001,对某个具体项目timing signoff 工具的版本最好保证一致: 操 ...

- clock

Prime Time中的clock分析包括: 1)Multiple clocks,clock from port/pin,virtual clock. 2)Clock network delay an ...

- (数字IC)低功耗设计入门(六)——门级电路低功耗设计优化

三.门级电路低功耗设计优化 (1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化 ...

- IN2REG group 的时序分析

针对 IN2REG 的 timing group,其 timing 模型是假设 input pin 外面有一个虚拟的reg(如图中的 reg1),这个虚拟reg的 clock 是 virtual cl ...

- clock gating check

在 sta 分析时,经常会碰到 clock gating cell (一般是 ICG cell 或者 latch)引起的 violation,这种 violation 很常见,而且往往很难修. 为什么 ...

- STA分析(七) sdc

STA分析前的环境设置,包括:setup clocks,specifying IO characteristics 1)定义一个master clock:create_clock -name .. - ...

- STA分析(一) setup and hold

timing check可以分为Dynamic Timing Analysis(Post_sim)和Static Timing Analysis STA:可以分析的很全面:仿真速度也很快:可以分析控制 ...

- FPGA静态时序分析基础

FPGA静态时序分析基础 基本概念 Skew: 时钟偏移 Skew表示时钟到达不同触发器的延时差别,Tskew = 时钟到达2号触发器的时刻 - 时钟到达1号触发器的时刻. Jitter: 时钟抖动 ...

随机推荐

- memcache 缓存失效问题(转)

在大并发的场合,当cache失效时,大量并发同时取不到cache,会同一瞬间去访问db并回设cache,可能会给系统带来潜在的超负荷风险. 解决方法 方法一 在load db之前先add一个mutex ...

- flume-ng配置文档简单说明

1.配置文件现状 1.1 Flume数据接收端 IP地址:54.0.95.67 功能:接收各个端口发来的数据. 启动方式:进入目录 /usr/local/flume/*bin 在终端运行 ./rece ...

- 用java页面下载图片

try { //根据String形式创建一个URL对象 String filePath = materialProductWorks.getDownloadImageUrl(); URL url = ...

- Hadoop.2.x_MR-Shuffle过程

1.map到reduce中间的一个过程 洗牌,打乱(打乱我们传递的所有元素)(流程:input->map->reduce->output) 2.map()->shuffle-& ...

- springMVC工作机制和框架搭建配置说明

先说一下springMVC的工作机制 1.springmvc把 所有的请求都提交给DispatcherServlet,它会委托应用系统的其他模块负责对请求进行真正的处理工作. 2.Dispatcher ...

- do some projects in macine learning using python

i want to do some projects in macine learning using python help me in this context I don't know if y ...

- 关于JQuery设置checkbox checked 的问题

近日做一个关于JQuery表单验证,有一个比较奇葩的要求,即checkbox是为必填项,textbox不是必填的. 而checkbox与textbox又是相关的,填写了textbox,则其上方的che ...

- Webform——中国省市三级联动以及IsPostBack

首先要明白Webform的运行顺序,当开始启动时候,首先执行的是Page_Load事件, 当点击任意按钮后,每次点击都要先执行一遍Page_Load(在这里Page_Load里面的事件是给数据控件加载 ...

- 关于UGUI Image Sliced模式的一个BUG。

Unity4.6.2f1 在Android/IOS平台下,Image选择Sliced模式,并且对Sprite设置好Border后,会发现并没有按照预计的 情况进行拉伸. 搜了一下是因为Sprite的G ...

- String-自定义功能

<script> /* *发现js中的String对象有限,想要对字符串操作的其他功能. *比如:去除字符串两端的空格.这时只能自.定义 */ //去除字符串两端的空格 function ...