关于testbench

区别与verilog HDL代码,主要留意以下内容:

1,语言本身支持的特征和可综合的代码是两回事,不是所有verilog语言都可以转化为硬件的。

2,testbench作为top module,不需要任何输入和输出。

3,在testbench module中将要测试的模块例化为dut(名字可以任起),input要是reg类型,output要是wire类型,inout是reg。

4,initial和always是同时执行的,只是initial只执行一次。

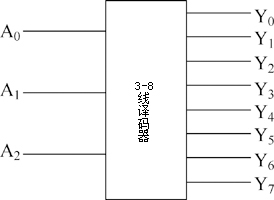

一.38译码器框图

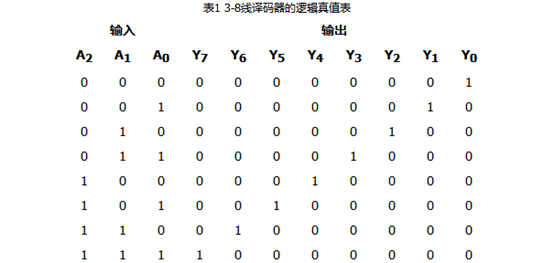

二、真值表

创建工程:

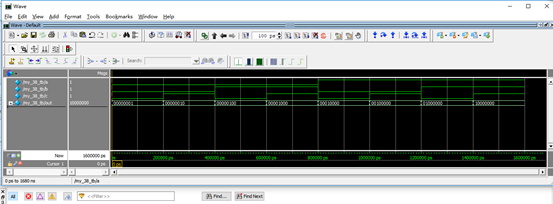

按照真值表定义编写Verilog程序:

module my_38(a,b,c,out);

input a;

input b;

input c;

output reg [7:0]out; //定义一个8位的位宽.只要是在always块中进行赋值的都要定义为reg类型。

always@(a,b,c)

begin

case ({a,b,c}) //{}位为位拼接,将信号拼接成一个三位的信号

3'b000: out=8'b0000_0001;

3'b001: out=8'b0000_0010;

3'b010: out=8'b0000_0100;

3'b011: out=8'b0000_1000;

3'b100: out=8'b0001_0000;

3'b101: out=8'b0010_0000;

3'b110: out=8'b0100_0000;

3'b111: out=8'b1000_0000;

endcase

end

endmodule

编写testbench测试文件:

`timescale 1ns/1ns

module

my38_tb;

reg a,b,c;

wire [7:0]

out my3_8 u1(

.a(a),

.b(b),

.c(c),

.out(out)); //顶层例化

initial begin

a=0;b=0;c=0;

#200;

a=0;b=0;c=1;

#200;

a=0;b=1;c=0;

#200;

a=0;b=1;c=1;

#200;

a=1;b=0;c=0;

#200;

a=1;b=0;c=1;

#200;

a=1;b=1;c=0;

#200;

a=1;b=1;c=1;

#200;

$stop;

end

endmodule

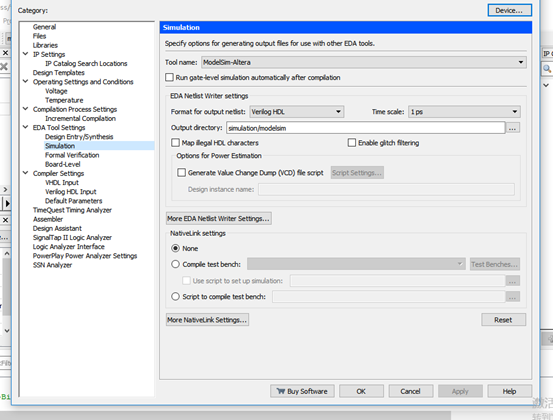

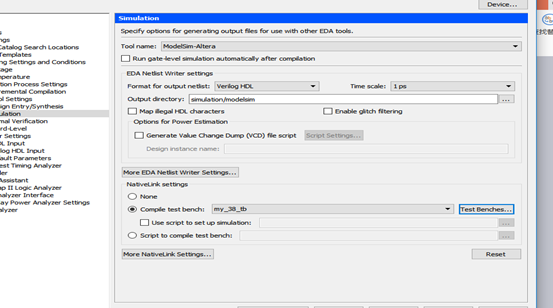

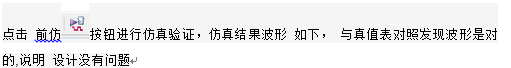

将testbench文件链接到仿真工具

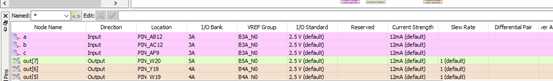

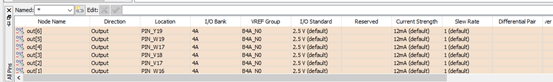

分配引脚

点击全编译按钮后,上电链接开发板,点击programmer,将系统生成的.sof文件烧写到开发板中。

本次实验中,testbench是用initial块给信号赋初值,initial块执行一次,

首先在写testbench时,应注意名称要和自己待仿真的工程名称要对应,比如自己的待仿真文件名称叫my_38,那么对于teshbench的名称则取一个叫my_38_tb,在书写testbench module name则取名叫my_38_tb,这样对于自己有好处,以免自己找不到自己写的文件。

关于testbench的更多相关文章

- UVM Top Testbench

top testbench在top_tb中包含进所有的文件,将DUT放在top_tb中(例化DUT),连接好各个端口,提供clk时钟和rst_n复位信号.最主要的是要给组件中的虚接口设置接口,一般是给 ...

- VHDL TestBench基础(转)

TestBench的主要目标是: 实例化DUT-Design Under Test 为DUT产生激励波形 产生参考输出,并将DUT的输出与参考输出进行比较 提供测试通过或失败的指示 TestBench ...

- VHDL的testbench的编写(转)

大多数硬件设计人员对verilog的testbench比较熟悉,那是因为verilog被设计出来的目的就是为了用于测试使用,也正是因为这样verilog的语法规则才被设计得更像C语言,而verilog ...

- quartus II 自动生成testbench

如果自己不想写这些testbench的这些固定格式,可以在quartus里自动生成testbench文件的模板,然后往里面写信号就行了 步骤:processing->start->star ...

- testbench中将外部数据引入输出的方法(转载)

在进行HDL的仿真测试时,除了用较为直观的波形仿真图像以外,通过编写测试文件testbench进行仿真并将仿真结果保存在对应的文件,显得尤为重要.文件的操作主要用到读和写两种操作. 1. 读操作 读操 ...

- 关于使用ModelSim中编写testbench模板问题

对于初学者来说写Testbench测试文件还是比较困难的,但Modelsim和quartus ii都提供了模板,下面就如何使用Modelsim提供的模板进行操作. Modelsim提供了很多Testb ...

- IIC模块TestBench的书写方法

今天在看黑金AX309FPGA开发板自带教程中的EEPROM那一章,考虑如何写其中iic_com模块的TestBench,难点在于1. 该模块存在一个inout型的端口信号:2. 时序较为复杂,不可能 ...

- Testbench(转)

本来还打算自己写下对Testbench的理解,后来发现百度百科名片解释得很好,所以就直接转了. 原文百度百科链接:http://baike.baidu.com/link?url=dxzsOAs32IE ...

- vcs+Makefile实现简单的testbench

网络上找的文章,实现了一遍. 步骤如下: 1. 创建verilog代码, 包括8位加法器代码和testbench代码. adder8.v module adder8 ( input clk, inpu ...

- Verilog TestBench Coding Style

Abtract 关于编写testbench的一些经验总结心得. Introduction 1.基本的Testbench结构 1)常用的编码结构 `timescale 1 ns / 1 ps ...

随机推荐

- Python带你来一次说走就走的环球旅行

image 1.目 标 场 景 十一长假,相信大部分的朋友这会应该是在全国各地浪或者是在浪的路上,朋友圈成为你们表演的场所. 当然,也有一小戳朋友是选择家里蹲,你们是否感觉到无聊?是否想出去浪,参 ...

- Java8新特性一览表

总览 forEach() method in Iterable interface(Iterable接口中的forEach()方法) default and static methods in Int ...

- matplotlib调整子图大小

因为子图太多而导致每个子图很小,很密,如何调整

- gulp常用插件之bower使用

更多gulp常用插件使用请访问:gulp常用插件汇总 bower这是一款客户端技术的软件包管理器,它可用于搜索.安装和卸载如JavaScript.HTML.CSS之类的网络资源. 更多使用文档请点击访 ...

- A Simple Problem with Integers POJ - 3468 线段树区间修改+区间查询

//add,懒标记,给以当前节点为根的子树中的每一个点加上add(不包含根节点) // #include <cstdio> #include <cstring> #includ ...

- 【大道至简】NetCore3.1快速开发框架一:集成Swagger

在上一章节中,我们创建了基本的框架结构:https://www.cnblogs.com/fuyu-blog/p/12217647.html 下面我们测试接口和集成Swagger接口文档 一.接口测试 ...

- TCP常用拆包处理

1.演示环境为windows 10 1903 2.演示代码 #include "pch.h" #include <iostream> #include <WinS ...

- react 事件传参数

class Demo extends React.Component { click = (a) => (e) => { console.log('额鹅鹅鹅', a, e); } rend ...

- Java期末考试冲刺总结

经过长达将近三个小时的冲刺,我感觉身心俱疲,但它无法掩盖我敲代码的欲望! 三个小时我只实现了公文流转系统的的部分功能. 我深刻的意识到建民老师说的这套关系之复杂,它真的是太复杂了!!!没有系统的梳理, ...

- Wannafly Camp 2020 Day 7K 修炼

搞了半天才发现TMD是个模拟 #include <bits/stdc++.h> using namespace std; #define int long long int x,y,p,q ...