这些年学过的FPGA

这些年学过的FPGA

最近看了老罗的鄙视链是怎样炼成的,联想到FPGA。从2011年底开始接触FPGA到现在已经快接近4个年头了,这四年见证了Altera-FPGA的发展,使用的cyclone系列的芯片也从cyclone到现在cycloneV,从单纯逻辑门,到集成DSP模块,再到现在的集成ARM,工艺技术也从最初的90nm发展到现在的28nm,最小的可以达到14nm(这么高级的芯片目前还没有用过),设计软件也从当初的Quartus II 9.0-- Quartus II 11.0-- Quartus II 13.1-- Quartus II 14.1。

FPGA的角色也慢慢从当初的设计数字电路,到后来也把DSP干的活给干了,再到现在也想把ARM的活给干了。几年前,嵌入式处理器方面,就是三国(ARM、DSP、FPGA)鼎立,FPGA干的最多的也就是协处理,那时大部分人都去学习ARM,学习DSP和FPGA的寥寥无几,没办法,市场所向,市场所需的DSP和FPGA开发人员就是要求少而精,当然那时ARM也是炒得火热,各种培训机构涌现,有种供过欲求的趋势。如今这形势已经变了,ARM器件厂商一般连方案都提供了,市场没必要要那么多的ARM器件开发人员,更多需要的是做上层软件的人员,由此当初大部分ARM器件开发人员更多的就转向了做上层软件和系统软件方面。没办法,市场所向,智能手机出现,需要的更多的是人/物与人/物之间的连接,由此也出现了近两年做应用软件人员越来越多,做ARM、DSP、FPGA器件开发人员越来越少的现象,这情况也是和前几年的情况一样一样的。

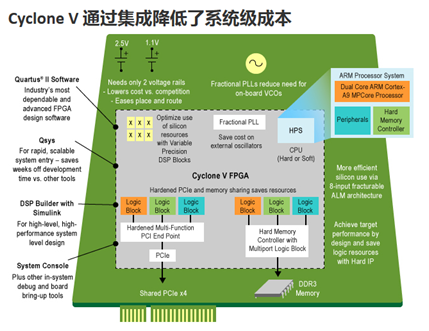

不过,现在的总趋势是电子产品的集成度必须越来越小,一板多芯片的情况也必须改变,变成了现在的一板一芯片,一芯片多核的形势,而SoPC(system on the chip)的特性正好能满足电子产品的集成度越来越高的特点。

下图为2013年Altera和xilinx官网的头条,Altera当年提出的技术蓝图,如今Altera都已经实现了,电子产品更新的速度还是很快的,工艺甚至超过当初设计的发展蓝图,达到了14nm(估计也达到了一个暂时的极限,FPGA的单位面积逻辑门集成度也很高了,所以要在广度上进行扩展),所以也集成了ARM,也能跑跑OpenCL(异构并行计算,当前大数据处理前卫处理方式)。

Altera和xilinx也开始大力推广SoC开发平台,逐渐感觉FPGA开发的软硬件界限越来越模糊了………….

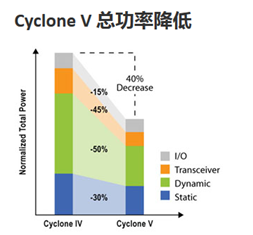

这些年FPGA芯片的发展形势就是:单位面积上逻辑门越来越高、功耗越来越低、硬件集成模块越来越多,芯片价格也越来越实惠(但是相比ARM而言还是贵的),如今感觉FPGA的功耗还是一个问题,再降功耗也是一个很大的难题,Altera在降低功耗可下了大工夫,连电源功耗管理芯片PowerSoC都开始自己做了,看来FPGA的功耗设计还是个很大的难题,没办法集成度、时钟频率、功耗是个矛盾的问题。

芯片功能方面,从cyclone用到如今的cycloneV,感觉单位的逻辑门集成度越来越高,从cyclone到cyclone IV感觉FPGA的变化就是逻辑门集成度、集成DSP 处理模块数量和功耗,基本上没有多大的变化,所以作为一个基础入门FPGA的学习也无须强求一定要最新的cyclone型号,其实内部基本无差,关键还是要掌握基础的逻辑设计规则。但是从cycloneV的S信号型号开始,就开始集成ARM处理器,功能也就实现了一个广度上的扩展,当初的三国鼎立也变成了一家,估计以后懂FPGA的,也要开始学软件、ARM、系统方面的知识了,开发FPGA也要开始面临一个转型,也就是转型到SoCFPGA的开发,更像是一个系统设计。但是FPGA器件开发人员的转型相对较难,因为开发语言没有相通性,FPGA开发所看到的是触发器、锁存器、门电路,逻辑流也是一大堆并行的信号流,而软件开发是串行执行,由当前的处理结果引导到下一个执行动作。

FPGA本身的无奈,虽然能够并行计算、流水线处理,但是有些东西是串行实现的,虽然状态机本身能够实现,但是实现起来也是很复杂的,例如一个iic接口或者是一个SD卡读写操作,这种串行机制非常强的东西,用FPGA就是很不方便了,用状态机的方式实现,估计也要几百上千行的代码,而用C实现的话简单方便。如非必要,还是不要少让FPGA干那些串行机制太强的活,多干些数据搬运的工作。

FPGA应用方面,在通信方面的应用还最为广泛的,但是FPGA承担的角色主要还是高速数据搬移、高速数学运算与数据处理、ASIC/SoC的原型验证。

(http://blog.chinaaet.com/molf/p/35051#)

虽然现在出现了异构并行计算的趋势,但还不是主流,OpenCL也可以实现到FPGA上,在能效上FPGA也比GPU高一到两个数量级,以前运行在GPU上工程也能够移植到FPGA上运行,运行速度方面也有很大的提升,但是其所带来的资源使用率还是个很大的问题,毕竟成本太高,开发难度也上了一个台阶,开发者要掌握的知识量也是很大的(算法层面、器件实现层面、并行计算层面)。异构并行计算国内目前估计没几家在研究,百度在这方面走在了前沿,需要用到更加高级的计算能力来支撑其庞大的业务和大量的数据计算,由此百度开始尝试用FPGA打造AI专有芯片,并成就了第一版AI专有芯片版百度大脑——FPGA版百度大脑。这使得百度成为了全球最早将FPGA规模应用在人工智能领域的公司,也和Altera开启了合作。同时,也有应用于金融超级计算,单纯用超级计算机,需要运行238秒,而在超级计算机中添加 FPGA,运行只需要12秒。但是,目前离FPGA广泛用于异构并行计算还有距离。

对于目前开始火热起来的VR、MR,估计FPGA的应用主要是在前期asic验证或者是作为一个数据协处理器件,毕竟VR和MR面临的是消费类电子产品,成本是关键,ASIC才是VR投向市场的关键所在。

(http://it.people.com.cn/n/2015/1202/c223607-27882640.html)

电子产品朝着一板一芯片,一芯片多核的形势短期之内不会改变,FPGA硬件上该集成的已经集成了,Altera三年前的设计蓝图已经完成,未来如何走向还是很期待。作为FPGA器件开发,要掌握的知识越来越多,面对市场的少而精转变为少而精而全,FPGA的门槛感觉也越来越高,毕竟这个行业发展太快了,所以,从功利的角度上来讲,如果是只是为了找工作的话,应该去选择那些就业概率更大的技术学习。

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

这些年学过的FPGA的更多相关文章

- [转]学DSP、FPGA、ARM,哪个更有前途?

1.这世界真是疯了,貌似有人连FPGA原理是什么都不知道就开始来学习FPGA了. 2.DSP就是一个指令比较独特的处理器.它虽然是通用处理器,但是实际上不怎么“通用”.技术很牛的人可以用DSP做一台电 ...

- 上四条只是我目前总结菜鸟们在学习FPGA时所最容易跑偏的地

长期以来很多新入群的菜鸟们总 是在重复的问一些非常简单但是又让新手困惑不解的问题.作为管理员经常要给这些菜鸟们普及基础知识,但是非常不幸的是很多菜鸟怀着一种浮躁的心态来学习 FPGA,总是急于求成. ...

- V3学院XILINX FPGA寒假班培训感受 江苏大学 电子信息科学与技术 邓普建

事先申明一点,我是大一的学生,因此会站在一个新生的角度叙述. 刚开始接触V3学院是在江苏大学与V3学院合办的FPGA/SOC培训中,那是对全校开放的免费培训,历时三个周末.我那时有幸从头听到了尾,觉得 ...

- verilog实现中值滤波

前言 项目需要,想要实现算法中的其中一步即中值滤波,同时,因为图像处理部分中值滤波相对来说还是比较简单的,将中值滤波的硬件实现作为进入FPGA领域的第一次尝试.虽然说网上有较多关于中值滤波的文档,可是 ...

- 三叔学FPGA系列之二:Cyclone V中的POR、配置、初始化,以及复位

对于FPGA内部的复位,之前一直比较迷,这两天仔细研究官方数据手册,解开了心中的诸多疑惑,感觉自己又进步了呢..... 原创不易,转载请转原文,注明出处,谢谢. 一.关于POR(Power-On ...

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- 【资讯】天啦鲁,这十余款创客设计居然由FPGA搞定 [转]

按理说‘高大上’的FPGA,多出现在航天航空(如火星探测器).通信(如基站.数据中心).测试测量等高端应用场景.但麦迪却也发现,近期,在很多创客的作品内部都有FPGA的影子.这或许也从侧面看出,打从总 ...

- 如何学习FPGA?FPGA学习必备的基础知识

如何学习FPGA?FPGA学习必备的基础知识 时间:2013-08-12 来源:eepw 作者: 关键字:FPGA 基础知识 FPGA已成为现今的技术热点之一,无论学生还是工程师都希望 ...

- FPGA speed grade

Altera的-6.-7.-8速度等级逆向排序,Xilinx速度等级正向排序. 不很严密地说,“序号越低,速度等级越高”这是Altera FPGA的排序方法, “序号越高,速度等级也越高”这是Xili ...

随机推荐

- Oracle a Parameter with multi value

备注:此两种方案,都因为oracle内部字符函数的参数长度4000限制.另外,个人测试,性能不如”将数据插入物理表再JOIN查询“或”每1000次ID做一次IN查询“的总的运行速度. 即ID的个数越 ...

- app上架流程的整理

app的上架流程 一.准备工作 首先需要有开发者账号,企业级的账号是299$,个人开发者账号是99$,没有的话可以登录http://developer.apple.com/自行申请 假如你已经有账号了 ...

- Android 一个对sharedpreferences 数据进行加密的开源库

1.项目地址 https://github.com/iamMehedi/Secured-Preference-Store 2.使用方法 2.1.存数据 //存数据 SecuredPreferenceS ...

- Android项目实战(二十五):Android studio 混淆+打包+验证是否成功

前言: 单挑Android项目,最近即时通讯用到环信,集成sdk的时候 官方有一句 在 ProGuard 文件中加入以下 keep. -keep class com.hyphenate.** {*;} ...

- 【代码笔记】iOS-图文混排(HBLabelDemo)

一,效果图. 二,工程图. 三,代码. ViewController.h #import <UIKit/UIKit.h> @interface ViewController : UIVie ...

- SQL2008中的Sequence

CREATE TABLE dbo.GlobalSequence ( id INT IDENTITY(1, 1) ) GO CREATE PROC seq ( @id INT OUTPU ...

- Redis 支持的5种数据结构

redis的崛起绝非偶然,它确实有自己的新东西在里面,它不像Memcached,只能将数据存储在内存中,它提供了持久化机制和数据同步,避免了宕机后的雪崩的问题,即服务器出现问题后,内存中保留的原始数据 ...

- 0026 Java学习笔记-面向对象-抽象类、接口

抽象方法与抽象类 抽象方法用abstract修饰,没有方法体部分,连花括号都不能有: 抽象方法和抽象类都用abstract修饰 包含抽象方法的类一定是抽象类:但不包含抽象方法的类也可以是抽象类 不能创 ...

- Hive官方手册翻译(Getting Started)

翻译Hive官方文档系列,文中括号中包含 注: 字样的,为我自行标注的,水平有限,翻译不是完美无缺的.如有疑问,请参照Hive官方文档对照查看. 内容列表 Cloudera制作的Hive介绍视频 ...

- Android 上实现像微信一样的用Fragment来实现的Tab切页效果 提供源码下载

网有不少的例子,但是要么是像微信一样可是没有使用Fragment实现,要么是只实现了一个很简单的切换,没有下面的菜单页.这个例子有实现了,我觉得暂时够我用了##实现类:+ MainTabFragmen ...