Verilog中使用'include实现参数化设计

前段时间在FPGA上用Verilog写了一个多端口以太网的数据分发模块,因为每个网口需要独立的MAC地址和IP地址,为了便于后期修改,在设计中使用parameter来定义这些地址和数据总线的位宽等常量。

当时的做法是,顶层模块和子模块中都定义parameter型常数,在顶层模块引用子模块时,通过参数传递改变在被引用子模块中已定义的参数,实现在顶层模块统一管理参数的功能,代码如下

module top(); // 顶层模块

parameter eth1_ip_addr = {'d192, 8'd168, 'd100, 8'd1}; // 以太网1 IP地址 192.168.100.1

parameter eth2_ip_addr = {'d192, 8'd168, 'd100, 8'd2}; // 以太网2 IP地址 192.168.100.2 // 子模块1例化

sub1

#( .ip_addr(eth1_ip_addr) // 参数传递

)

sub1_inst( ); //端口映射 // 子模块2例化

sub2

#( .ip_addr(eth2_ip_addr) // 参数传递

)

sub2_inst( ); //端口映射

子模块1和2分别实现以太网1和2的收发功能,ip_addr为各自的本地IP地址,通过参数传递将eth1_ip_addr和eth2_ip_addr的值分别传递给两个子模块的ip_addr常数。

不过上述方法的缺点在于:

1. 当子模块的参数较多,并且要多次实例化时,代码会显得较为臃肿

2. 假如工程的层次有4层,某个参数只在第4层的模块使用到,为了实现将参数从顶层传递到第4层,第2层和第3层模块的参数列表中必须包含该参数。

解决上述问题有两种方法:

1. 使用defparam命令在顶层模块对子模块中的参数重定义,但是该方法同样存在一个问题:改变已经实例化后的模块中的参数,必须用英文小数点(.)表示层次逻辑关系,如下所示

module top;

reg clk;

reg [:] in1;

reg [:] in2;

wire [:] o1;

wire [:] o2;

// 子模块实例化

vdff m1 (o1, in1, clk);

vdff m2 (o2, in2, clk);

endmodule

// 子模块定义

module vdff (out, in, clk);

parameter size = , delay = ;

input [:size-] in;

input clk;

output [:size-] out;

reg [:size-] out; always @(posedge clk)

# delay out = in;

endmodule

// 参数重定义模块

module annotate;

defparam

top.m1.size = , // size参数的层次化表示

top.m1.delay = ,

top.m2.size = ,

top.m2.delay = ;

endmodule

具体使用方法见http://www.cnblogs.com/hechengfei/p/4116667.html

2. 使用`inculude预处理命令

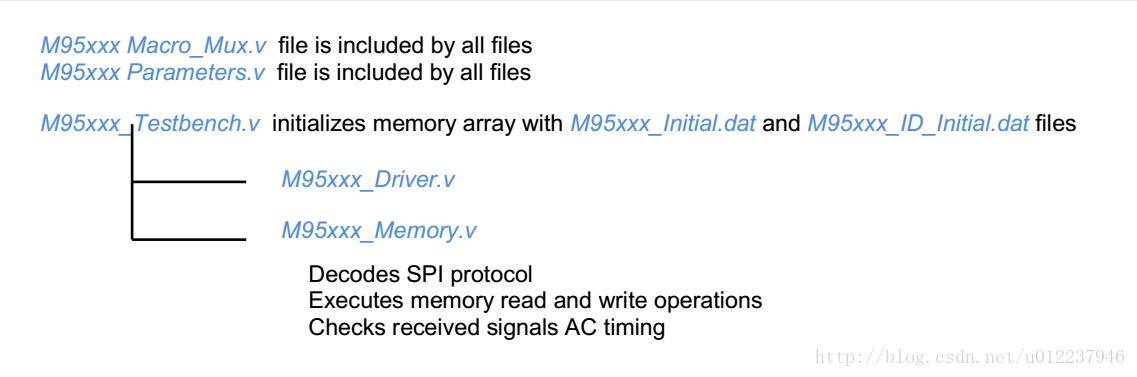

最近在STM官网上找M95xxx系列的EEPROM资料时,看到该芯片的Verilog Testbench模块,如下图所示

M95XXX_Macro_Mux.v:定义M95xxx系列芯片的AC参数

M95XXX_Parameters.v:定义Memory大小、有效地址位数和Page大小等参数

M95xxx_Testbench.v:链接 M95xxx_Driver.v和M95xxx_Memory.v

M95xxx_Driver.v:模拟M95xxx_Memory.v文件基于SPI接口的读写行为

M95xxx_Memory.v:M95xxx EEPROM的行为级描述模型

在上述文件中,M95XXX_Macro_Mux.v和M95XXX_Parameters.v定义了全局参数,被其他文件通过’include命令包含到文件内。具体使用方法如下

M95XXX_Parameters.v 参数定义文件

`define MEM_ADDR_BITS //memory address bits

`define PAGE_ADDR_BITS //page address bits

M95xxx_Driver.v 驱动文件

`include "M95XXX_Parameters.v"

reg[`MEM_ADDR_BITS-:] memory_address;

reg[`PAGE_ADDR_BITS-:] page_address;

可以看到要调用参数文件中参数时,需要:

1. 使用'include命令包含参数文件

2. 使用反引号+参数名的方式来调用该参数

STM MP95xxx系列EEPROM Verilog Testbench模型的链接地址:

https://gitee.com/hombeen/codes/y9rb0g7ej385sipqozvla95

Verilog中使用'include实现参数化设计的更多相关文章

- Verilog语法基础讲解之参数化设计

Verilog语法基础讲解之参数化设计 在Verilog语法中,可以实现参数化设计.所谓参数化设计,就是在一个功能模块中,对于一个常量,其值在不同的应用场合需要设置为不同的置,则将此值在设计时使用 ...

- 【实战】verilog中`define的使用记录

背景: 在最近实战开发中发现:对外部芯片进行初始化时,往往需要定义大量参数. 若直接在module中通过localparam或者parameter进行参数定义的话,会带来两个问题: 1.代码长度增加, ...

- C/C++ 中的include

当需要使用已有的方法或库时, 可以将它们的头文件#include进来. #include会在preprocess过程中被替换成它包含的代码. 头文件中包含了需要使用的函数/变量的声明. 当然声明与定义 ...

- Android在layout xml中使用include

Android include与merge标签使用详解 - shuqiaoniu的博客 - 博客频道 - CSDN.NEThttp://blog.csdn.net/shuqiaoniu/article ...

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- 一段比较有意思的代码——介绍system verilog中的新增幅值语句

system verilog中新加了很多幅值语句,虽然都只适用于阻塞幅值,但是在某些场合中非常实用. 下面是一段有意思的代码,覆盖了一些用法. package definitions; typedef ...

- fatal error C1010: 在查找预编译头时遇到意外的文件结尾。是否忘记了向源中添加“#include "StdAfx.h"”? 解决方法

错误描述: fatal error C1010: 在查找预编译头时遇到意外的文件结尾.是否忘记了向源中添加“#include "StdAfx.h"”? 错误分析: 此错误发 ...

- EF Core 1.0中使用Include的小技巧

(此文章同时发表在本人微信公众号"dotNET每日精华文章",欢迎右边二维码来关注.) 题记:由于EF Core暂时不支持Lazy Loading,所以利用Include来加载额外 ...

随机推荐

- oracle 用户创建、修改、删除

创建用户: create user test identified by test; 修改密码: 1.alter user test identified by mima; 2.passw[ord] ...

- canvas交互部分

mousemove let mouse = { x: undefined, y: undefined, } // 鼠标监听事件,获取鼠标移动的相应坐标 window.addEventListener( ...

- leetCode题解 Student Attendance Record I

1.题目描述 You are given a string representing an attendance record for a student. The record only conta ...

- 分享:将WDCP中的PHP5.2 1.7升级到PHP 5.3的方法

将wdcp中php 5.2.17升级到php 5.3方法: 1.首先下载wdcp php5.3升级脚本 wget http://down.wdlinux.cn/in/php_up53.sh 2.进行安 ...

- 一、Vim编辑器 二、用户和组管理 三、软件的安装(jdk,mysql) 四、Shell编程

一.Vim编辑器的使用 1. vim编辑器的运行模式 编辑模式:等待用户编辑命令的输入 插入模式:编辑文本内容 命令模式:执行命令 2. 使用 :vim 文件名 3. 查看当前vim编辑器介绍:vim ...

- mac osx 升级到10.10 软件无法打开的问题

osx升级到10.9.5 和10.10后,很多软件出现无法打开的问题, This patch seems to be corrupted.Please make sure you get your p ...

- DevExpress01、独立使用的控件

XtraEditors 库提供了只能独立使用的控件,也就是说不能在容器控件的内置编辑中使用它们. 这些控件包括: 几种类型的列表框.数据导航控件.滚动条和一个按钮控件. 这些控件都是 BaseStyl ...

- codeforces 933D A Creative Cutout

题目链接 正解:组合数学. 充满套路与细节的一道题.. 首先我们显然要考虑每个点的贡献(我就不信你能把$f$给筛出来 那么对于一个点$(x,y)$,我们设$L=x^{2}+y^{2}$,那么它的贡献就 ...

- SOJ1022 Uniform Generator

Computer simulations often require random numbers. One way to generate pseudo-random numbers is via ...

- java面向切面编程总结-面向切面的本质

面向切面的本质:定义切面类并将切面类的功能织入到目标类中: 实现方式:将切面应用到目标对象从而创建一个新的代理对象的过程.替换: 使用注解@Aspect来定义一个切面,在切面中定义切入点(@Point ...