verilog 实现DDS

一.DDS的原理

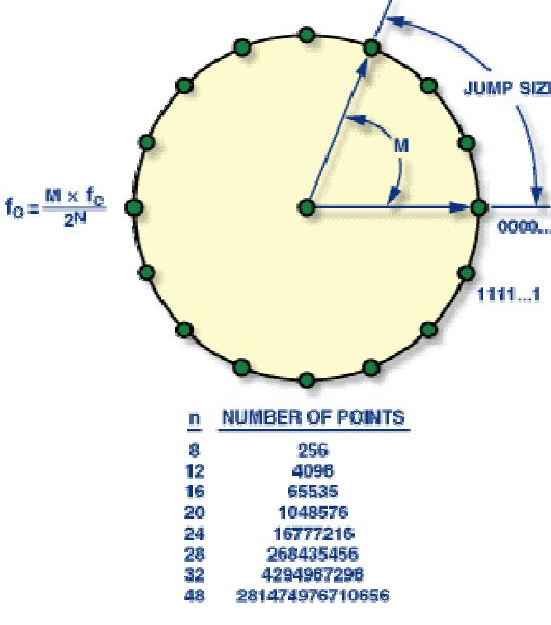

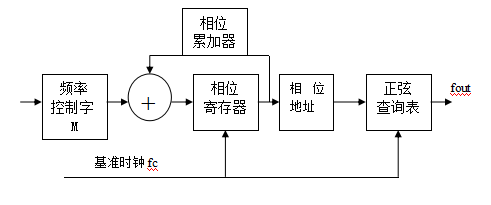

直接数字频率合成器(DDS),功能是通过输入频率输入字从而实现改变输出信号的频率的功能,它所利用的原理就是虽然对于一段正弦信号来说其幅度值是非线性的,但是其相位的值却是线性增加的,如下图所示:DDS的核心公式便脱颖而出

公式中N代表的是频率字输入的位数,当位数越大的时候输出的频率的频率分辨率便会越高,DDS的核心原理也如上图所示:

二.ROM的设计实现

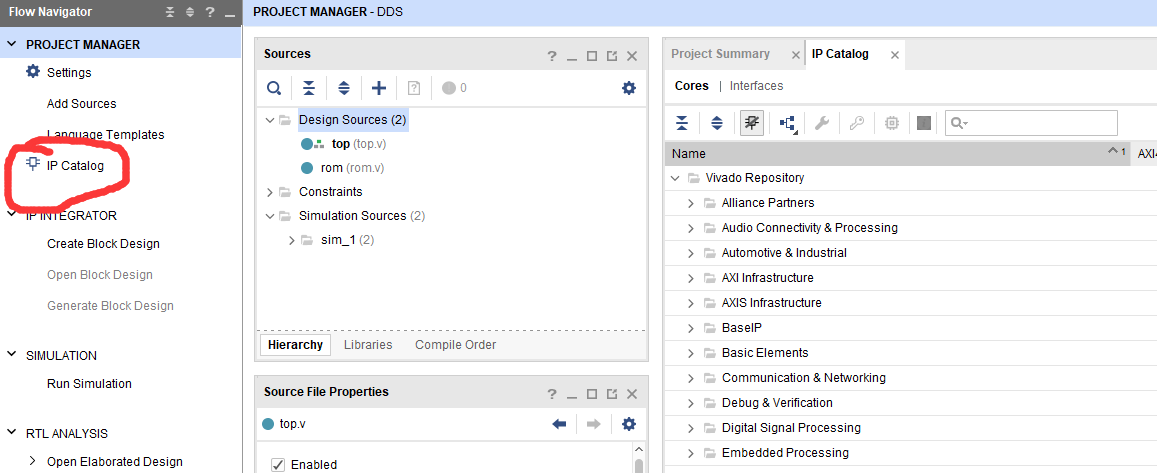

如果仅仅是为了设计方针可以通过$redmem来实现对某一文件的读取,但是为了实现可以综合的系统的设计我们采用如下的采用vivado自带的IP内核来设计,其实实现的过程是非常简单的,我们要完成的最主要的任务就是用vivado(我所使用的开发平台)完成ROM的IP核的配置工作,以及其他的工作即可,那么接下来我们来介绍一下ROM的配置:

首先第一步:(打来项目的IP catalog)

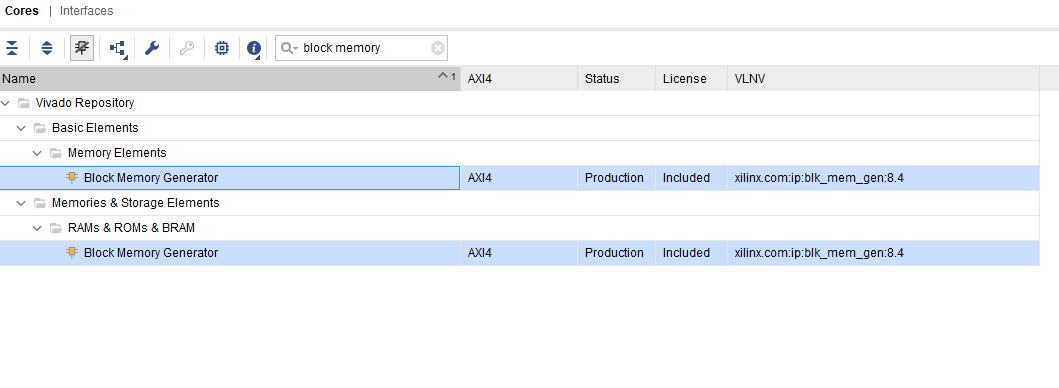

第二步,搜索block memory关键词

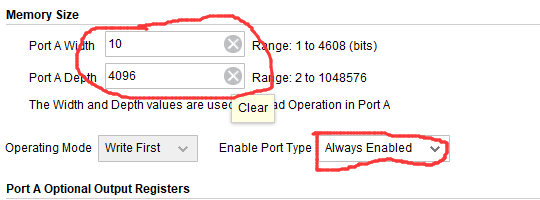

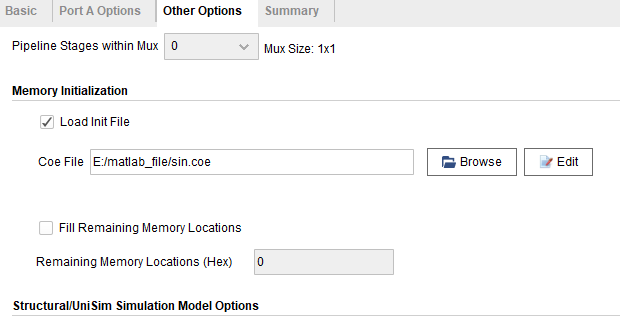

第三步,设置ROM的一些参数,包括其中的存储内容.coe文件以及其数据深度和数据宽度(数据深度指的是:最大可以存储的数据个数,比如12位的数据深度就是可以存储4096个数据。数据宽度指的是:存储数据的位数,即存储的几位数据)

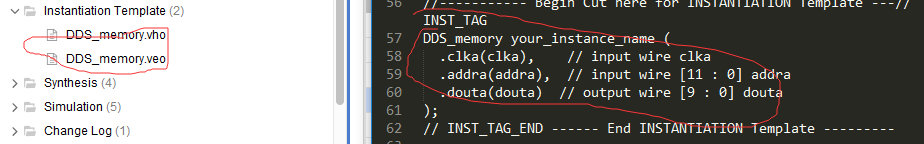

第四步,点击确认生成器件,在器件生成后依旧可以对器件进行修改,我们可以通过以下操作来引用ROM模块(右边是在sourses的IP sources的)。

三..coe文件的生成

move=2^12;

%先生成文件,和头格式

fid = fopen('all.coe','w');

fprintf(fid,'MEMORY_INITIALIZATION_RADIX=10;\n');

fprintf(fid,'MEMORY_INITIALIZATION_VECTOR=\n');

%先写入sin函数值地址0~4095

t=0:2*pi/2^12:2*pi;

y=0.5*sin(t)+0.5;

r=ceil(y*(2^8-1)); %将小数转换为整数,ceil是向上取整。

for i = 1:1:2^12

fprintf(fid,'%d',r(i));

fprintf(fid,',');

if i%15==0

fprintf(fid,'\n');

end

end

%下面写入方波

t=1:1:2^12;

y=(t<=2047);

r=ceil(y*(2^8-1));

for i = 1:1:2^12

fprintf(fid,'%d',r(i));

fprintf(fid,',');

if i%15==0

fprintf(fid,'\n');

end

end

%最后写入三角波

t=1:1:2^12;

y=[0.5:0.5/1024:1-0.5/1024, 1-0.5/1024:-0.5/1024:0, 0.5/1024:0.5/1024:0.5];

r=ceil(y*(2^8-1));

for i = 1:1:2^12

fprintf(fid,'%d',r(i));

if i==2^12

fprintf(fid,';');

else

fprintf(fid,',');

end

if i%15==0

fprintf(fid,'\n');

end

end

fclose(fid);

以上是正弦波,方波以及三角波的形成matlab代码

四.verilog代码的编写

module top#(parameter move=4096)(

input [13:0]fw,//

input clk,//

input reset,// output [9:0]out

); reg [14:0]phase;

reg [13:0] relat;

wire [13:0] addr; always@(posedge clk or negedge reset)

begin

if(!reset)

begin

phase<=0;

relat<=0;

end

else

begin

if((fw>=move))

begin

if(fw>=2*move) relat=fw-2*move;

else relat=fw-move;

end

else relat=fw;

phase=((phase+relat)>12'd4095)?0:(phase+relat);

end

end assign addr=phase+(fw-relat); rom r(.clk(clk),.phase(addr),.out(out)); endmodule

在波形设置的窗口可以设置模拟数字波形,这里还要注意的一点是如果要显示方波一定在模拟波形的设置里面的hold勾上,因为verilog默认是线性画图。

verilog 实现DDS的更多相关文章

- 用verilog模拟DDS产生正弦波信号

前言: DDS:直接数字频率合成,正弦波0-2pi周期内,相位到幅度是一一对应的(这里我们使用放大后的整数幅度). 主要思路: 个人理解,FPGA不擅长直接做数字信号计算,那样太占用片上逻辑资源,所以 ...

- 彻底理解DDS(信号发生器)的fpga实现(verilog设计代码)

DDS(Direct Digital Synthesis)是一种把一系列数字信号通过D/A转换器转换成模拟信号的数字合成技术. 它有查表法和计算法两种基本合成方法.在这里主要记录DDS查表法的fpga ...

- 【仿真】【modelsim】:verilog功能仿真流程

一.编写verilog源文件,在diamond中编译.编写testbench文件.在diamond设置中将仿真工具设置为modelsim,运行仿真向导 二.自动进入modelsim, 编译全部 运行仿 ...

- ROM存储1/4周期正弦信号构造DDS

上周的时候,老师让编写一个简单的dds程序,本文说明了整个过程中我遇到问题以及一些个人的思考.初次接触FPGA,如有问题请多多指教~ 1.几个疑问,解决和没有解决的. 为何采用ROM而不是直接采用DD ...

- FPGA学习笔记. DDS

DDS原理 直接数字式频率合成器(Direct Digital Synthesizer) 频率计算公式 Fout = FW * Fclk / 2^N Fout 输出频率, Fw 频率控制字, N 位数 ...

- psoc做dds

今天用psoc做了dds,现在总结一下. 1dds用到的相位累加器是用verilog写的,本来准备用一下datapath,这是和fpga不一样的一点,用了类似alu的结构,但是看手册后发现,虽然可以执 ...

- 国产CPLD(AGM1280)试用记录——做个SPI接口的任意波形DDS [原创www.cnblogs.com/helesheng]

我之前用过的CPLD有Altera公司的MAX和MAX-II系列,主要有两个优点:1.程序存储在片上Flash,上电即行,保密性高.2.CPLD器件规模小,成本和功耗低,时序不收敛情况也不容易出现.缺 ...

- Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi.Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号.列表有: Xi Yi Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 ...

- Verilog HDL模型的不同抽象级别

所谓不同的抽象类别,实际上是指同一个物理电路,可以在不同层次上用Verilog语言来描述.如果只从行为功能的角度来描述某一电路模块,就称作行为模块.如果从电路结构的角度来描述该电路模块,就称作结构模块 ...

随机推荐

- FAQ_1

FAQ LoadRunner录制脚本时为什么不弹出IE浏览器? 当一台主机上安装多个浏览器时,LoadRunner录制脚本经常遇到不能打开浏览器的情况,可以用下面的方法来解决. 启动浏览器,打开Int ...

- 【转】一次HBase问题的解决过程(Status: INCONSISTENT)

[From]https://www.cnblogs.com/quchunhui/p/9583746.html ==版本信息== HBase:2.7.1 Storm:1.0.1 RocketMQ:3.4 ...

- Aes加密/解密示例项目

#AesEncrypt:Aes加密/解密示例项目 <br> 附件中的“AesEncrypt.zip”是本项目的exe文件,可直接下载下来运行和查看. *高级加密标准(英语:Advanced ...

- Win10黑色白色主题切换

打开设置面板 选择个性化 -> 颜色 -> 选择默认应用模式 然后选择亮和暗就好了. (这还是看404说的我才知道.)

- Flume入门案例

首先需要通过一个配置文件来配置Agent. 通过flume提供的工具启动agent就可以工作了. (1)编写配置文件 #example.conf:单节点Flume配置 #命名Agent a1的组件 ...

- 1.docker 慕课入门

本文是学习慕课网的实战https://www.imooc.com/learn/824 同时结合菜鸟教程的思想https://www.runoob.com/docker/docker-architec ...

- 使用PowerShell 自动创建DFS命名空间服务器

运行环境:Windows Server 2012 R2 DFS命名空间概述 DFS命名空间 PowerShell脚本命令 Writing PowerShell DFS Scripts: Managin ...

- PHP反序列化进阶寻找和构造

POP链的构造 如果关键代码不在魔术方法中,而是在一个类的普通方法中. 这时候可以通过寻找相同的函数名将类的属性和敏感函数的属性联系起来 <?phpclass lemon { protec ...

- pikachu-SQL注入

参考网址: http://www.mamicode.com/info-detail-2795438.html

- 格式化hdfs以及namnode没启动

先stop-all.sh 删除hdfs-site.xml中的这两个目录 然后删除core-site.xml 中的这个目录 然后格式化hdfs hdfs namenode -format 即可启动成功 ...