CPU缓存一致性协议—MESI详解

MESI(也称伊利诺斯协议)是一种广泛使用的支持写回策略的缓存一致性协议,该协议被应用在Intel奔腾系列的CPU中。

MESI协议中的状态

CPU中每个缓存行使用的4种状态进行标记(使用额外的两位bit表示)

| 状态 | 描述 |

| M(Modified) | 这行数据有效,数据被修改了,和内存中的数据不一样,数据只存在于本cache中。 |

| E(Exclusive) | 这行数据有效,数据和内存中的数据一致,数据只存下于本Cache中 |

| S(Shared) | 这行数据有效,数据和内存中的数据一致,数据存在于很多cache中 |

| I(Invalid) | 这行数据无效 |

M和E的数据都是本core独有的,不同之处是M状态的数据是dirty(和内存中的不一致),E状态的数据是clean(和内存中的一致)

S状态是所有Core的数据都是共享的,只有clean的数据才能被多个core共享

I表示这个Cache line无效

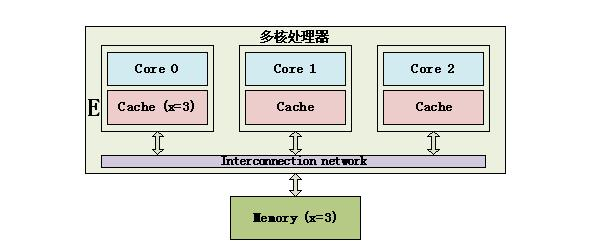

E状态

只有Core 0访问变量x,它的Cache line状态为E(Exclusive)。

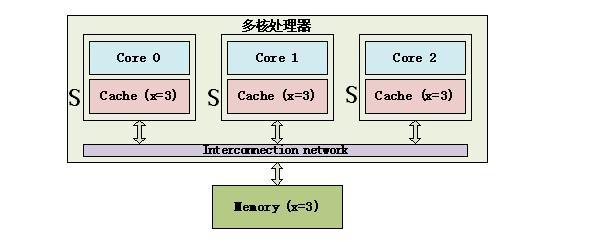

S状态

3个Core都访问变量x,它们对应的Cache line为S(Shared)状态。

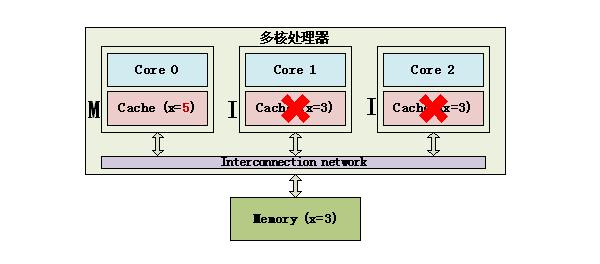

M状态和<I>状态之间的转化

Core 0修改了x的值之后,这个Cache line变成了M(Modified)状态,其他Core对应的Cache line变成了I(Invalid)状态

在MESI协议中,每个Cache的Cache控制器不仅知道自己的读写操作,而且也监听(snoop)其它Cache的读写操作。每个Cache line所处的状态根据本核和其它核的读写操作在4个状态间进行迁移

Local Read表示本内核读本Cache中的值,Local Write表示本内核写本Cache中的值,Remote Read表示其它内核读其它Cache中的值,Remote Write表示其它内核写其它Cache中的值,箭头表示本Cache line状态的迁移,环形箭头表示状态不变。 当内核需要访问的数据不在本Cache中,而其它Cache有这份数据的备份时,本Cache既可以从内存中导入数据,也可以从其它Cache中导入数据,不同的处理器会有不同的选择。MESI协议为了使自己更加通用,没有定义这些细节,只定义了状态之间的迁移,下面的描述假设本Cache从内存中导入数据.

MESI状态之间的迁移过程如下:

|

当前状态 |

事件 |

行为 |

下一个状态 |

|

I(Invalid) |

Local Read |

如果其它Cache没有这份数据,本Cache从内存中取数据,Cache line状态变成E; 如果其它Cache有这份数据,且状态为M,则将数据更新到内存,本Cache再从内存中取数据,2个Cache 的Cache line状态都变成S; 如果其它Cache有这份数据,且状态为S或者E,本Cache从内存中取数据,这些Cache 的Cache line状态都变成S |

E/S |

|

Local Write |

从内存中取数据,在Cache中修改,状态变成M; 如果其它Cache有这份数据,且状态为M,则要先将数据更新到内存; 如果其它Cache有这份数据,则其它Cache的Cache line状态变成I |

M |

|

|

Remote Read |

既然是Invalid,别的核的操作与它无关 |

I |

|

|

Remote Write |

既然是Invalid,别的核的操作与它无关 |

I |

|

|

E(Exclusive) |

Local Read |

从Cache中取数据,状态不变 |

E |

|

Local Write |

修改Cache中的数据,状态变成M |

M |

|

|

Remote Read |

数据和其它核共用,状态变成了S |

S |

|

|

Remote Write |

数据被修改,本Cache line不能再使用,状态变成I |

I |

|

|

S(Shared) |

Local Read |

从Cache中取数据,状态不变 |

S |

|

Local Write |

修改Cache中的数据,状态变成M, 其它核共享的Cache line状态变成I |

M |

|

|

Remote Read |

状态不变 |

S |

|

|

Remote Write |

数据被修改,本Cache line不能再使用,状态变成I |

I |

|

|

M(Modified) |

Local Read |

从Cache中取数据,状态不变 |

M |

|

Local Write |

修改Cache中的数据,状态不变 |

M |

|

|

Remote Read |

这行数据被写到内存中,使其它核能使用到最新的数据,状态变成S |

S |

|

|

Remote Write |

这行数据被写到内存中,使其它核能使用到最新的数据,由于其它核会修改这行数据, 状态变成I |

I |

MESI状态迁移

AMD的Opteron处理器使用从MESI中演化出的MOESI协议,O(Owned)是MESI中S和M的一个合体,表示本Cache line被修改,和内存中的数据不一致,不过其它的核可以有这份数据的拷贝,状态为S。

Intel的core i7处理器使用从MESI中演化出的MESIF协议,F(Forward)从Share中演化而来,一个Cache line如果是Forward状态,它可以把数据直接传给其它内核的Cache,而Share则不能。

CPU缓存一致性协议—MESI详解的更多相关文章

- 并发研究之CPU缓存一致性协议(MESI)

CPU缓存一致性协议MESI CPU高速缓存(Cache Memory) CPU为何要有高速缓存 CPU在摩尔定律的指导下以每18个月翻一番的速度在发展,然而内存和硬盘的发展速度远远不及CPU.这就造 ...

- C和C++中的volatile、内存屏障和CPU缓存一致性协议MESI

目录 1. 前言2 2. 结论2 3. volatile应用场景3 4. 内存屏障(Memory Barrier)4 5. setjmp和longjmp4 1) 结果1(非优化编译:g++ -g -o ...

- 一篇文章让你明白CPU缓存一致性协议MESI

CPU高速缓存(Cache Memory) CPU为何要有高速缓存 CPU在摩尔定律的指导下以每18个月翻一番的速度在发展,然而内存和硬盘的发展速度远远不及CPU.这就造成了高性能能的内存和硬盘价格及 ...

- Java内存模型(二)volatile底层实现(CPU的缓存一致性协议MESI)

CPU的缓存一致性协议MESI 在多核CPU中,内存中的数据会在多个核心中存在数据副本,某一个核心发生修改操作,就产生了数据不一致的问题,而一致性协议正是用于保证多个CPU cache之间缓存共享数据 ...

- CPU缓存一致性协议与java中的volatile关键字

有关缓存一致性协议MESI自行百度. 提出问题:volatile在缓存一致性协议上又做了哪些事情?为啥它不保证原子性? 在缓存一致性协议下,CPU为了执行效率使用了写(存储)缓存和失效队列从而导致对用 ...

- 多线程之:MESI-CPU缓存一致性协议

MESI(Modified Exclusive Shared Or Invalid)(也称为伊利诺斯协议,是因为该协议由伊利诺斯州立大学提出)是一种广泛使用的支持写回策略的缓存一致性协议,该协议被应用 ...

- MESI-CPU缓存一致性协议

转http://blog.csdn.net/realxie/article/details/7317630 http://en.wikipedia.org/wiki/MESI_protocol MES ...

- 缓存一致性协议 mesi

m : modified e : exlusive s : shared i : invalid 四种状态的转换略过,现在讨论为什么有了这个协议,i++在多线程上还不是安全的. 两个cpu A B同时 ...

- 各大中间件底层技术-分布式一致性协议 Raft 详解

前言 正式介绍 Raft 协议之前,我们先来举个职场产研团队的一个例子

随机推荐

- JavaScript ES6 核心功能一览

JavaScript 在过去几年里发生了很大的变化.这里介绍 12 个你马上就能用的新功能. JavaScript 历史 新的语言规范被称作 ECMAScript 6.也称为 ES6 或 ES2015 ...

- react-native中的props

效果图 大多数组件在创建时就可以使用各种参数来进行定制.用于定制的这些参数就称为props(属性). 以常见的基础组件Image为例,在创建一个图片时,可以传入一个名为source的 prop 来指定 ...

- 第四篇-以ConstraintLayout进行Android界面设计

此文章基于第三篇. 一.新建一个layout.xml文件,创建方法不再赘述,在Design界面右击LinearLayout,点击Convert LinearLayout to ConstraintLa ...

- 团体程序设计天梯赛(CCCC) L3012 水果忍者 上凸或下凹的证明

团体程序设计天梯赛代码.体现代码技巧,比赛技巧. https://github.com/congmingyige/cccc_code #include <cstdio> #include ...

- POJ 1236 Network of Schools (Tarjan)

Network of Schools Time Limit: 1000MS Memory Limit: 10000K Total Submissions: 22745 Accepted: 89 ...

- 创建免密码sudo用户

创建免密码sudo用户 #!/bin/bash c1=`grep -w 'bkuser' /etc/passwd | wc -l` ]; then echo "bkuser已经存在" ...

- vue的一些小坑

1.$refs使用时机 尝试在watch的时候使用$refs,发现里面都是空的,然后google了一下,$refs需要在整个组件挂载完成后才能使用 解决方法:使用setTimeout setTImeo ...

- java8的Streams

首先看一个问题:在这个task集合中一共有多少个OPEN状态的?计算出它们的points属性和.在Java 8之前,要解决这个问题,则需要使用foreach循环遍历task集合:但是在Java 8中可 ...

- centos 6.5 ruby环境安装

redis3.0以上支持集群,自带集群管理工具redis-trib.rb:在搭建集群前,安装ruby环境 ruby安装包下载 安装开发工具 1.命令:yum groupinstall "De ...

- SSRF漏洞分析与利用

转自:http://www.4o4notfound.org/index.php/archives/33/ 前言:总结了一些常见的姿势,以PHP为例,先上一张脑图,划√的是本文接下来实际操作的 0x01 ...