基于FPGA的DW8051移植(三)

总结一下问题:

1) http://www.cnblogs.com/sepeng/p/4137405.html 基于FPGA的DW8051移植(一)里面用modelsim观测波形发现程序进入了idata区间初始化循环中跳转不出来,没有进入用户程序这一块。

2) http://www.cnblogs.com/sepeng/p/4141072.html 基于FPGA的DW8051移植(二)里面将idata区间初始化去掉,程序进入了用户程序却发现在执行DelayMs 函数的时候,循环执行完毕,在最后跳转回主函数main的时候居然跳进了for循环。

这一篇我将会去掉for循环再追查核的执行情况

#include <reg51.h>

#define uchar unsigned char

#define uint unsigned int sbit LED = P0^ ; void DelayMS (uint x )

{

//uchar i ;

while (x--);

//{

//for (i=0;i<2;i++) ; //}

} void main ()

{

LED = ;

while ()

{ DelayMS();

LED=~LED ;

}

}

这一次的执行情况依据keilC里面的调试,执行地址顺序应该是

00 01 02 --> 1B 1C 1D --> 1E 1F 20(头文件执行完成)

-->(进入主函数) 03 04 --> 05 06 --> 07 08 --> 09 0A 0B(开始向子函数转跳)

-->(进入子函数)10 -->11 --> 12 13 --> 14 15 ()--> 17 --> 18 19 -->(跳回子函数循环)

10 .....(这里循环五次)

--> (最后一次)10 --11 -->12 13 --> 14 15 --> 16 --> 17 --> 18 19 --> 1A(子函数执行完毕)

--> (回到主函数) 0C 0D --> 0E 0F --> 05 06 --> 07 08 --> 09 0A 0B (向子函数跳转)

--> ...............循环

在modelsim中看到指令执行错误,上面红色字体的地方执行错误,错误方式就是每次多读了一个数据。

正常 :09 0A 0B(开始向子函数转跳) 实际 : 09 0A 0B 0C

正常 : 14 15 () 实际 : 14 15 16

正常 :18 19 -->(跳回子函数循环) 实际 : 18 19 1A

这三个地方有一个共同的特点就是需要跳转。

既然如此就第三次回避(第一次回避memory初始化loop,第二次回避for )修改C程序如下,回避子函数的转跳行为

#include <reg51.h> sbit LED = P1^ ; void main ()

{

LED = ; while ()

LED=~LED ; }

可是这主函数main里面必须要有一个循环啊,所以loop还是无法避免,最终的地址跳转为

00 01 02 --> 03 04 05 --> 06 07 08 (初始化运行完毕)

(进入主函数)09 0A --> 0B 0C --> 0D 0E (主函数运行完毕)

(循环)0B 0C --> 0D 0E (循环)

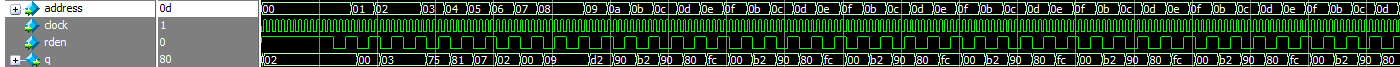

从modelsim中看到这个核运行的情况是

每次跳转的前一个时刻0D 0E 都执行成0D 0E 0F 。就是多执行了一条语句,语句地址0F

在让我们看看我关心已久的sfr

前面的01 81 00 我真是醉了,81可是P0^1啊,无法解释,后面的90 倒是符合期望,问题又来了,这个data_out 怎么又不听话了呢?

抓狂,核你到底怎么了

下午仔细的去看datasheet,发现在Application Software Compatibility 这一章节里面有这么一句话: However, becausethe DW8051 usesa different instruction timing than the standard 8051, code with timing loops may require modification.

新思你丫的到底是个什么意思,出现了timing loop 就需要修改代码,但是没有说如何修改。我的所有的程序中都有循环,难道意思就是说应用程序中有了loop就有问题吗,如果是这样那岂不是在代码中故意埋了个地雷

mmd 这半个月岂不是白忙活了

基于FPGA的DW8051移植(三)的更多相关文章

- 基于FPGA的DW8051移植(一)

最近 半个月都在移植8051,看到DW8051内核资料比较齐全又是新思发布的,所以就开始玩弄 可是这半个月的努力几近白费 —— 移植失败了,不知道从何着手这个内核.可能大家能找到不同的版本,我的是最初 ...

- 基于FPGA的DW8051移植(二)

基于上一篇博文继续,本来想换到oc8051,但是还是不甘心,弄了这么久还是没有弄出来,真是打击屎了. 上一篇说3f进入了operation code所以判断是代码错误,后来发现不可以这么判断. 因为地 ...

- 基于FPGA的HDMI显示设计(三)

上一篇:基于FPGA的VGA显示设计(二) 10月10日 ~ 20日期间实习,令我万万没想到的是实习题目是 “便携式高清电视显示屏测试系统原型设计” 也就是 “基于FPGA的视频显示”. 实习要求用 ...

- 基于FPGA的RGB565_YCbCr_Gray算法实现

前面我们讲了基于FPGA用VGA显示一副静态图片,那么接下来我们就接着前面的工程来实现我们图像处理的基础算法里最简单的一个那就是彩色图像转灰度的实现. 将彩色图像转化为灰度的方法有两种,一个是令RGB ...

- 基于FPGA的中值滤波算法实现

在这一篇开篇之前,我需要解决一个问题,上一篇我们实现了基于FPGA的均值滤波算法的实现,最后的显示效果图上发现有一些黑白色的斑点,我以为是椒盐噪声,然后在做基于FPGA的中值滤波算法的实验时,我发现黑 ...

- 基于FPGA的肤色识别算法实现

大家好,给大家介绍一下,这是基于FPGA的肤色识别算法实现. 我们今天这篇文章有两个内容一是实现基于FPGA的彩色图片转灰度实现,然后在这个基础上实现基于FPGA的肤色检测算法实现. 将彩色图像转化为 ...

- PCIE_DMA实例四:xapp1052在Xilinx 7系列(KC705/VC709)FPGA上的移植

PCIE_DMA实例四:xapp1052在Xilinx 7系列(KC705/VC709)FPGA上的移植 一:前言 这段时间有个朋友加微信请求帮忙调试一块PCIe采集卡.该采集卡使用xilinx xc ...

- 基于FPGA的VGA可移植模块终极设计【转】

本文转载自:http://www.cnblogs.com/lueguo/p/3373643.html 略过天涯 基于FPGA的VGA可移植模块终极设计 一.VGA的诱惑 首先,VGA的驱动,这事, ...

- 基于FPGA的图像开发平台 其他摄像头附件说明(OV5642 OV9655)

基于FPGA的图像开发平台 其他摄像头附件说明 FPGA_VIP_V101 编者 奇迹再现 个人博客 http://www.cnblogs.com/ccjt/ 联系邮箱 Shenyae86@163.c ...

随机推荐

- NET Core Docker部署

NET Core Docker部署 前言 在前面文章中,介绍了 ASP.NET Core在 macOS,Linux 上基于Nginx和Jexus的发布和部署,本篇文章主要是如何在Docker容器中运行 ...

- 用javascirpt画个太极

偶然看到用代码画太极,感觉很有趣,用JS写了一个 过程很简单,画了张图,应该一看就懂了 代码也很简单,如下,注释很多 function TaiJi(r,canvas){ this.r = r; thi ...

- UUID Gen

https://github.com/twitter/snowflake/releases/tag/snowflake-2010 http://boundary.com/blog/2012/01/12 ...

- protel99_拼板详细图解

首先打开PCB文档.如图所示,在PCB左下角放置一個坐標為X=0,Y=0的焊盤. 从下图看,为了方便电路板生产厂家的加工和焊接工厂的加工,拼版的方向是向上Y轴方向拼版. 接着为了在拼版过程中好对齐板边 ...

- Trie三兄弟——标准Trie、压缩Trie、后缀Trie

1.Trie导引 Trie树是一种基于树的数据结构,又称单词查找树.前缀树,字典树,是一种哈希树的变种.应用于字符串的统计与排序,经常被搜索引擎系统用于文本词频统计.用于存储字符串以便支持快速模式匹配 ...

- oracle数据类型和对应的java类型

由于 实体类里面 使用的是 double ,生成的Oracle 用的JDBC 类型为java.sql.Types.FLOAT 所以Oracle 数据类型为 float. 如果想保留两位小数 实体类 ...

- C标准函数库中获取时间与日期、对时间与日期数据操作及格式化

表示时间的三种数据类型[编辑] 日历时间(calendar time),是从一个标准时间点(epoch)到现在的时间经过的秒数,不包括插入闰秒对时间的调整.开始计时的标准时间点,各种编译器一般使用19 ...

- Network of Schools(强连通分量+缩点) (问添加几个点最少点是所有点连接+添加最少边使图强连通)

Network of Schools Time Limit: 1000MS Memory Limit: 10000K Total Submissions: 13801 Accepted: 55 ...

- [置顶] Asp.Net底层原理(二、写自己的Asp.Net框架)

我们介绍过了浏览器和服务器之间的交互过程,接下来介绍Asp.net处理动态请求. 写自己的Asp.Net框架,我们不会引用System.Web这个程序集,我们只需要创建要给自己的类库,所以在接下来的程 ...

- STL之使用vector排序

应用场景: 在内存中维持一个有序的vector: // VectorSort.cpp : Defines the entry point for the console application. #i ...