【第一季】CH07_FPGA_RunLED创建VIVADO工程实验

【第一季】CH07_FPGA_RunLED创建VIVADO工程实验

7.1 硬件图片

先来熟悉一下开发板的硬件:LED部分及按钮部分

7.2 硬件原理图

PIN脚定义(讲解以MIZ702讲解,MIZ701N只有4个LED 2个按钮):

|

GCLK:Y9(PL输入时钟) LD0:T22 LD1:T21 LD2:U22 LD3:U21 LD4:V22 LD5:W22 LD6:U19 LD7:U14 |

BTNU:T18 BTNC:P16 BTNL:N15 BTNR:R18 BTND:R16 |

7.3新建VIVADO工程

Step1:创建工程

Step2:欢迎界面直接单击NEXT

Step3:工程名字命名为Led,并且设置保存的路径,单击NEXT

Step4:新建一个RTL 工程,并且勾选不要添加源文件,单击NEXT

Step5:由于MIZ702和ZEDBOARD是兼容的,因此直接选择ZEDBOARD硬件开发包作为我们MIZ702的开发包。这样可以省去很多麻烦,达到事半功倍的目的。单击NEXT

Step6:最后单击Finish 完成工程的创建

7.4创建工程文件

Step1:打开VIVADO软件

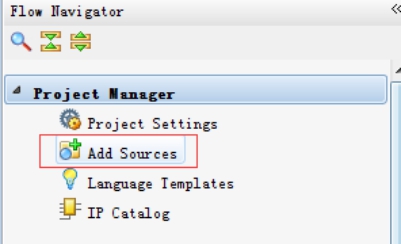

Step2:单击 Add Sources

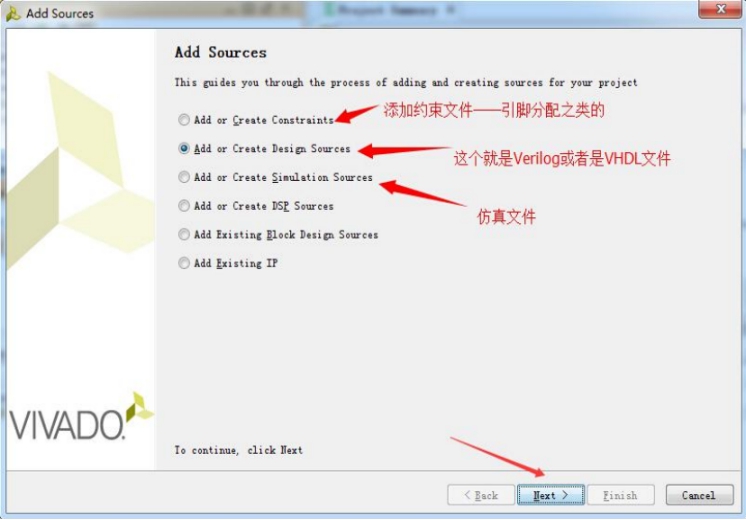

Step4:选择单击Add or Create Design Sources 然后单击NEXT

Step5:单击Create File 来创建文件

Step6:创建一个Led的文件,并且文件类型选择Verilog

Step7:添加完成后如下图所示之后单击finish完成文件的创建

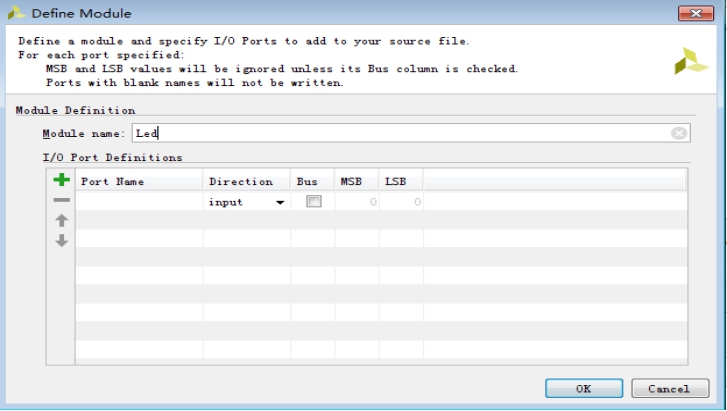

Step8:继续弹出的对话空中,可以设置一些端口,但是我们现在什么都不做。单击OK

Step9:创建完成后可以看到Design Sources文件夹中有了Led.v这个文件

Step9:创建完成后可以看到Design Sources文件夹中有了Led.v这个文件,这个文件就是我们可以编写verilog程序的文件。

7.5 Verilog FPGA流水灯实验

Step1:双击Led.v打开流水程序源码如下

|

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // Create Date: 2016/03/22 15:05:39 // Design Name: // Module Name: Led // Project Name: // Target Devices: // Tool Versions: // Description: // Dependencies: // Revision: // Revision 0.01 - File Created // Additional Comments: ////////////////////////////////////////////////////////////////////////////////// module Led( ); endmodule |

可以看出这是一个空的工程,我们现在要添加代码同时也要添加工程信息。

Step2:编写程序并且添加工程信息

|

// Target Devices: XC7Z020-FGG484 // Tool versions: VIVADO2015.4 // Description: water led // Revision: V1.1 // Additional Comments: //1) _i PIN input //2) _o PIN output //3) _n PIN active low //4) _dg debug signal //5) _r reg delay //6) _s state machine ////////////////////////////////////////////////////////////////////////////// module Led( input CLK_i, input RSTn_i, output reg [7:0]LED_o ); reg [31:0]C0; always @(posedge CLK_i) if(!RSTn_i) begin LED_o <= 8'b0000_0001; C0 <= 32'h0; end else begin if(C0 == 32'd50_000_000) begin C0 <= 32'h0; if(LED_o == 8'b1000_0000) LED_o <= 8'b0000_0001; else LED_o <= LED_o << 1; end else begin C0 <= C0 + 1'b1; LED_o <= LED_o; end end endmodule |

这样我们就编写好了代码下面还要添加管脚约束文件。

7.6 添加管脚约束文件

Step1:单击 (和添加.v文件一样)

(和添加.v文件一样)

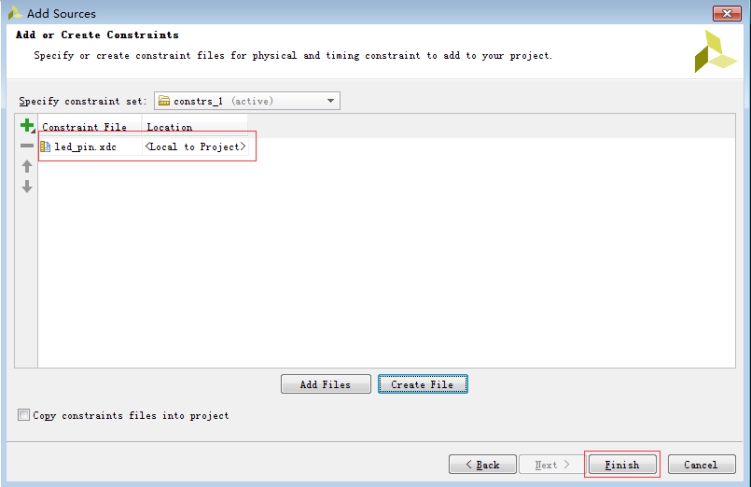

Step2:选择Add or create constraints 然后单击NEXT

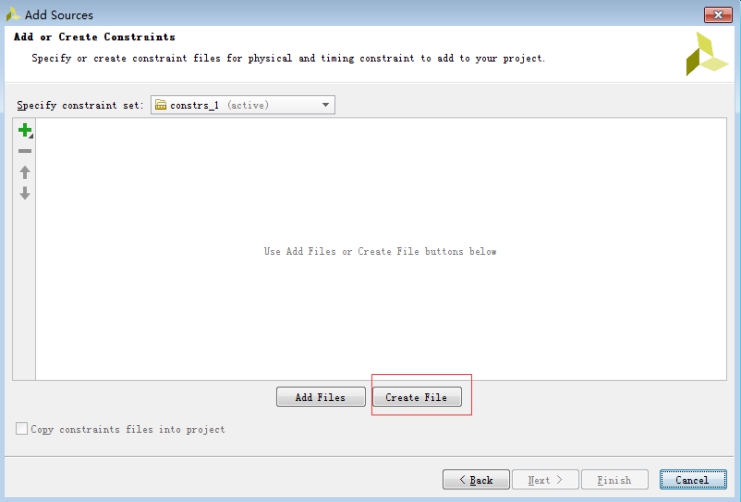

Step3:单击Create File

Step4:命名为led_pin 后单击OK

Step5:可以看到产生了名为led_pin.adc的文件然后单击Finish

Step6:打开led_pin.adc文件添加如下约束

|

create_clock -name clk100MHZ -period 10.0 [get_ports {CLK_i}] set_property PACKAGE_PIN Y9 [get_ports {CLK_i}] set_property IOSTANDARD LVCMOS33 [get_ports {CLK_i}] set_property PACKAGE_PIN N15 [get_ports {RSTn_i}] set_property IOSTANDARD LVCMOS18 [get_ports {RSTn_i}] set_property PACKAGE_PIN T22 [get_ports {LED_o[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[0]}] set_property PACKAGE_PIN T21 [get_ports {LED_o[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[1]}] set_property PACKAGE_PIN U22 [get_ports {LED_o[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[2]}] set_property PACKAGE_PIN U21 [get_ports {LED_o[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[3]}] set_property PACKAGE_PIN V22 [get_ports {LED_o[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[5]}] set_property PACKAGE_PIN W22 [get_ports {LED_o[5]}] set_property PACKAGE_PIN U19 [get_ports {LED_o[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[7]}] set_property PACKAGE_PIN U14 [get_ports {LED_o[7]}] |

7.7 编译并且产生bit文件

Step1:单击综合

Step2:单击执行

Step3:单击产生bit

7.8下载程序

Step1:给开发板通电,并且连接下载器

Step2:单击OpenTarget 然后单击Auto Connect

Step3:连接成功后

Step4:单击Program Device

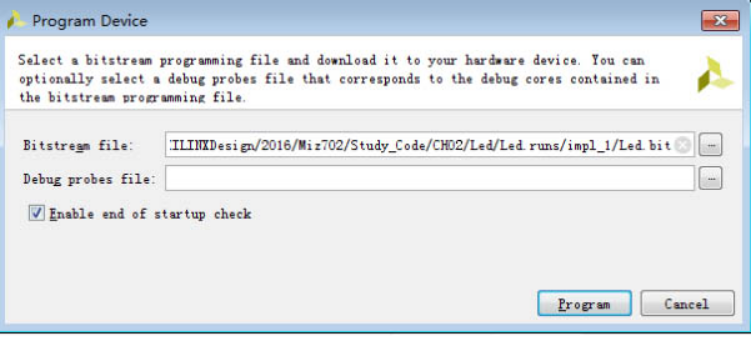

Step5:单击Program Device 然后选择 XC7Z020_1

Step6:或者也可以从顶部单击Program device

Step7:弹出的对话框中有我们要下载的Bit文件

Step7:下载过程

7.9实验结果

下载过程下载完成后LED流水灯就运行起来了。

7.10本章小结

本章详细讲解了如何创建VIVADO工程以及在VIVADO工程环境下编写纯PL代码的程序,并且讲解了如何添加管脚约束,时钟约束,编译程序,下载程序。通过流水灯实现这个简单的实验抛砖引玉,让大家掌握了VIVADO软件的使用。

【第一季】CH07_FPGA_RunLED创建VIVADO工程实验的更多相关文章

- java搭建web从0-1(第一步:创建web工程)

intellij idea版本:2017 1.新建一个web工程 使用工具intellij ideal,注意:只有Ultimate版本的可以新建web工程,社区版本的不支持新建web工程 File ...

- Maven创建父子工程(简单、完整)

Eclipse创建Maven父子工程(书中有的叫聚合工程,因为看了网上很多教程,实际操作总会有这样那样的小问题,有时候包结构还不对,创建成功后索性就自己写一篇帮助小白,有不对请指教) 1 file-n ...

- 【第一季】CH08_FPGA_Button 按钮去抖动实验

[第一季]CH08_FPGA_Button 按钮去抖动实验 按键的消抖,是指按键在闭合或松开的瞬间伴随着一连串的抖动,这样的抖动将直接影响设计系统的稳定性,降低响应灵敏度.因此,必须对抖动进行处理,即 ...

- Vivado SDK 2014.2 创建新工程后,BSP版本不对的解决办法

问题描述如下: 1. 使用Vivado SDK 2014.2已经创建了工程,但是此时,hdf文件增加了外设,需要重新创建工程以更新SDK中的外设描述: 2. 使用新的hdf创建工程后,发现system ...

- vivado 创建PS工程

前言 本文简要介绍在vivado中创建PS工程.单纯使用zynq芯片的PS部分就像使用普通ARM芯片一样,只是多了建立Zynq硬件系统这一个步骤.vivado创建PL工程参见此处 新建工程 与viva ...

- vivado 创建PL工程

参考来源 https://china.xilinx.com/video/hardware/i-and-o-planning-overview.html 前言 我Win10系统上的Xilinx Plat ...

- Verilog基础入门——Vivado工程创建(三)

Verilog基础入门--Vivado工程创建(三) Vivado是Verilog语言的一个集成环境,目前使用的版本为英文版,简单介绍一下在Vivado中创建一个工程并写入源文件 [配置] win10 ...

- 【第一季】CH09_FPGA多路分频器设计

[第一季]CH09_FPGA多路分频器设计 在第七节的学习中,笔者带大家通过一个入门必学的流水灯实验实现,快速掌握了VIVADO基于FPGA开发板的基本流程.考虑到很多初学者并没有掌握好Vivado ...

- QQ聊天界面的布局和设计(IOS篇)-第一季

我写的源文件整个工程会再第二季中发上来~,存在百度网盘, 感兴趣的童鞋, 可以关注我的博客更新,到时自己去下载~.喵~~~ QQChat Layout - 第一季 一.准备工作 1.将假数据messa ...

随机推荐

- 设置Python打印格式

>>> def esc(code): ... return f'\033[{code}m' ... >>> print(esc('31;1;4') + 'reall ...

- JS获取div高度的方法

有时在写页面时,需要获取一个div的高度.怎么才能获取呢?哈哈,先上结论.有两种方法. offsetHeight .clientHeight getComputedStyle offsetHeight ...

- java经典算法题50道

原文 JAVA经典算法50题[程序1] 题目:古典问题:有一对兔子,从出生后第3个月起每个月都生一对兔子,小兔子长到第三个月后每个月又生一对兔子,假如兔子都不死,问每个月的兔子总数为多少?1.程序 ...

- THREE.js(一)

//创建场景 var scene = new THREE.Scene(); //透视摄像机(视野角度,长宽比,远剪切面,进剪切面,) var camera = new THREE.Perspectiv ...

- 文件上传对servlet的要求

request.getParamter(String name)方法不能再使用了 需要使用request.getInputStream()获取输入流对象然后在进行读取数据 解析数据 ServletIn ...

- 记录一次vxworks下使用NFS组件的过程

问题:有三块CPU都运行vxworks6.9,现在想要CPU3做server,CPU1-2通过NFS访问CPU3上的文件 补充:使用防火墙可能会影响NFS访问,目前我还没有找到解决办法... 下面是过 ...

- delphi7 treeview + 数据库 实现动态节点维护

首先说下树节点对应的表的基本结构,必需要有的字段(节点编号,父节点编号,节点名称),其他字段根据你开发的需要添加从添加节点开始,一开始就取出表中最大节点编号,每次添加节点的时候,该节点编号增加1;添加 ...

- XGBoost原理详解

原文:https://blog.csdn.net/qq_22238533/article/details/79477547

- Spark On YARN(Yarn-Cluster模式)启动流程源码分析(二)

转自:https://www.cnblogs.com/yy3b2007com/p/11087180.html 本章将针对yarn-cluster(--master yarn –deploy-mode ...

- Jmeter综合运用 之 接口测试

Jmeter用的最多的就是做接口和性能测试了,着实比较好用,今天给大家分享下如何利用Jmeter做接口测试. 在做接口测试之前,我们起码需要了解: 1.接口涉及的业务 2.接口的基本信息:访问地址.传 ...