基于Verilog的串口发送程序

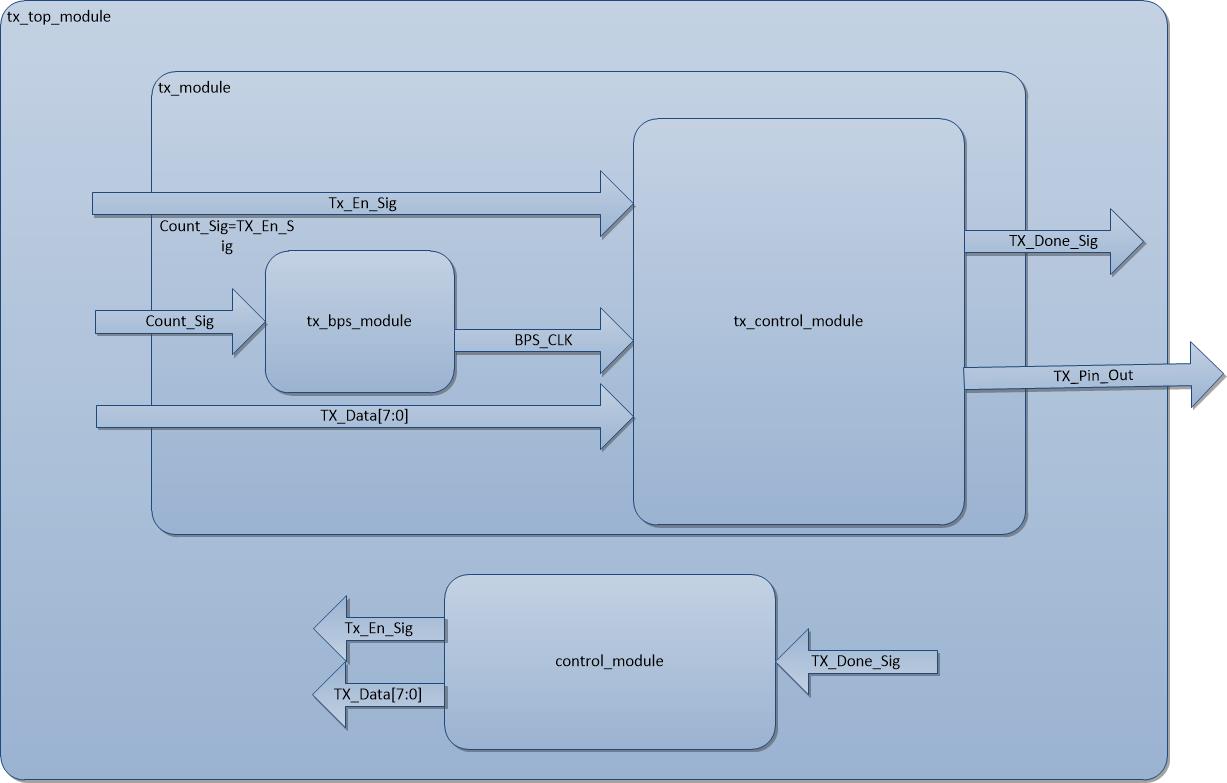

一、模块框图及基本思路

tx_bps_module:波特率时钟产生模块

tx_control_module:串口发送的核心控制模块

tx_module:前两个模块的组合

control_module:发送控制模块,每秒触发一次发送

tx_top_module:tx_module+control_module

二、软件部分

tx_bps_module:

module tx_bps_module #(parameter Baud=)(

CLK,RSTn,

Count_Sig,

BPS_CLK

);

input CLK;

input RSTn;

input Count_Sig;

output BPS_CLK; /***************************/

localparam Baud_Div=50_000_000/Baud-;

localparam Baud_Div2=Baud_Div/; reg[:] Count_BPS;

/*************************/

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

Count_BPS<='d0;

else if(Count_BPS==Baud_Div)

Count_BPS<='d0;

else if(Count_Sig)

Count_BPS<=Count_BPS+;

else Count_BPS<='d0;

end

/************************/

assign BPS_CLK=(Count_BPS==Baud_Div2)?'b1:1'b0;

endmodule

tx_control_module:

module tx_control_module(

CLK,RSTn,

TX_En_Sig,TX_Data,BPS_CLK,

TX_Done_Sig,TX_Pin_Out

);

input CLK,RSTn;

input TX_En_Sig,BPS_CLK;

input [:]TX_Data;

output TX_Done_Sig,TX_Pin_Out;

/***************************************/

reg rTX;

reg isDone;

reg[:] i;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

rTX<='b1;

isDone<='b0;

i<='d0;

end

else if(TX_En_Sig)

begin

case(i)

'd0:if(BPS_CLK) begin rTX<=0;i<=i+1'b1; end

'd1,4'd2,'d3,4'd4,'d5,4'd6,'d7,4'd8:

if(BPS_CLK) begin rTX<=TX_Data[i-];i<=i+'b1; end

'd9:if(BPS_CLK) begin rTX<=1;i<=i+1'b1; end

'd10:if(BPS_CLK) begin rTX<=1;i<=i+1'b1; end

'd11:if(BPS_CLK) begin isDone<=1;i<=i+1'b1; end

'd12: begin isDone<=0;i<=1'b0; end

endcase

end

end

/***************************************/

assign TX_Pin_Out=rTX;

assign TX_Done_Sig=isDone;

endmodule

tx_module:

module tx_module(

CLK,RSTn,

TX_En_Sig,TX_Data,TX_Pin_Out,TX_Done_Sig

);

input CLK;

input RSTn;

input TX_En_Sig;

input [:] TX_Data;

output TX_Pin_Out;

output TX_Done_Sig; wire BPS_CLK; tx_bps_module U0(.CLK(CLK),.RSTn(RSTn),.Count_Sig(TX_En_Sig),.BPS_CLK(BPS_CLK));

tx_control_module U1(.CLK(CLK),.RSTn(RSTn),.TX_En_Sig(TX_En_Sig),

.BPS_CLK(BPS_CLK),.TX_Data(TX_Data),.TX_Done_Sig(TX_Done_Sig),

.TX_Pin_Out(TX_Pin_Out));

endmodule

control_module:

module control_module(

CLK, RSTn,

TX_Done_Sig,

TX_En_Sig, TX_Data

);

input CLK;

input RSTn;

input TX_Done_Sig;

output TX_En_Sig;

output [:]TX_Data; /***********************************************/

localparam T1S='d49_999_99;

reg [:] Count_Sec;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

Count_Sec<='d0;

else if(Count_Sec==T1S) Count_Sec<='d0;

else Count_Sec<=Count_Sec+'b1;

end

/************************************************/ reg[:] rData;

reg isEn;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

rData<='h31;

isEn<='b0;

end

else if(TX_Done_Sig)

begin

rData<='h31;

isEn<='b0;

end

else if(Count_Sec==T1S) isEn<='b1;

end /*************************************************/

assign TX_Data=rData;

assign TX_En_Sig=isEn; /*************************************************/

endmodule

tx_top_module:

module tx_top_module(

CLK,RSTn,

TX_Pin_Out

);

input CLK;

input RSTn;

output TX_Pin_Out; wire TX_Done_Sig;

wire TX_En_Sig;

wire [:]TX_Data;

control_module U0(

.CLK(CLK), .RSTn(RSTn),

.TX_Done_Sig(TX_Done_Sig),

.TX_En_Sig(TX_En_Sig), .TX_Data(TX_Data)); tx_module U1(

.CLK(CLK),.RSTn(RSTn),

.TX_En_Sig(TX_En_Sig),.TX_Data(TX_Data),.TX_Pin_Out(TX_Pin_Out),.TX_Done_Sig(TX_Done_Sig)

);

endmodule

三、硬件部分

黑金SPARTAN开发板

NET "CLK" LOC = T8;

NET "RSTn" LOC = L3;

NET "TX_Pin_Out" LOC = D12;

基于Verilog的串口发送程序的更多相关文章

- 基于Verilog的串口接收程序

一.模块框图及基本思路 detect_module:检测输入引脚的下降沿,以此判断一帧数据的开始 rx_bps_module:波特率时钟产生模块 rx_control_module:串口接收的核心控制 ...

- 基于Verilog的带FIFO写入缓冲的串口发送接口封装

一.模块框图及基本思路 tx_module:串口发送的核心模块,详细介绍请参照前面的“基于Verilog的串口发送实验” fifo2tx_module:当fifo不为空时,读取fifo中的数据并使能发 ...

- 纠错:基于FPGA串口发送彩色图片数据至VGA显示

今天这篇文章是要修改之前的一个错误,前面我写过一篇基于FPGA的串口发送图片数据至VGA显示的文章,最后是显示成功了,但是显示的效果图,看起来确实灰度图,当时我默认我使用的MATLAB代码将图片数据转 ...

- 基于Verilog的带FIFO输出缓冲的串口接收接口封装

一.模块框图及基本思路 rx_module:串口接收的核心模块,详细介绍请见“基于Verilog的串口接收实验” rx2fifo_module:rx_module与rx_fifo之间的控制模块,其功能 ...

- C#中缓存的使用 ajax请求基于restFul的WebApi(post、get、delete、put) 让 .NET 更方便的导入导出 Excel .net core api +swagger(一个简单的入门demo 使用codefirst+mysql) C# 位运算详解 c# 交错数组 c# 数组协变 C# 添加Excel表单控件(Form Controls) C#串口通信程序

C#中缓存的使用 缓存的概念及优缺点在这里就不多做介绍,主要介绍一下使用的方法. 1.在ASP.NET中页面缓存的使用方法简单,只需要在aspx页的顶部加上一句声明即可: <%@ Outp ...

- 串口发送端verilog代码分析

串口发送端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- 基于STM32F10x的串口(USART)输入输出编程

1 前言 STM32有强大的固件库,绝大部分函数都可以有库里面的函数组合编写.固件库可以到ST官网(www.st.com)上下载,也可以搜索“STM32 固件库 v3.5”下载到固件库.本文章就是基于 ...

- C语言实验单片机串口发送int型数据

void SendIint(int n)reentrant { unsigned char s; while(n!=0) { s=(unsigned char)n%10+48; SendByte(s) ...

- 【小梅哥FPGA进阶教程】串口发送图片数据到SRAM在TFT屏上显示

十五.串口发送图片数据到SRAM在TFT屏上显示 之前分享过rom存储图片数据在TFT屏上显示,该方法只能显示小点的图片,如果想显示TFT屏幕大小的图片上述方法rom内存大小不够.小梅哥给了个方案,利 ...

随机推荐

- python基础(四)集合

[集合特点] 1.天生去重.循环 2 关系测试 -交集,差集,并集,(反向差集,对称差集) list = [1,2,3,4,5,3,6]list_2 =[2,3,5,7,8]list=set(lis ...

- 表单、框架结构的大概、CSS开头(选择器以及常用属性)

<!--为网页添加图标,写在头部--> <link rel="shortcut icon" href="favicon.ico(路径)" ty ...

- Oracle之with as和update用法

许久不用,又忘了,做个记录 update test b set b.code=(with t as(select t.id,code||'_'||row_number() over(partition ...

- 自制操作系统Antz(6)——内核初步,引入c语言

Antz系统更新地址: https://www.cnblogs.com/LexMoon/category/1262287.html Linux内核源码分析地址:https://www.cnblogs. ...

- Oracle 参数文件spfile

pfile和spfile 概念 ORACLE中的参数文件是一个包含一系列参数以及参数对应值的操作系统文件,可以分为两种类型.它们是在数据库实例启动时候加载的,决定了数据库的物理结构.内存.数据库的限制 ...

- 剑指offer(61)序列化二叉树

题目描述 请实现两个函数,分别用来序列化和反序列化二叉树 题目分析 首先拿到题目时候,我先想到的是什么是序列化二叉树?序列化主要就是在前后端交互时候需要转换下,毕竟网络传输的是流式数据(二进制或者文本 ...

- 最短路径之Bellman-Ford——解决负权边

Bellman-Ford算法非常简单,核心代码四行,可以完美的解决带有负权边的图. for(k=1;k<=n-1;k++) //外循环循环n-1次,n为顶点个数 for(i=1;i<=m; ...

- topcoder srm 560 div1

problem1 link 从大到小贪心,较大的数字应该放置在较浅的位置. problem2 link 最后的位置要么都是整数(经过偶数次变换),要么是$(p.5, q.5)$这种位置(奇数次变换). ...

- MyBio小隐本记注册破解

既然开始了,就把这一个系列的都破了算了,这次主角小隐本记MyBio 和WDTP的原理是差不多的,先把软件界面换成e文,然后写了15个记录后提示注册,一样的路子,直接跳过注册窗口的弹出就好了 然后查壳一 ...

- WebApi 运行原理

1.当请求过来时,首先经过Global 下面的Application_start()方法,在这个方法中注册了WebApiConfig.Register 2.WebApiConfig.Register把 ...