ModelSim+Synplify+Quartus的Alte

[page_break] 本文适合初学者,源代码:mux4_to_1.v

工作内容:

1、设计一个多路选择器,利用ModelSimSE做功能仿真;

2、利用Synplify Pro进行综合,生成xxx.vqm文件;

3、利用Quartus II导入xxx.vqm进行自动布局布线,并生成xxx.vo(Verilog

4、利用ModelSimSE做后仿真,看是否满足要求。

注:

1. 仿真器(Simulator)是用来仿真电路的波形。

2. 综合工具(Synthesizer)的功能是将HDL转换成由电路所组成的Netlist。

3. 一般而言,在电路设计的仿真上可分为Pre-Sim 和Post-Sim。Pre-Sim 是针而Post-Sim则是针对综合过且做完成了Auto Place and Route(APR)的电路进行仿真,以确保所设计的电路实现在FPGA上时,与Pre-Sim 的功能一样。

1、前仿真(Pre-Sim)

步骤一:打开ModelSimSE,然后建立一个Project;

※建立Project的方式为点选File → New → Project…;

※设定Project Name 与Project location,按OK 即可建立Project。

步骤二:新增设计文档或加入文档。

※新增文档的方式为点选File → New → Source → Verilog,然后对文档进行编辑并储存为xxx.v;

※ 加入文档的方式为点选File → Add to Project → File...,然后点选xxx.v;

步骤三:编译(Compile)。

※编译文档的方式为点选Compile → Compile All,即可编译所有的文档。

※如果编译时发生错误,在显示错误的地方(红字)点两下,即可跳到错误。

步骤四:新增或加入测试平台(Testbench)。

※当设计完电路后,为了确定所设计的电路是否符合要求,我们会写一个测 试平台(Testbench);

※ 新增或加入测试平台,然后编译它。

步骤五:仿真(Simulate)。

※仿真的方式为点选Simulate → Simulate…;

※打开Design里面的work,然后点选mux_4_to_1_tb 并Add 它,最后按Load 即可跳到仿真窗口。

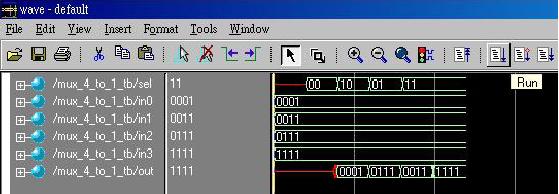

步骤六:加入信号线。

※ 在窗口上按右键,然后点选Add → Add to Wave;

步骤七:看波形。

※在工具列上按Run,然后就会显示波形;

※慢慢看波形吧,没有波形就没有真相!

以上就是使用ModelSim做Pre-Sim的基本流程,在此要特别强调的是,ModelSim所有的功能并不仅仅于此,如果你想要了解更多的话,一切都要靠自己花时间去问去试,只有努力的人才能有丰富的收获,加油!

2、综合(Synthesis)

步骤一:打开Synplify Pro,然后建立一个Project。

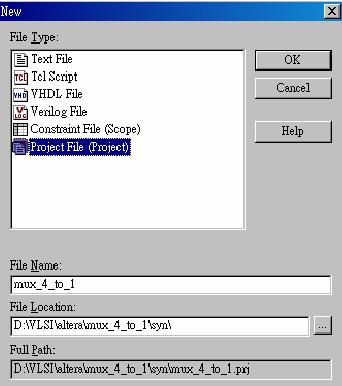

※先点选File,再点选New;

※选择Project File,并设定File Name与File Location;

步骤二:加入设计文件。

※ 点选欲加入的xxx.v,然后按Add,再按OK后就可以将档案加入。

步骤三:选择FPGA的Device 与其它相关设定。

※先点选Project,再点选Implementation Options。

※在Device 的设定如下:Technology为Altera Stratix,Part为EP1S10,Speed 为-6,Package 为FC780。

※在Options 的设定是将FSM Compiler与Resource Sharing打勾。

※在Constraints的设定是将Frequency设定至100Mhz。

※在Implementation Results的设定是将Result File Name填入与电路模块相同的名称,而xxx.vgm这个文件会在QuartusII做APR时被使用。然后将下列两个选项打勾(Write Vendor Constraint File与Write Mapped Verilog Netlist)。

※在Timing Report的设定是将Number of Critical Paths与Number of Start/End Points都设为11。

※在Verilog里是将TOP Level Module填入与电路模块相同的名称,然后将 Use Verilog 2001打勾。

步骤四:综合(Synthesis)。

※点选RUN → Synthesize,最后出现Done!就是已经综合完毕。

步骤五:检查综合后的电路。

※先点选HDL Analyst,再点选RTL,最后点选Hierarchal View,画面会出现综合后的电路Netlist。

以上就是使用Synplify将HDL程序合成为电路Netlist的基本流程,值得注意的是,当你针对不同要求而设定的Constraints不同时,你就会得到不同的电路Netlist,所要付出的硬件代价也不同,这就需要大家多花点心思来了解其中的奥妙之处。

3、自动布局布线(APR)

步骤一:开启Quartus II,然后建立一个Project。

※先点选File,再点选New Project Wizard…。

※设定Work Directory,Project Name与Top-Level Entity Name,再按Next。

步骤二:加入设计文件。

※ 点选Add…,将Synplify合成出来的xxx.vqm加入,再按Next。

步骤三:设定相关的EDA Tools。

※在Tool Type点选Simulation,Tool Name点选ModelSim。

※ 点选Settings,将Time Scale设定为1 ns。

步骤四:设定Family。

※ 设定Family为Stratix,再按Next。

步骤五:设定Device。

※ 设定Device 为EP1S10F780C6,再按Finish,即可完成Project的设定。

步骤六:编译。

※ 点选Processing → Start Compilation,即可开始编译。

步骤七:完成编译。

※ 弹出下面窗口即代表编译完毕。

以上就是使用Quartus II对电路Netlist做APR的基本流程,并且利用设定仿真工具所产生的xxx.vo(Verilog Output File)与xxx.sdo(Standard Delay Output File)做后仿真。

4、后仿真(Post-Sim)

步骤一:启动ModelSim,然后建立一个Project。

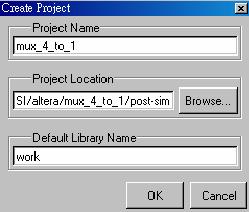

※建立Project的方式为点选File → New → Project…。

※设定Project Name与Project location,按OK即可建立Project。

步骤二:加入设计文档。

※将xxx.vo更改为xxx.v,然后加入。

步骤三:加入组件库文件。

※由于我们是采用Altera的Cell Library来合成电路,所以合成后的电Netlist里所包括的那些Logic Gates与Flip-Flop 都是出自于Cell Library,所以模拟时要将此Cell Library加入。

※我们所选用的Family是Stratix,所以到QuartusIIedasim_lib 里将Stratix的Cell Library(stratix_atoms.v)加入。

步骤四:加入测试平台。

※加入Pre-Sim的测试平台,并在测试平台里加上`timescale 1ns/100ps。

步骤五:编译。

※编译档案的方式为点选Compile → Compile All,即可编译所有的档案。

※如果编译时发生错误,在显示错误的地方(红字)点两下,即可跳到错误。

步骤六:仿真。

※仿真文件的方式为点选Simulate → Simulate…。

步骤七:加入要观察的信号。

※在窗口上按右键,然后点选Add → Add to Wave。

步骤八:观察波形。

※慢慢看波形吧,没有波形就没有真相!

步骤九:比对Pre-Sim 与Post-Sim。

※ 很明显地,Post-Sim 的输出有不稳定的信号,并且受到延迟时间的影响。

转载自:http://www.elecfans.com/article/87/98/2010/20100607219006.html

ModelSim+Synplify+Quartus的Alte的更多相关文章

- 浅谈用ModelSim+Synplify+Quartus来实现Altera FPGA的仿真

浅谈用ModelSim+Synplify+Quartus来实现Altera FPGA的仿真 工作内容: Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业 ...

- 14.quartus联合modelsim仿真

在quartus调用modelsim仿真过程中,出现了一个错误,如下所示: Check the NativeLink log file I:/Quartus11.0/Myproject/testi_n ...

- Modelsim初级使用教程

来源 http://blog.sina.com.cn/s/blog_6c7b6f030101ctlh.html 一. Modelsim简介 Modelsim仿真工具是Model公司开发的.它支持Ver ...

- 关于使用ModelSim中编写testbench模板问题

对于初学者来说写Testbench测试文件还是比较困难的,但Modelsim和quartus ii都提供了模板,下面就如何使用Modelsim提供的模板进行操作. Modelsim提供了很多Testb ...

- 如何使用SignalTap II觀察reg與wire值? (SOC) (Verilog) (Quartus II) (SignalTap II)

Abstract撰寫Verilog時,雖然每個module都會先用ModelSim或Quartus II自帶的simulator仿真過,但真的將每個module合併時,一些不可預期的『run-time ...

- 数字IC设计工程师的知识结构

刚毕业的时候,我年少轻狂,以为自己已经可以独当一面,庙堂之上所学已经足以应付业界需要.然而在后来的工作过程中,我认识了很多牛人,也从他们身上学到了很多,从中总结了一个IC设计工程师需要具备的知识架构, ...

- 个人学习FPGA的初步过程

对于FPGA,完全是从零开始学习,简单讲述一下我个人学习FPGA的经历吧: 没有开发板的日子.说真的要我掏腰包买开发板觉得是一件非常奢侈的事情.理由1:现成的东西,背后影藏诸多诡异的事情我们是无法体会 ...

- 基于dsp_builder的算法在FPGA上的实现(转自https://www.cnblogs.com/sunev/archive/2012/11/17/2774836.html)

一.摘要 结合dsp_builder.matlab.modelsim和quartus ii等软件完成算法的FPGA实现. 二.实验平台 硬件平台:DIY_DE2 软件平台:quartus ii9.0 ...

- 《FPGA全程进阶---实战演练》第四章之实验平台软硬件使用简介

本章主要是讲解读者在进行FPGA逻辑设计之前的准备工作,需要下载Quartus II软件和 Modelsim 软件,一个是用来进行FPGA逻辑设计,一个是用来对逻辑进行理论分析与验证. 1.1 qua ...

随机推荐

- PS常用技能综合

1.ps中怎么吧选中的一块区域覆盖到另一个区域中? 1.用PS中选取工具或套索工具--选好后用移动工具把你选取的区域移动到你要覆盖的地方2.或用图章工具中的仿制图章 2.如何将选中的区域新建为一个新图 ...

- Asp.net 生成静态页面

http://www.cnblogs.com/tonycall/archive/2009/07/18/1526079.html Asp.net 生成静态页面(简单用法) 第一次发表,有什么错误,请大家 ...

- BIOS和Bootloader的对比

桌面电脑刚加电时,一个叫做BIOS的软件程序立刻获得了处理器的控制权.(历史上,BIOS是Basic Input/Output Software的缩写,但现在这个单词已经有了自身的含义,因为其完成的功 ...

- iOS-仿京东6位密码支付输入框

概述 用于安全支付的密码支付输入框. 详细 代码下载:http://www.demodashi.com/demo/10709.html 开发需求中有时候我们需要用于安全支付的功能, 需要设置APP钱包 ...

- Web Service-WSDL详解

WSDL指网络服务描述语言 (Web Services Description Language), 是一种用XML编写的文档, 用于描述Web Service和函数.参数以及返回值等; 文档内规定了 ...

- Foundations of Machine Learning: Boosting

Foundations of Machine Learning: Boosting Boosting是属于自适应基函数(Adaptive basis-function Model(ABM))中的一种模 ...

- Java数据库表自动转化为PO对象

本程序简单实现了数据库内省,生成PO对象. 数据库内省有如下两种实现方式: 通过mysql元表 通过desc table,show tables等命令 import java.io.IOExcepti ...

- ubuntu修改固定ip

1.vi /etc/network/interfasces,添加红框内的内容:

- Windows下面安装和配置Solr 4.9(一)

1.Solr下载 下载地址 :http://lucene.apache.org/solr/ 2.解压,测试 在example文件夹中找到start.jar文件,用命令提示符运行这个文件:ja ...

- List Set Map以及子接口用法总结(转)

Collection ├List│├LinkedList│├ArrayList│└Vector│ └Stack└SetMap├Hashtable├HashMap └WeakHashMap list 和 ...