使用Vivado的block design

使用Vivado的block design

(1)调用ZYNQ7 Processing System

(2)配置ZYNQ7系统

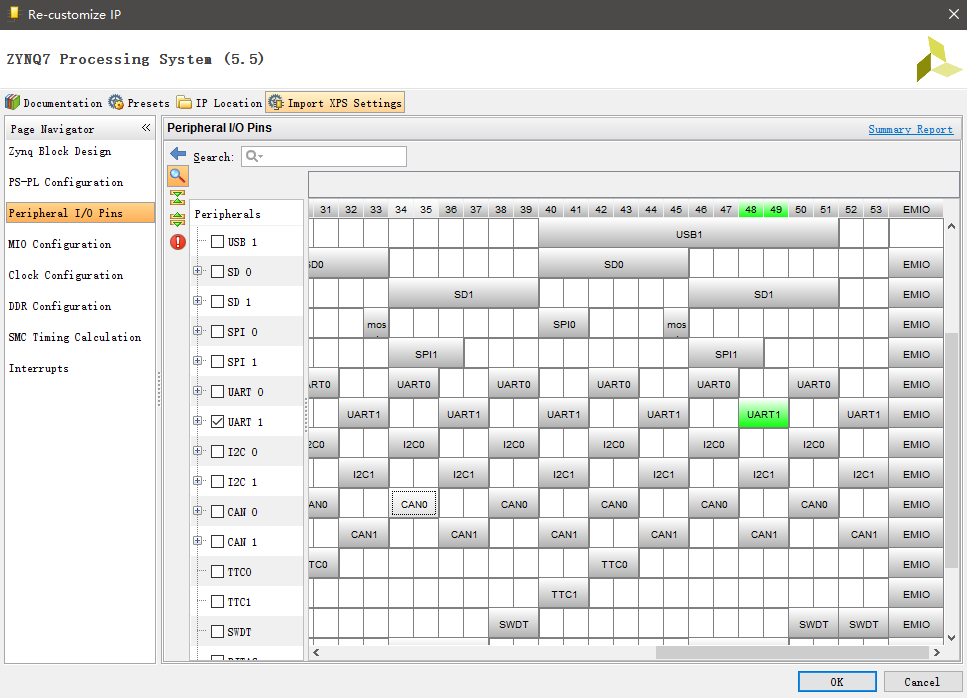

(3)外设端口配置

根据开发板原理图MIO48和MIO49配置成了串口通信。

(4)串口波特率的配置

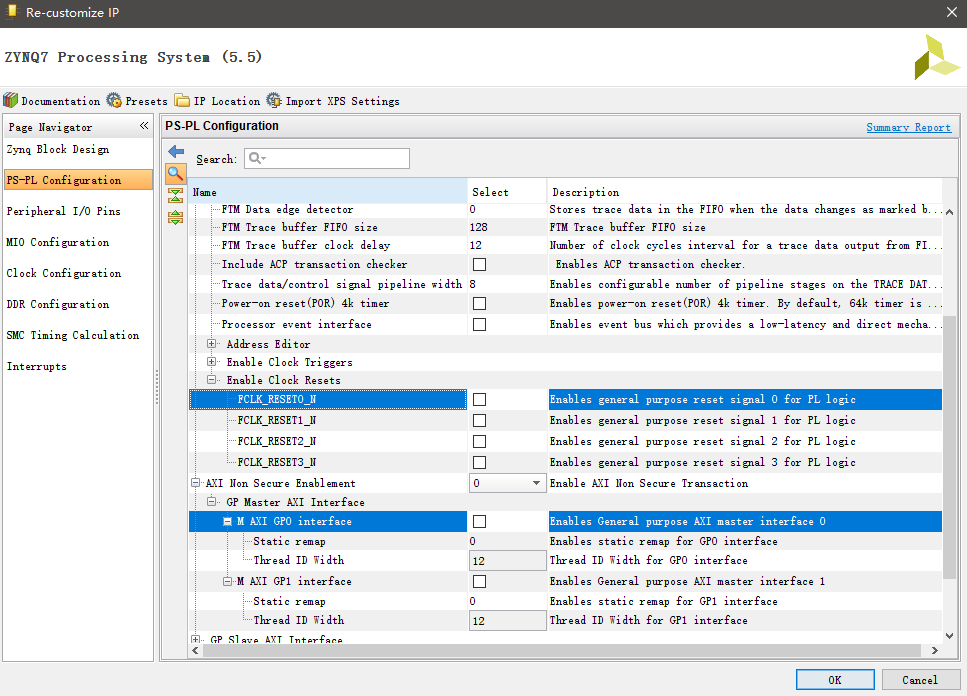

(5)关于AXI总线的配置

(6)时钟配置界面

这里可以配置ZYNQ系统输入时钟,CPU的工作时钟,DDR工作时钟,还有其他外设的工作时钟。

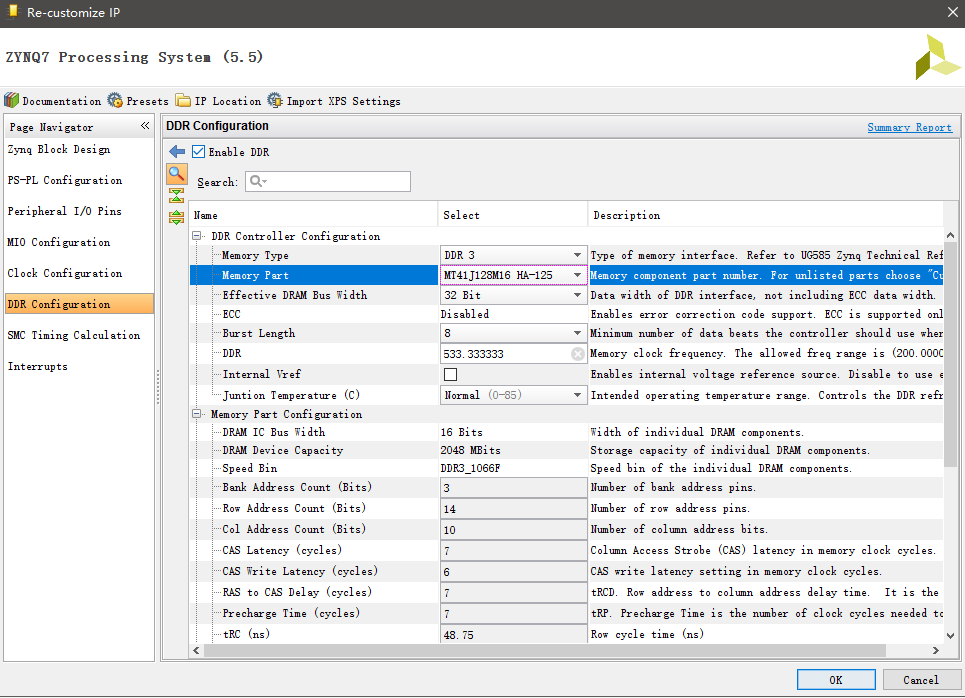

(7)DDR的配置

重点在于选择DDR的信号,其他参数会自适应。

(8)Run Block Automation完成对ZYNQ7 Processing System IP核的配置

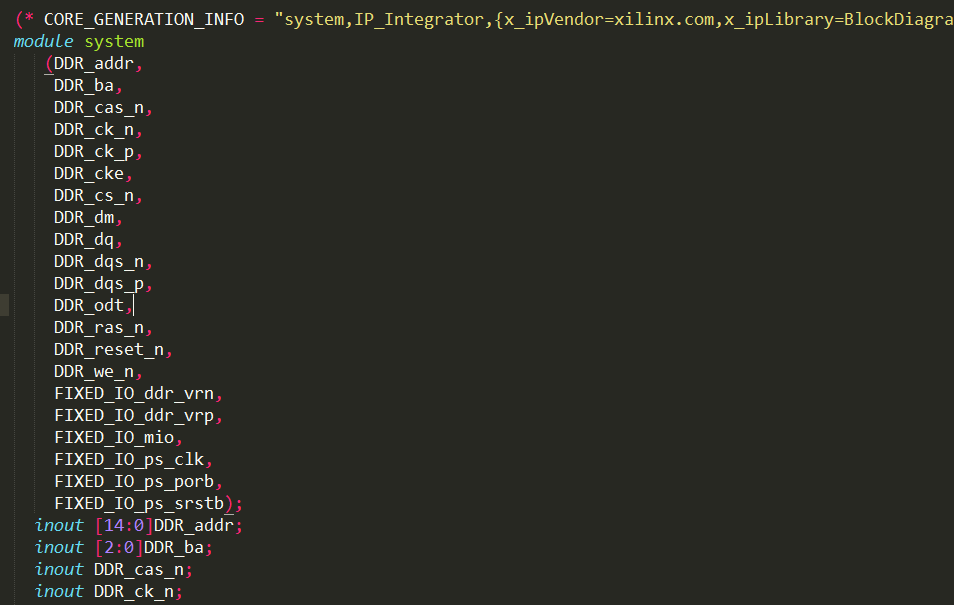

运行完Run Block Automation之后,会生成ZYNQ系统外部管脚,如下图:一个是DDR接口,一个是FIXED_IO接口。

(9)Generate Output Products

此步骤是用来生成Diagram Block Design的HDL源文件以及相应端口的约束文件。

生成的system.v文件内容如下图所示,其实就是这个block design的顶层文件:

(10)生成整个工程的顶层文件

生成结果为:

注意:如果系统只使用了PS部分的资源,没有使用PL部分的资源,则不需要再vivado下编译和生成bit文件了。

(11)硬件导入SDK

File ->Export->Export Hardware..

(12)启动SDK开发环境

File->Launch SDK

(13)SDK软件编程

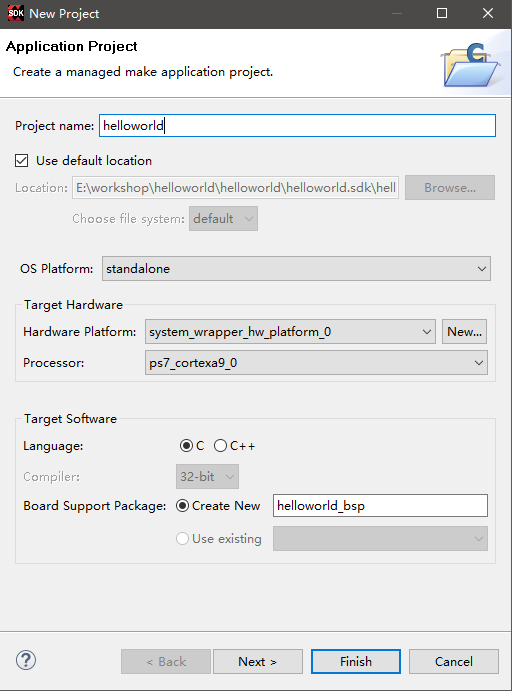

File->New->Application Project,即新建一个SDK的软件工程。

选择工程模板Hello World

新建的Hello World工程

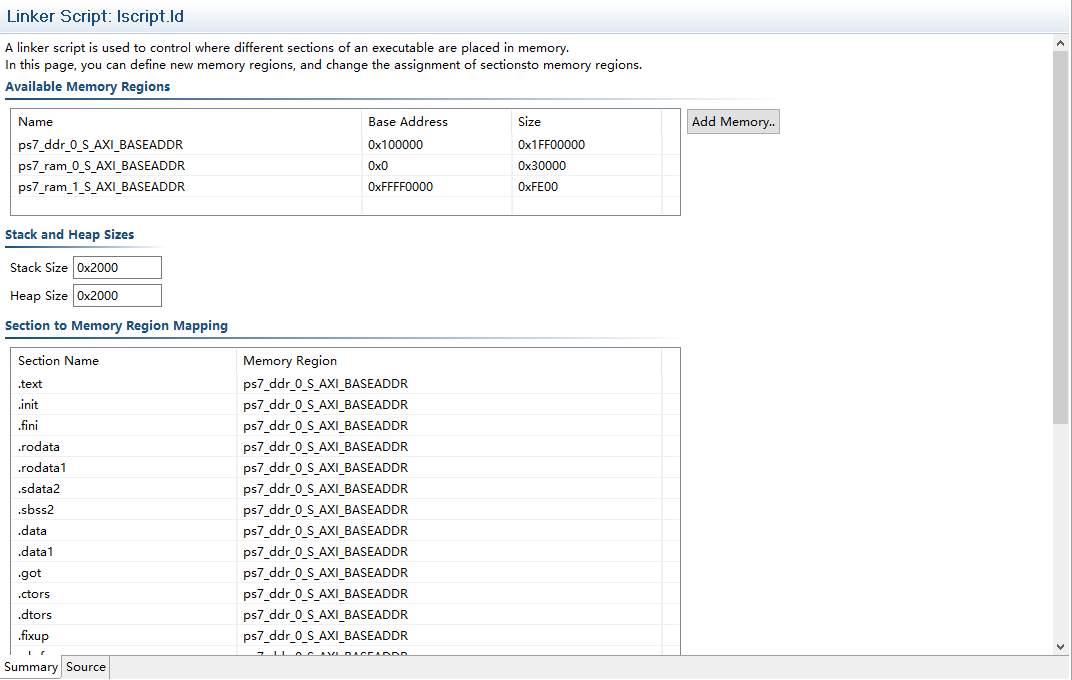

其中工程里面的lscript.ld文件是用来定义程序或者数据是在内部的RAM还是外部的DDR里面。

(14)编译软件程序

Build Project

使用Vivado的block design的更多相关文章

- Vivado中备份设计好的block design

参考链接 https://blog.csdn.net/dimples_song/article/details/81391615 前言 为了不每次都重新生成block design,避免重复劳动. 可 ...

- ZYNQ block design警告:[BD 41-968] AXI interface port /axi_lite4 is not associated to any clock port. It may not work correctly.

前言 在Block design中引出AXI接口给外部,检查设计告警如下: [BD 41-968] AXI interface port /axi_lite4 is not associated to ...

- Block Design 小技巧之添加RTL代码到block_design

Block Design 小技巧之添加RTL代码到block_design 1.首先得打开Block Design,右击RTL文件,才会出现Add module to Block Design选项. ...

- ZYNQ Block Design中总线位宽的截取与合并操作

前言 在某些需求下,数据的位宽后级模块可能不需要原始位宽宽度,需要截位,而某些需求下,需要进行多个数据的合并操作. 在verilog下,截位操作可如下所示: wire [7:0] w_in; wire ...

- 方差分析|残差|MSA/MSE|Completely randomized design|Randomized block design|LSD|主效应|intercept|多重比较|

符合方差分析的三个条件: 残差=实际值-预测值(其实是均值). 在原假设下,MSA的期望会等于MSE的期望:在备选假设下,MSA的期望会大于MSE的期望,所以MSA/MSE的取值范围在(1,正无穷), ...

- Vivado_MicroBlaze_问题及解决方法_汇总(不定时更新)

Vivado_MicroBlaze_问题及解决方法_汇总(不定时更新) 标签: Vivado 2015-07-03 14:35 4453人阅读 评论(0) 收藏 举报 分类: 硬件(14) 版权声 ...

- [转载]Vivado轻松实现IP封装

Vivado轻松实现IP封装 1.新建一个测试工程 工程化的设计方法是离不开工程的,第一步往往都是新建工程,后面我会学习去工程化的开发方法,可能会更加高效. 2.利用向导完成IP封装 2.1.启动IP ...

- Vivado的helloword计划(一个):硬件project部分

硬件平台:ZedBoard 软件平台:vivado2013.3 本演示样例通过综合.实现,生成比特流,发送到SDK实现. 启动vivado而且创建一个项目 依据提示操作一步步创建新项目的时候记得选择R ...

- Zedboard(二)使用Vivado+SDK开发嵌入式应用程序——实例一

本次介绍用Vivado构建Zedboard开发板的硬件平台+SDK开发应用程序(Zedboard裸机开发) 过程如下: 一.运行Vivado,建立新工程 指定好工程路径,下一步,选择RTL Proje ...

随机推荐

- 一分钟使用Docker快速搭建Wordpress

1. apt install docker.io -y 2. pip install docker-compose 3. vim wordpress_stack.yml version: '3.1' ...

- Dubbo浅谈

一.高并发的解决 1.高并发:很多人同时访问. 2.高并发产生的性能瓶颈: tomcat支持的controller,解决办法:多个tomcat共同支撑.(tomcat集群) 只有一个service被调 ...

- http状态码301和302的区别

1.官方的比较简洁的说明: 301 redirect: 301 代表永久性转移(Permanently Moved) 302 redirect: 302 代表暂时性转移(Temporarily Mov ...

- python 基础 内置函数 和lambda表达式

1.把任意数值转化为字符串有两种方法. (1)str()用于将数值转化为易于人读的形式.print(str("我是中国人"))>>>我是中国人 (2)repr() ...

- 九度OJ-1001-A+B矩阵-有些小技巧

题目1001:A+B for Matrices 时间限制:1 秒 内存限制:32 兆 特殊判题:否 提交:22974 解决:9099 题目描述: This time, you are supposed ...

- 20155219 2016-2017-2 《Java程序设计》第4周学习总结

20155219 2016-2017-2 <Java程序设计>第4周学习总结 教材学习内容总结 抽象方法与抽象类 如果某方法区块中没有任何程序代码操作,可以使用abstract在class ...

- P2261 [CQOI2007]余数求和 (数论)

题目链接:传送门 题目: 题目背景 数学题,无背景 题目描述 给出正整数n和k,计算G(n, k)=k mod + k mod + k mod + … + k mod n的值,其中k mod i表示k ...

- day 017面向对象-反射

主要内容: isinstance, type, issubclass( 内置函数) 区分函数和方法 反射 一 ( isinstance, type, issubclass) isinstance ...

- Blender设置界面语言

新安装的Blender默认是英文, 可通过如下方法修改界面语言: 1. 点开文件菜单{File},选择用户首选项{User Preferences}: 2. 在用户首选项{User Preferenc ...

- [codeforces round#475 div2 ][C Alternating Sum ]

http://codeforces.com/contest/964/problem/C 题目大意:给出一个等比序列求和并且mod 1e9+9. 题目分析:等比数列的前n项和公式通过等公比错位相减法可以 ...