多路选择器,加法器原理及verilog实现

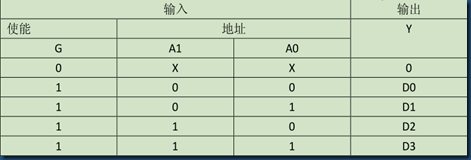

1.数据选择器是指经过选择,把多个通道的数据传到唯一的公共数据通道上。实现数据选择功能的逻辑电路称为数据选择器,它的作用相当于多个输入的单刀多掷开关。本例程以四选一数据选择器(电平触发)为例。 四选一数据选择器书堆 4 个数据源进行选择, 使用量为地址 A1A0 产生 4 个地址信号,由 A1A0 等于“00” 、 “01” 、 “10” 、 “11”来选择输出,真值表如下:

对应的verilog代码为

module mux4(d0,d1,d2,d3,y,a,g);

input d0,d1,d2,d3; // 输入的四个数据

input g; // 输入使能端

input[1:0] a; // 输入的选择端

output y; // 输出数据

reg y; // 输出数据寄存器

always@(d0 or d1 or d2 or d3 or g or a) // 电平触发,当 d0,d1,d2,d3,a 有变化时

候、// 触发

begin

if(g==1'b0) //当 当 g 为 为 0 时候

y=1'b0; //y 置 置 0

else

case(a) // 判断 a 的取值,并作出相应的赋值

2'b00:y=d0;

2'b01:y=d1;

2'b10:y=d2;

2'b11:y=d3;

default:y=1'b0; //a 为其他值得条件下,y 赋予 0

endcase

end

endmodule

时序仿真结果:

2.加法器是一种较为常见的算术运算电路,包括半加器(对两个输入数据相加,输出一个结果位和进位,没有进位输入的电路),全加器(有进位输入)。

如题,实现一个四位全加器:

module add4(a,b,ci,s,co);

input [3:0] a,b; // 输入四位数据 a ,b

input ci; // 输入进位 ci

output [3:0] s; // 输出四位数据 s

output co; // 输出进位 co

assign {co,s}=a+b+ci; //把 把 a 、b 、ci 相加后的结果赋予 co 、s ,其中 co

// 放最高位,s 放低三位

endmodule

多路选择器,加法器原理及verilog实现的更多相关文章

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- 多路选择器实现总线结构——Verilog

////////////////////////////////////////////////////////////////////////////////// //该程序完成通过多路选择器MUX ...

- 格雷码原理与Verilog实现

格雷码原理 格雷码是一个叫弗兰克*格雷的人在1953年发明的,最初用于通信.格雷码是一种循环二进制码或者叫作反射二进制码.格雷码的特点是从一个数变为相邻的一个数时,只有一个数据位发生跳变,由于这种特点 ...

- 多路选择器(multiplexer)简介

1.多路器简介 简称:多路器 功能:多输入 单输出 组合逻辑电路 2.verilog代码实现: module Mux_8(addr,in1,in2,in3,in4,in5,in6,in7,in8 ...

- 【接口时序】6、IIC总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE .ChipScope 硬件平台: 1. FPG ...

- 【接口时序】7、VGA接口原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 【接口时序】4、SPI总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 【接口时序】3、UART串口收发的原理与Verilog实现

一.软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1.FPGA型号:XC6SLX45- ...

- SPI总线的原理与Verilog实现

转载地址:https://www.cnblogs.com/liujinggang/p/9609739.html 一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件 ...

随机推荐

- AS3事件类型

Event事件类型: ACTIVATE 激活事件 DEACTIVATE 对象休眠事件 ADDED 可视对象添加事件 ADDED_TO_STAGE 可视对象添加到舞台事件 REMO ...

- WebapiController的名字不能随便取名

在做webapi时候,遇到一个很坑的问题,就是新增一个控制器时,当新增加的控制器名称叫:AccountController.cs 自己测试,通过postman 访问 都没有问题,但是前端调用会报错,说 ...

- git便携版 添加git-bash到右键菜单

注册表路径 HKEY_CLASSES_ROOT\Directory\Background\shell 新建项取名open in git 默认设置为右键显示的名称 Git Bash Here 新建字符串 ...

- 如何回答——请简述MySQL索引类型

想必大家在被问到这个问题的时候,在网上总是能搜到不同的回答,却又各不相同.其实这些答案大部分都是正确的,只不过在阐述MySQL索引类型的时候从不同方面入手而已.这里归纳如下,具体的机制可以参考其他博文 ...

- Imagetragick RCE(CVE-2016–3714)复现

CVE-2016–3714: 闲着没事突然想起这个洞来,借用vulhub复现一下 poc有很多:https://github.com/ImageTragick/PoCs 我用的 push graphi ...

- jenkins 启动

docker pull jenkinsci/blueocean docker run \ -u root \ --rm \ -d \ -p 8888:8080 \ -p 50000:50000 \ - ...

- python3 提示sqlite模块不存在

首先yum install sqlite-devel -y 然后重装下python3(一定要重装)# cd Python-3.4.2# ./configure --prefix=/usr/local/ ...

- Struts框架笔记03_OGNL表达式与值栈

目录 1. OGNL 1.1 OGNL概述 1.1 什么是OGNL 1.1.2 OGNL的优势 1.1.2 OGNL使用的要素 1.2 OGNL的Java环境入门[了解] 1.2.1 访问对象的方法 ...

- python3+django+mysql

django 连接mysql默认驱动是MySQLdb,MySQLdb没有支持python3的版本,如果使用python3.x版本时,django连接mysql的方法 1.使用pymysql替换MySQ ...

- k8s pv无法删除问题

一般删除步骤为:先删pod再删pvc最后删pv 但是遇到pv始终处于“Terminating”状态,而且delete不掉.如下图: 解决方法: 直接删除k8s中的记录: kubectl patch p ...