001 PCI Express体系结构(一)

一 、PCI总线的基本知识

PCI总线作为处理器系统的局部总线,主要目的是为了连接外部设备,而不是作为处理器的系统总线连接Cache和主存储器。但是PCI总线、系统总线和处理器体系结构之间依然存在着紧密的联系。

(1) PCI总线空间与处理器空间隔离

PCI设备具有独立的地址空间,即PCI总线地址空间,该空间与存储器地址空间通过HOST主桥隔离。处理器需要通过HOST主桥才能访问PCI设备,而PCI设备需要通过HOST主桥才能主存储器。在HOST主桥中含有许多缓冲,这些缓冲使得处理器总线与PCI总线工作在各自的时钟频率中,彼此互不干扰。HOST主桥的存在也使得PCI设备和处理器可以方便地共享主存储器资源。处理器访问PCI设备时,必须通过HOST主桥进行地址转换;而PCI设备访问主存储器时,也需要通过HOST主桥进行地址转换。HOST主桥的一个重要作用就是将处理器访问的存储器地址转换为PCI总线地址。PCI设备使用的地址空间是属于PCI总线域的,而与存储器地址空间不同。

(2) 可扩展性

PCI总线具有很强的扩展性。在PCI总线中,HOST主桥可以直接推出一条PCI总线,这条总线也是该HOST主桥的所管理的第一条PCI总线,该总线还可以通过PCI桥扩展出一系列PCI总线,并以HOST主桥为根节点,形成1颗PCI总线树。这些PCI总线都可以连接PCI设备,但是在1颗PCI总线树上,最多只能挂接256个PCI设备(包括PCI桥)。

在同一条PCI总线上的设备间可以直接通信,并不会影响其他PCI总线上设备间的数据通信。隶属于同一颗PCI总线树上的PCI设备,也可以直接通信,但是需要通过PCI桥进行数据转发。

PCI桥是PCI总线的一个重要组成部件,该部件的存在使得PCI总线极具扩展性。PCI桥也是有别于其他局部总线的一个重要部件。在“以HOST主桥为根节点”的PCI总线树中,每一个PCI桥下也可以连接一个PCI总线子树,PCI桥下的PCI总线仍然可以使用PCI桥继续进行总线扩展。

PCI桥可以管理这个PCI总线子树,PCI桥的配置空间含有一系列管理PCI总线子树的配置寄存器。在PCI桥的两端,分别连接了两条总线,分别是上游总线(Primary Bus)和下游总线(Secondary Bus)。其中与处理器距离较近的总线被称为上游总线,另一条被称为下游总线。这两条总线间的通信需要通过PCI桥进行。PCI桥中的许多概念被PCIe总线采纳,理解PCI桥也是理解PCIe体系结构的基础。

(3) 动态配置机制

PCI设备使用的地址可以根据需要由系统软件动态分配。PCI总线使用这种方式合理地解决了设备间的地址冲突,从而实现了“即插即用”功能。从而PCI总线不需要使用ISA或者EISA接口卡为解决地址冲突而使用的硬件跳线。

每一个PCI设备都有独立的配置空间,在配置空间中含有该设备在PCI总线中使用的基地址,系统软件可以动态配置这个基地址,从而保证每一个PCI设备使用的物理地址并不相同。PCI桥的配置空间中含有其下PCI子树所能使用的地址范围。

(4) 总线带宽

PCI总线与之前的局部总线相比,极大提高了数据传送带宽,32位/33MHz的PCI总线可以提供132MB/s的峰值带宽,而64位/66MHz的PCI总线可以提供的峰值带宽为532MB/s。虽然PCI总线所能提供的峰值带宽远不能和PCIe总线相比,但是与之前的局部总线ISA、EISA和MCA总线相比,仍然具有较大的优势。

ISA总线的最高主频为8MHz,位宽为16,其峰值带宽为16MB/s;EISA总线的最高主频为8.33MHz,位宽为32,其峰值带宽为33MB/s;而MCA总线的最高主频为10MHz,最高位宽为32,其峰值带宽为40MB/s。PCI总线提供的峰值带宽远高于这些总线。

(5) 共享总线机制

PCI设备通过仲裁获得PCI总线的使用权后,才能进行数据传送,在PCI总线上进行数据传送,并不需要处理器进行干预。

PCI总线仲裁器不在PCI总线规范定义的范围内,也不一定是HOST主桥和PCI桥的一部分。虽然绝大多数HOST主桥和PCI桥都包含PCI总线仲裁器,但是在某些处理器系统的设计中也可以使用独立的PCI总线仲裁器。如在PowerPC处理器的HOST主桥中含有PCI总线仲裁器,但是用户可以关闭这个总线仲裁器,而使用独立的PCI总线仲裁器。

PCI设备使用共享总线方式进行数据传递,在同一条总线上,所有PCI设备共享同一总线带宽,这将极大地影响PCI总线的利用率。这种机制显然不如PCIe总线采用的交换结构,但是在PCI总线盛行的年代,半导体的工艺、设计能力和制作成本决定了采用共享总线方式是当时的最优选择。

(6) 中断机制

PCI总线上的设备可以通过四根中断请求信号INTA~D#向处理器提交中断请求。与ISA总线上的设备不同,PCI总线上的设备可以共享这些中断请求信号,不同的PCI设备可以将这些中断请求信号“线与”后,与中断控制器的中断请求引脚连接。PCI设备的配置空间记录了该设备使用这四根中断请求信号的信息。

PCI总线进一步提出了MSI(Message Signal Interrupt)机制,该机制使用存储器写总线事务传递中断请求,并可以使用x86处理器FSB(Front Side Bus)总线提供的Interrupt Message总线事务,从而提高了PCI设备的中断请求效率。

虽然从现代总线技术的角度上看,PCI总线仍有许多不足之处,但也不能否认PCI总线已经获得了巨大的成功,不仅x86处理器将PCI总线作为标准的局部总线连接各类外部设备,PowerPC、MIPS和ARM[1]处理器也将PCI总线作为标准局部总线。除此之外,基于PCI总线的外部设备,如以太网控制器、声卡、硬盘控制器等,也已经成为主流。

注:[1] 在ARM处理器中,使用SoC平台总线,即AMBA总线,连接片内设备。但是某些ARM生产厂商,依然使用AMBA-to-PCI桥推出PCI总线,以连接PCI设备。

二、PCI总线的组成结构

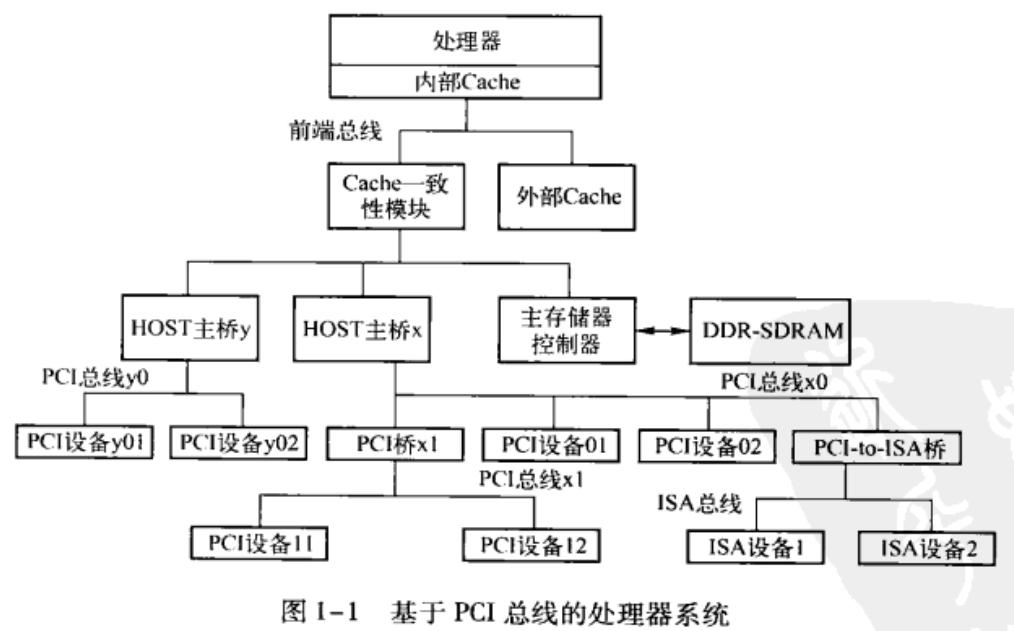

如上文所述,PCI总线作为处理器系统的局部总线,是处理器系统的一个组成部件,讲述PCI总线的组成结构不能离开处理器系统这个大环境。在一个处理器系统中,与PCI总线相关的模块如图1‑1所示。

如图1‑1所示在一个处理器系统中,与PCI总线相关的模块包括,HOST主桥、PCI总线、PCI桥和PCI设备。PCI总线由HOST主桥和PCI桥推出,HOST主桥与主存储器控制器在同一级总线上,PCI设备可以方便地通过HOST主桥访问主存储器,即进行DMA操作。

值得注意的是,PCI设备的DMA操作需要与处理器系统的Cache进行一致性操作,当PCI设备通过HOST主桥访问主存储器时,Cache一致性模块将进行地址监听,并根据监听的结果改变Cache的状态。

在一些简单的处理器系统中,可能不含有PCI桥,此时所有PCI设备都是连接在HOST主桥推出的PCI总线上,此外在一些处理器系统中可能含有多个HOST主桥,如在图1‑1所示的处理器系统中含有HOST主桥x和HOST主桥Y。

1、HOST主桥

HOST主桥主要功能是隔离处理器系统的存储器域与处理器系统的PCI总线域,管理PCI总线域,并完成处理器与PCI设备间的数据交换。处理器与PCI设备间的数据交换主要由“处理器访问PCI设备的地址空间”和“PCI设备使用DMA机制访问主存储器”这两部分组成。

在一个处理器系统中,有几个HOST主桥,就有几个PCI总线域。

如图1‑1所示,HOST主桥x之下的PCI设备属于PCI总线x域,而HOST主桥y之下的PCI设备属于PCI总线y域。在这颗总线树上的所有PCI设备的配置空间都由HOST主桥通过配置读写总线周期访问。

2、PCI总线

在处理器系统中,含有PCI总线和PCI总线树这两个概念。这两个概念并不相同,在一颗PCI总线树中可能具有多条PCI总线,而具有血缘关系的PCI总线组成一颗PCI总线树。如在图1‑1所示的处理器系统中,PCI总线x树具有两条PCI总线,分别为PCI总线x0和PCI总线x1。而PCI总线y树中仅有一条PCI总线。

PCI总线由HOST主桥或者PCI桥管理,用来连接各类设备,如声卡、网卡和IDE接口卡等。在一个处理器系统中,可以通过PCI桥扩展PCI总线,并形成具有血缘关系的多级PCI总线,从而形成PCI总线树型结构。在处理器系统中有几个HOST主桥,就有几颗这样的PCI总线树,而每一颗PCI总线树都与一个PCI总线域对应。

与HOST主桥直接连接的PCI总线通常被命名为PCI总线0。考虑到在一个处理器系统中可能有多个主桥,图1‑1将HOST主桥x推出的PCI总线命名为x0总线,而将PCI桥x1扩展出的PCI总线称之为x1总线;而将HOST主桥y推出的PCI总线称为y0~yn。分属不同PCI总线树的设备,其使用的PCI总线地址空间分属于不同的PCI总线域空间。

3、PCI设备

在PCI总线中有三类设备,PCI主设备、PCI从设备和桥设备。其中PCI从设备只能被动地接收来自HOST主桥,或者其他PCI设备的读写请求;而PCI主设备可以通过总线仲裁获得PCI总线的使用权,主动地向其他PCI设备或者主存储器发起存储器读写请求。而桥设备的主要作用是管理下游的PCI总线,并转发上下游总线之间的总线事务。

一个PCI设备可以即是主设备也是从设备,但是在同一个时刻,这个PCI设备或者为主设备或者为从设备。PCI总线规范将PCI主从设备统称为PCI Agent设备。在处理器系统中常见的PCI网卡、显卡、声卡等设备都属于PCI Agent设备。

在PCI总线中,HOST主桥是一个特殊的PCI设备,该设备可以获取PCI总线的控制权访问PCI设备,也可以被PCI设备访问。但是HOST主桥并不是PCI设备。PCI规范也没有规定如何设计HOST主桥。

在PCI总线中,还有一类特殊的设备,即桥设备。桥设备包括PCI桥、PCI-to-(E)ISA桥和PCI-to-Cardbus桥。本篇重点介绍PCI桥,而不关心其他桥设备的实现原理。PCI桥的存在使PCI总线极具扩展性,处理器系统可以使用PCI桥进一步扩展PCI总线。

PCI桥的出现使得采用PCI总线进行大规模系统互连成为可能。但是在目前已经实现的大规模处理器系统中,并没有使用PCI总线进行处理器系统与处理器系统之间的大规模互连。因为PCI总线是一个以HOST主桥为根的树型结构,使用主从架构,因而不易实现多处理器系统间的对等互连。

即便如此PCI桥仍然是PCI总线规范的精华所在,掌握PCI桥是深入理解PCI体系结构的基础。PCI桥可以连接两条PCI总线,上游PCI总线和下游PCI总线,这两个PCI总线属于同一个PCI总线域,使用PCI桥扩展的所有PCI总线都同属于一个PCI总线域。

其中对PCI设备配置空间的访问可以从上游总线转发到下游总线,而数据传送可以双方向进行。在PCI总线中,还存在一种非透明PCI桥,该桥片不是PCI总线规范定义的标准桥片,但是适用于某些特殊应用,本篇将在第2.5节中详细介绍这种桥片。在本书中,如不特别强调,PCI桥是指透明桥,透明桥也是PCI总线规范定义的标准桥片。

4、HOST处理器

PCI总线规定在同一时刻内,在一颗PCI总线树上有且只有一个HOST处理器。这个HOST处理器可以通过HOST主桥,发起PCI总线的配置请求总线事务,并对PCI总线上的设备和桥片进行配置。

在PCI总线中,HOST处理器是一个较为模糊的概念。在SMP(symmetric multiprocessing)处理器系统中,所有CPU都可以通过HOST主桥访问其下的PCI总线树,这些CPU都可以作为HOST处理器。但是值得注意的是,HOST主桥才是PCI总线树的实际管理者,而不是HOST处理器。

在HOST主桥中,设置了许多寄存器,HOST处理器通过操作这些寄存器管理这些PCI设备。如在x86处理器的HOST主桥中设置了0xCF8和0xCFC这两个I/O端口访问PCI设备的配置空间,而PowerPC处理器的HOST主桥设置了CFG_ADDR和CFG_DATA寄存器访问PCI设备的配置空间。值得注意的是,在PowerPC处理器中并没有I/O端口,因此使用存储器映像寻址方式访问外部设备的寄存器空间。

5、PCI总线的负载

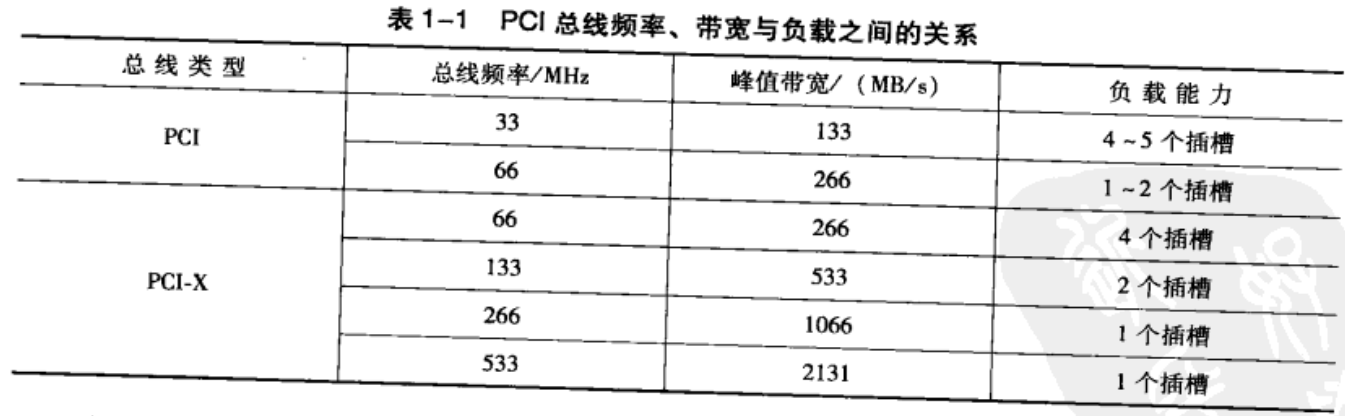

PCI总线的所能挂接的负载与总线频率相关,其中总线频率越高,所能挂接的负载越少。下文以 PCI总线和PCI-X总线为例说明总线频率、峰值带宽和负载能力之间的关系,如表1‑1所示。

由表1‑1所示,PCI总线频率越高,所能挂接的负载越少,但是整条总线所能提供的带宽越大。值得注意的是,PCI-X总线与PCI总线的传送协议略有不同,因此66MHz的PCI-X总线的负载数较大,PCI-X总线的详细说明见第1.5节。当PCI-X总线频率为266MHz和533MHz时,该总线只能挂接一个PCI-X插槽。在PCI总线中,一个插槽相当于两个负载,接插件和插卡各算为一个负载,在表1‑1中,33MHz的PCI总线可以挂接4~5个插槽,相当于直接挂接8~10个负载。

三、参考资料

1、PCI Express体系结构导读

2、https://mp.weixin.qq.com/s/eNNxJpgNxkvgSFA823FJhA

001 PCI Express体系结构(一)的更多相关文章

- 002 PCI Express体系结构(二)

一.PCI总线的信号定义 PCI总线是一条共享总线,在一条PCI总线上可以挂接多个PCI设备.这些PCI设备通过一系列信号与PCI总线相连,这些信号由地址/数据信号.控制信号.仲裁信号.中断信号等多种 ...

- 第II篇PCI Express体系结构概述

虽然PCI总线取得了巨大的成功,但是随着处理器主频的不断提高,PCI总线提供的带宽愈发显得捉襟见肘.PCI总线也在不断地进行升级,其位宽和频率从最初的32位/33MHz扩展到64位/66MHz,而PC ...

- 004 PCI Express体系结构(四)

一.PCI总线的中断机制 PCI总线使用INTA#.INTB#.INTC#和INTD#信号向处理器发出中断请求.这些中断请求信号为低电平有效,并与处理器的中断控制器连接.在PCI体系结构中,这些中断信 ...

- 003 PCI Express体系结构(三)

一.PCI总线的存储器读写总线事务 总线的基本任务是实现数据传送,将一组数据从一个设备传送到另一个设备,当然总线也可以将一个设备的数据广播到多个设备.在处理器系统中,这些数据传送都要依赖一定的规则,P ...

- 000 PCI Express协议入门指南目录

一.001 PCI Express体系结构(一)

- PCI Express

1.1课题研究背景 在目前高速发展的计算机平台上,应用软件的开发越来越依赖于硬件平台,尤其是随着大数据.云计算的提出,人们对计算机在各个领域的性能有更高的需求.日常生活中的视频和图像信息包含大量的数据 ...

- PCI Express(六) - Simple transactions

原文地址:http://www.fpga4fun.com/PCI-Express6.html Let's try to control LEDs from the PCI Express bus. X ...

- PCI Express(五) - Xilinx wizard

原文地址:http://www.fpga4fun.com/PCI-Express5.html Xilinx makes using PCI express easy - they provide a ...

- PCI Express(四) - The transaction layer

原文出处:http://www.fpga4fun.com/PCI-Express4.html 感觉没什么好翻译的,都比较简单,主要讲了TLP的帧结构 In the transaction layer, ...

随机推荐

- Java实验项目三——简单工厂模式

Program: 请采用采用简单工厂设计模式,为某个汽车销售店设计汽车销售系统,接口car至少有方法print(), 三个汽车类:宝马.奥迪.大众 (属性:品牌,价格),在测试类中根据客户要求购买的汽 ...

- IDEA连接数据库出现报错

解决办法 jdbc:mysql://localhost:3306/test?useUnicode=true&characterEncoding=UTF-8&useJDBCComplia ...

- 【重学Java】多线程进阶(线程池、原子性、并发工具类)

线程池 线程状态介绍 当线程被创建并启动以后,它既不是一启动就进入了执行状态,也不是一直处于执行状态.线程对象在不同的时期有不同的状态.那么Java中的线程存在哪几种状态呢?Java中的线程 状态被定 ...

- 备战-Java 容器

备战-Java 容器 玉阶生白露,夜久侵罗袜. 简介:备战-Java 容器 一.概述 容器主要包括 Collection 和 Map 两种,Collection 存储着对象的集合,而 Map 存储着k ...

- 配置Mac 终端高亮

mac下所有vim的配色方案的样式. 下面讲解如何设置这些好看的配色 首先:在终端输入 vim ~/.bash_profile 查看是否有上面提到的某些配色,所有配色均是以.vim结束的,果有的话,再 ...

- python使用笔记21--发邮件

发邮件需要第三方模块 pip install yamail 1 #import yagmail #--别人写的,发中文附件的时候是乱码 2 import yamail #牛牛基于yagmail改的 3 ...

- 用EXCEL打开CSV文件

1.打开EXCEL 2.数据--自文本--选择对应的CSV文件 3.设置表头所在的行(例如17行为表头)则输入17 4.确定分隔符 5.单击"确定"即可

- 简单梳理 ES6 函数

箭头函数 箭头函数提供了一种更加简洁的函数书写方式.基本语法是 参数 => 函数体 基本用法: var f = v => v; //等价于 var f = function(a){ ret ...

- 【路径规划】 Optimal Trajectory Generation for Dynamic Street Scenarios in a Frenet Frame (附python代码实例)

参考与前言 2010年,论文 Optimal Trajectory Generation for Dynamic Street Scenarios in a Frenet Frame 地址:https ...

- 前端开发入门到进阶第三集【Jsonp】

/* $.ajax({ type : "get", url : "${loginInfo.SSO_BASE_URL }/user/token/" + token ...