VerilogHDL可综合设计的注意事项

可综合的语法已经记录得差不多了,剩下一些遗留的问题,在这里记录一下吧。

一、逻辑设计

(1)组合逻辑设计

下面是一些用Verilog进行组合逻辑设计时的一些注意事项:

①组合逻辑可以得到两种常用的RTL 级描述方式。第一种是always 模块的触发事件为电平敏感信号列表;第二种就是用assign 关键字描述的数据流赋值语句。

②always 模块的敏感表为电平敏感信号的电路可几乎可以完成对所有组合逻辑电路的建模。always模块的敏感列表为所有判断条件信号和输入信号,但一定要注意敏感列表的完整性(注意通配符*的使用)。

由于赋值语句有阻塞赋值和非阻塞赋值两类,建议读者使用阻塞赋值语句“=”,原因将在“阻塞赋值和非阻塞赋值”中(现在还没有写)进行说明。

always 模块中的信号必须定义为reg 型,不过最终的实现结果中并没有寄存器。这是由于在组合逻辑电路描述中,将信号定义为reg 型,只是为了满足语法要求。

③assign 语句的描述,利用条件符“?”可以描述一些相对简单的组合逻辑电路,左边的赋值信号只能被定义为wire 型。当组合逻辑比较复杂时,需要很多条语句assign 语句或者多重嵌套“?”,使得代码可读性极差,因此此时推荐always组合逻辑建模方式。

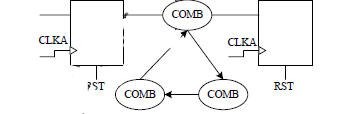

④设计时要注意不要出现组合逻辑环路:

不要在组合逻辑中引入环路,在组合逻辑中引入环路会导致电路产生振荡、毛刺以及冲突等问题,从而降低设计的稳定性和可靠性,此外,环回逻辑的延时完全依靠组合逻辑门延迟和布线延迟。一旦这些传播时延有所变化,则环路的整体逻辑将彻底失效。其次,环路的时序分析是个死循环过程。目前的EDA 开发工具为了计算环路的时序逻辑都会主动割断时序路径,引入许多不确定的因素。因此要彻底避免环路。

(2)时序逻辑设计

①时序电路的行为决定了其只能通过always 块语句实现,通过关键词“posedge”和“negedge”来捕获时钟信号的上升沿和下降沿。在always 语句块中可以使用任何可综合的标志符。

②在描述时序电路的always 块中的reg 型信号都会被综合成寄存器,这是和组合逻辑电路所不同的。

③时序逻辑中推荐使用非阻塞赋值“<=”,原因将后面详细说明。

④时序逻辑的敏感信号列表只需要加入所用的时钟触发沿即可,其余所有的输入和条件判断信号都不用加入,这是因为时序逻辑是通过时钟信号的跳变沿来控制的。

二、锁存器

锁存器是个“奇葩”的器件,在FPGA逻辑设计中很避讳;在ASIC设计中,以前很喜欢(因为面积小),现在不是很喜欢了。在这里就记录一下关于锁存器的一些事项吧。

(1)锁存器的概述

①锁存器的详细CMOS电路结果在前面电路基础章节中已经有描述,这里不详细描述它的结构,详情请挫这个链接:

http://www.cnblogs.com/IClearner/p/6443539.html。

②锁存器是一种对脉冲电平敏感的存储单元电路,可以在特定输入脉冲电平作用下改变状态,其本身也是一类常用的逻辑单元,有着特定的需求。

③锁存器在数据未锁存时,输出端的信号随输入信号变化,就像信号通过一个缓冲器一样,一旦锁存信号有效,则数据被锁住,输入信号不起作用。因此,锁存器也被称为透明锁存器,指的是不锁存时输出对于输入是透明的。

④锁存器和寄存器都是数字电路的基本存储单元,但锁存器是电平触发的存储器,触发器是边沿触发的存储器。

本质上,锁存器和D 触发器的逻辑功能是基本相同的,都可存储数据,且锁存器所需的门逻辑更少,具备更高的集成度。

⑤锁存器具备下列三个缺点:

·对毛刺敏感,不能异步复位,因此在上电后处于不确定的状态。

·锁存器会使静态时序分析变得非常复杂,不具备可重用性。

·在FPGA/CPLD芯片中,基本的单元是由查找表和触发器组成的,若生成锁存器反而需要更多的资源。

(2)锁存器的产生

①锁存器产生于组合逻辑的设计中,在基于always的组合逻辑描述语句中,可能产生锁存器的情况具体可分为两种:其一是在if 语句中,另一种是在case 语句中。

②在always 块中使用if 语句,但缺乏else 分支而造成锁存器。

③在always 块中使用case 语句,由于缺乏default 分支而造成锁存器。

④如果用到if 语句,最好有else 分支;如果用到case 语句,最好有default 语句。即使需要锁存器,也通过else 分支或default 分支来显式说明。

(3)锁存器的应用

①在总线应用上,锁存器能提高驱动能力、隔离前后级。

②地址锁存器、数据锁存器、复位信号锁存器;门控时钟钟的应用等等。

三、设计思维

这个设计思维本来属于设计技巧里面的,放在这里说明,是为了告诉自己,在进行电路描述的时候, 是基于这些准则的,在设计时能够根据这些基本准则进行优化电路。下面是常见的设计思维,主要是基于FPGA的,关于ASIC其他设计技巧或者设计思维,我记录在了“技巧”篇。

(1)速度面积互换准则

①速度与面积是设计时常考虑的的一个问题,因此在设计的时候要考虑怎么在这二者之间的权衡。当然,现在功耗也与速度、面积成为需要考虑的重大因素之一。

②面积和速度互换的具体操作很多,比如模块复用、乒乓操作、串并转换以及流水线操作等。在设计技巧策略和技巧那一章节中将会进行叙述。

③串并转换乘法器:假设数据速率是乘法器模块处理速度的3 倍,那么由于乘法器模块的数据吞吐量满足不了要求,在这种情况下,就利用面积换速度的思想,复制3 个乘法器模块。首先将输入数据进行串并转换,然后利用这3 个模块并行处理所分配到的数据,最后将处理结果并串转换,达到数据速率的要求。

如下图所示:

(2)FPGA中的设计思维

①信号反相的处理策略

在处理反相信号时,设计时应尽可能地遵从分散反相原则。即应使用多个反相器分别反相,每个反相器驱动一个负载,这个原则无论对时钟信号还是对其它信号都是适用的。

因为在FPGA设计中,反相是被吸收到CLB或IOB中的,使用多个反相器并不占用更多的资源,而使用一个反相器将信号反相后驱动多个负载却往往会多占资源,而且延迟也增加了。

②首先,如果输入信号需要反相,则应尽可能地调用输入带反相功能的符号,而不是用分离的反相器对输入信号进行反相。

因为在使用自带反相功能的器件中,由于函数发生器用查表方式实现逻辑,反相操作是不占资源的,也没有额外延迟;而分开使用不同逻辑使用反相操作实现,从而消耗额外的资源,增加额外的延迟。

③其次,如果一个信号反相后驱动了多个负载,则应将反相功能分散到各个负载中实现,而不能采用传统TTL电路设计,采用集中反相驱动多个负载来减少所用的器件的数量。

因为在FPGA设计中,集中反相驱动多个负载往往会多占一个逻辑块或半个逻辑块,而且延迟也增加了。分散信号的反相往往可以与其它逻辑在同一单元内完成而不消耗额外的逻辑资源。

VerilogHDL可综合设计的注意事项的更多相关文章

- mysql索引设计的注意事项

mysql索引设计的注意事项 目录 一.索引的重要性 二.执行计划上的重要关注点 (1).全表扫描,检索行数 (2).key,using index(覆盖索引) (3).通过key_len确定究竟使用 ...

- mysql索引设计的注意事项(大量示例,收藏再看)

mysql索引设计的注意事项(大量示例,收藏再看) 目录 一.索引的重要性 二.执行计划上的重要关注点 (1).全表扫描,检索行数 (2).key,using index(覆盖索引) (3).通过ke ...

- 游戏AI的综合设计

原地址:http://www.cnblogs.com/cocoaleaves/archive/2009/03/23/1419346.html 学校的MSTC要出杂志,第一期做游戏专题,我写了一下AI, ...

- C语言程序设计:综合设计实验一(设计一个文字游戏)

目录 C语言程序设计:综合设计实验一(设计一个文字游戏) 1.实验要求 2.设计思路 3.源码 4.后话 C语言程序设计:综合设计实验一(设计一个文字游戏) 1.实验要求 (1) 设计一个文字游戏,通 ...

- USB2.0学习笔记连载(六):USB2.0硬件设计需要注意事项

笔者在设计USB2.0时找到了一个官方给的硬件设计正确设计指南,其中有些内容还挺nice的.不单单只是USB的设计,其中有些思想可以应用到其他的场合中. 对于USB2.0而言,全速状态下可以达到480 ...

- FPGA设计的注意事项

设计文档 一个完整的软件是由程序. 数据和文档三部分组成的. 在FPGA电路设计中, 撰写完善的设计文档是非常重要的. 对于一个比较复杂的设计来说, 各个子单元的功能各不相同, 实现的方法也不一样,各 ...

- hbase rowkey设计的注意事项

充分利用有序性 1.1 如果要scan操作,且不是很频繁,可以利用rowkey的有序性将需要一起扫描的数据放到一起.例如直接用时间戳.这样就可以按时间scan了.这个只要是简单的全表扫描都行. 1.2 ...

- Java11-java基础语法(十)类设计综合案例

Java11-java语法基础(十)类设计综合案例 一.类综合设计方法 1.类设计步骤 (1)分析数据成员 (2)分析成员方法和构造方法 (3)画出类图 (4)编码测试 2.具体问题 1)分析数据成员 ...

- 循序渐进开发WinForm项目(1) --数据库设计和项目框架的生成

随笔背景:在很多时候,很多入门不久的朋友都会问我:我是从其他语言转到C#开发的,有没有一些基础性的资料给我们学习学习呢,你的框架感觉一下太大了,希望有个循序渐进的教程或者视频来学习就好了. 其实也许我 ...

随机推荐

- AS3批量替换文件

在做项目时,经过会遇到资源替换问题.比如配音公司,提供了一批八九百个配音MP3文件,用到后面却发现有些配音不能正常使用.可能是十几个,也可能是一两百个.只能是配音公司重新提供.因为之前的配音资源,已经 ...

- web存储之webstorage

web存储分类 客户端和服务端 认识web存储 随着web应用的发展,是的客户端存储的用途越来越多,然而实现客户端端存储的方式也是越来越多样化.最简单最兼容的方式就是cookie,但作为真正的客户端存 ...

- angularJS loading 载入画面

在请求网络的时候,显示loading画面 1. 使用http的interceptor,截断处理所有的http请求和响应,以及错误.在request的时候设置$rootScope.loading=Tru ...

- 解决ionic在Android和iOS的一些样式上的冲突

//设置默认返回按钮的文字 $ionicConfigProvider.backButton.previousTitleText(false).text('返回'); // 设置全局 $http 超时 ...

- Java基础语法实例(2)——实习第二天

来到广州实习的第二天,广州好潮湿,这就是我的感觉,手表里面都开始产生了水雾,这就尴尬了...每天不断的雨.好吧,尽管我很喜欢这里的树,但是我以后应该也不会再来广州了,其实也说不准.想起了<谁动了 ...

- BigDecimal四舍五入使用总结

//BigDecimal四舍五入double f1 = new BigDecimal(1).setScale(2,RoundingMode.HALF_UP).doubleValue();//转化成字符 ...

- jq和js插件的各个文件夹里放置的内容

1. demo文件夹,存放各种实例. 2. dist文件夹,全称是distribution.在某些框架中,因为开发和发布的内容或者代码形式是不一样的(比如利用Grunt压缩等等),这时候就需要一个存放 ...

- 【LeetCode】258. Add Digits

题目: Given a non-negative integer num, repeatedly add all its digits until the result has only one di ...

- 【Android Developers Training】 106. 创建并检测地理围栏

注:本文翻译自Google官方的Android Developers Training文档,译者技术一般,由于喜爱安卓而产生了翻译的念头,纯属个人兴趣爱好. 原文链接:http://developer ...

- 5.request对象详解

可以通过request对象获取表单提交的值,get或者post方式都是可以得 例子:login.jsp表单 <%@ page language="java" import=& ...