FPGA-Xilinx原语调用之ODDR

记录背景:最近由于想实现GMIItoRGMII的功能,因此需要调用ODDR原语。

ODDR:Dedicated Dual Data Rate (DDR) Output Register

通过ODDR把两路单端的数据合并到一路上输出,上下沿同时输出数据,上沿输出a路下沿输出b路;如果两路输入信号一路恒定为1,一路恒定为0,那么输出的信号实际上就是输入的时钟信号。

调用的Verilog语句是:

// ODDR: Output Double Data Rate Output Register with Set, Reset

// and Clock Enable.

// 7 Series

// Xilinx HDL Language Template, version 2017.4 ODDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT('b0), // Initial value of Q: 1'b0 or 'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_inst (

.Q(Q), // 1-bit DDR output

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D1(D1), // 1-bit data input (positive edge)

.D2(D2), // 1-bit data input (negative edge)

.R(R), // 1-bit reset

.S(S) // 1-bit set

); // End of ODDR_inst instantiation

模式解释:

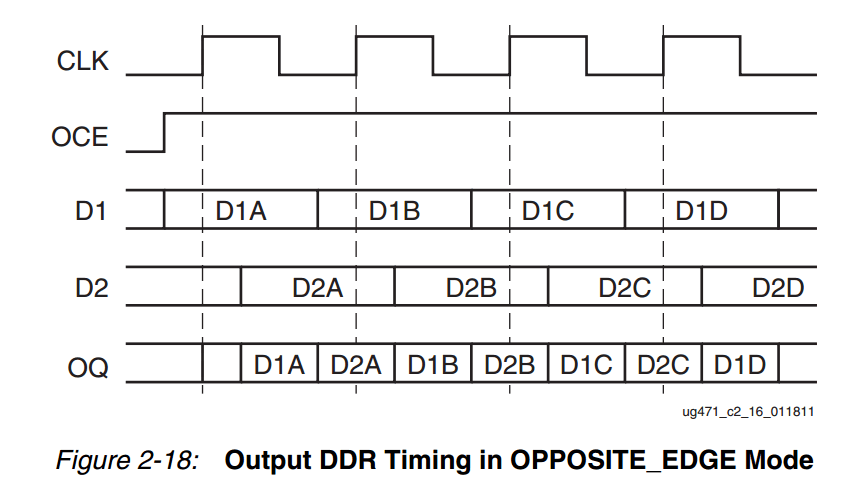

OPPOSITE_EDGE模式:

在此模式中,时钟边沿被用来以两倍的吞吐量从FPGA逻辑中捕获数据。这种结构与virtex-6的实现比较相似。两个输出都提供给IOB的数据输入或者三态控制输入。

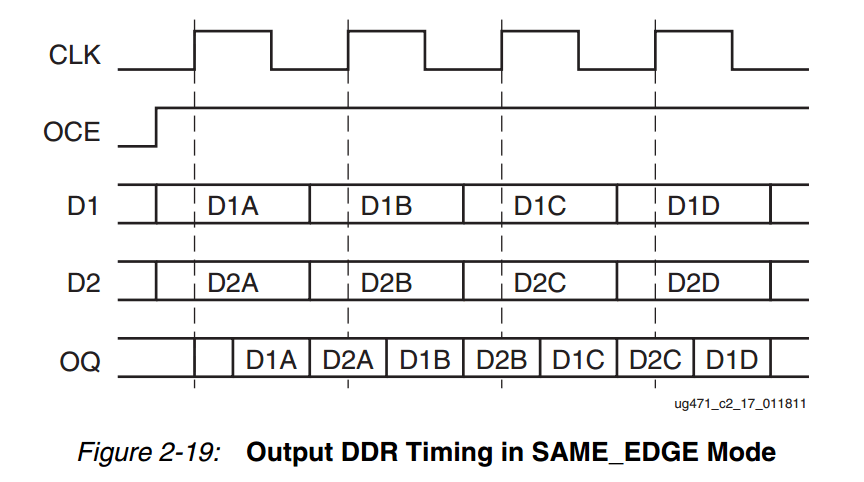

SAME_EDGE模式:

在此模式下,数据可以在相同的时钟边沿从给IOB。相同的时钟沿将数据送给IOB可以避免建立时间违规,并允许用户使用最小的寄存器来执行更高的DDR频率来进行寄存器的延迟,而不是使用CLB寄存器。

注意:

1、set和reset不能同时置位;

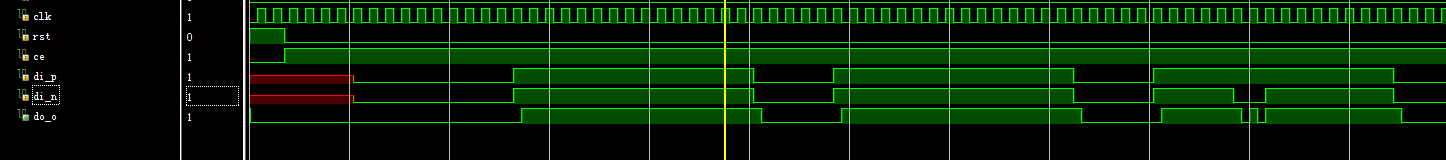

2、ODDR原语的复位需要约12个clock,第一次输入的数据可能会有问题(亲测),[由于公司网络的原因,无法上传图片],但亲测是如此。

修改代码前:

wire oddr_do_test; oddr_test oddr_test

(.clk(tx_clk),

.rst(rst),

.ce(~rst),

.di_p(tx_en),

.di_n(tx_er),

.do_o(oddr_do_test)

);

增加如下代码:

wire oddr_do_test; reg [:]tx_en_d;

reg [:]tx_er_d;

always @ (posedge tx_clk)

begin

tx_en_d <= {tx_en_d[:],tx_en};

tx_er_d <= {tx_er_d[:],tx_er};

end oddr_test oddr_test

(.clk(tx_clk),

.rst(rst),

.ce(~rst),

.di_p(tx_en_d[]),

.di_n(tx_er_d[]),

.do_o(oddr_do_test)

);

FPGA-Xilinx原语调用之ODDR的更多相关文章

- 58.xilinx原语DCM,PLL的使用

DCM_BASE 基本数字时钟管理模块的缩写,是相伴和频率可配置的数字锁相环电路,常用于FPGA系统中复杂的时钟管理.如需要频率和相位动态配置,则可以选用DCM_ADV原语,如需要相位动态偏移,可使用 ...

- Xilinx原语学习之时钟资源相关原语

一直来,都是使用Vivado中自带的GMIItoRGMII IP核来完成GMII转RGMII的功能:尽管对GMII及RGMII协议都有一定的了解,但从没用代码实现过其功能.由于使用IP时,会涉及到MD ...

- [原创][FPGA]Quartus中调用Modelsim波形仿真步骤说明

0. 简介 在使用QuartusII软件的过程中,经常地需要跑仿真,那么说到仿真就不得不说Modelsim这个仿真软件了,我们这里介绍下该软件在QuartusII中的使用方法. 1. 建立Quartu ...

- Xilinx器件原语

原语,其英文名为primitive,是FPGA厂商针对其器件特征开发的一系列常用模块的名称.原语是FPGA芯片中基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等.相当于软件 ...

- FIR调用DSP48E_05

作者:桂. 时间:2018-02-06 17:52:38 链接:http://www.cnblogs.com/xingshansi/p/8423457.html 前言 到目前为止,本文没有对滤波器实 ...

- FPGA开发流程1(详述每一环节的物理含义和实现目标)

要知道,要把一件事情做好,不管是做哪们技术还是办什么手续,明白这个事情的流程非常关键,它决定了这件事情的顺利进行与否.同样,我们学习FPGA开发数字系统这个技术,先撇开使用这个技术的基础编程语言的具体 ...

- FPGA开发流程

需求说明:Verilog设计 内容 :FPGA开发基本流程及注意事项 来自 :时间的诗 原文来自:http://www.dzsc.com/data/2015-3-16/1080 ...

- 【FPGA篇章二】FPGA开发流程:详述每一环节的物理含义和实现目标

欢迎大家关注我的微信公众账号,支持程序媛写出更多优秀的文章 FPGA的开发流程是遵循着ASIC的开发流程发展的,发展到目前为止,FPGA的开发流程总体按照下图进行,有些步骤可能由于其在当前项目中的条件 ...

- FPGA高速ADC接口实战——250MSPS采样率ADC9481

一.前言 最近忙于硕士毕业设计和论文,没有太多时间编写博客,现总结下之前在某个项目中用到的一个高速ADC接口设计部分.ADC这一器件经常用于无线通信.传感.测试测量等领域.目前数字系统对高速数据采集的 ...

随机推荐

- 009_svn配置多仓库与权限控制(Alpha)

1,配置多仓库 实际项目中,我们会同时开发多个项目,通过SVNserve进行仓库监管,但是监管命令只能同时监管一个文件夹,而不能同时监管多个仓库. 解决方法: 可以通过监管总目录来监管所有仓库 SVN ...

- Python 3从入门到精通02-python的简单使用

Python 3中的打印语句和字符串使用: Python中的常见数学运算: 这样的简单基础知识,你需要花5分钟就可以了,很基础的东西.

- AIX用裸设备给表空间添加数据文件

近期在对生产数据库表空间进行扩容,目的是春节期间保证表空间的使用率,不会出现紧急告警信息. 1.查看表空间使用率的SQL语句 col tablespace_name for a16 col SUM_S ...

- php 打印

php 打印功能需要printer.dll文件 扩展下载地址 http://downloads.php.net/pierre/ 这里有很多PHP的扩展

- 设计多选按钮ListChooseView

设计多选按钮ListChooseView 答应某位女屌丝而写的控件,效果还不错,开源给大家^_^! 效果图: 源码: // // ListChooseView.h // ScrollChooseBut ...

- hibernate设置了not-null 为什么无效?

因为设错地方了! 错误--写在了property标签里 <property name="password" type="string" length=&q ...

- Zabbix日常监控之lvs监控

参考博文:http://blog.51cto.com/kaibinyuan/1711863 监控环境的搭建请参考:https://www.cnblogs.com/huangyanqi/p/918780 ...

- if 的一切

第一种语法: if 条件: # @引号是为了把条件和结果分开. 结果1 # 一个Tab或者4个空格 @告诉程序满足上面的if条件才会执行结果1结果2 如果条件为真(True),执行结果1,然后执行结果 ...

- React onPaste 获取粘贴板的值

React 中, 获取 粘贴板的值, 使用下面的方法 console.log(e.clipboardData.getData('Text')); 如果是 JS 中的 onpaste 事件, 则使用 v ...

- MySQL安装俩个不同版本服务出现的问题(1053)

在使用命令mysqld --install servicename --defaults-file='file_name'创建mysql服务时,系统 已提示创建服务成功,但是net start命令提示 ...