全志A40i+Logos FPGA开发板(4核ARM Cortex-A7)硬件说明书(下)

前 言

本文档主要介绍板卡硬件接口资源以及设计注意事项等内容,测试板卡为创龙科技旗下的全志A40i+Logos FPGA开发板。

核心板的ARM端和FPGA端的IO电平标准一般为3.3V,上拉电源一般不超过3.3V,当外接信号电平与IO电平不匹配时,中间需增加电平转换芯片或信号隔离芯片。按键或接口需考虑ESD设计,ESD器件选型时需注意结电容是否偏大,否则可能会影响到信号通信。

核心板CPU、ROM、RAM、电源、晶振等所有器件均采用国产工业级方案,国产化率100%。同时,评估底板大部分元器件亦采用国产工业级方案。

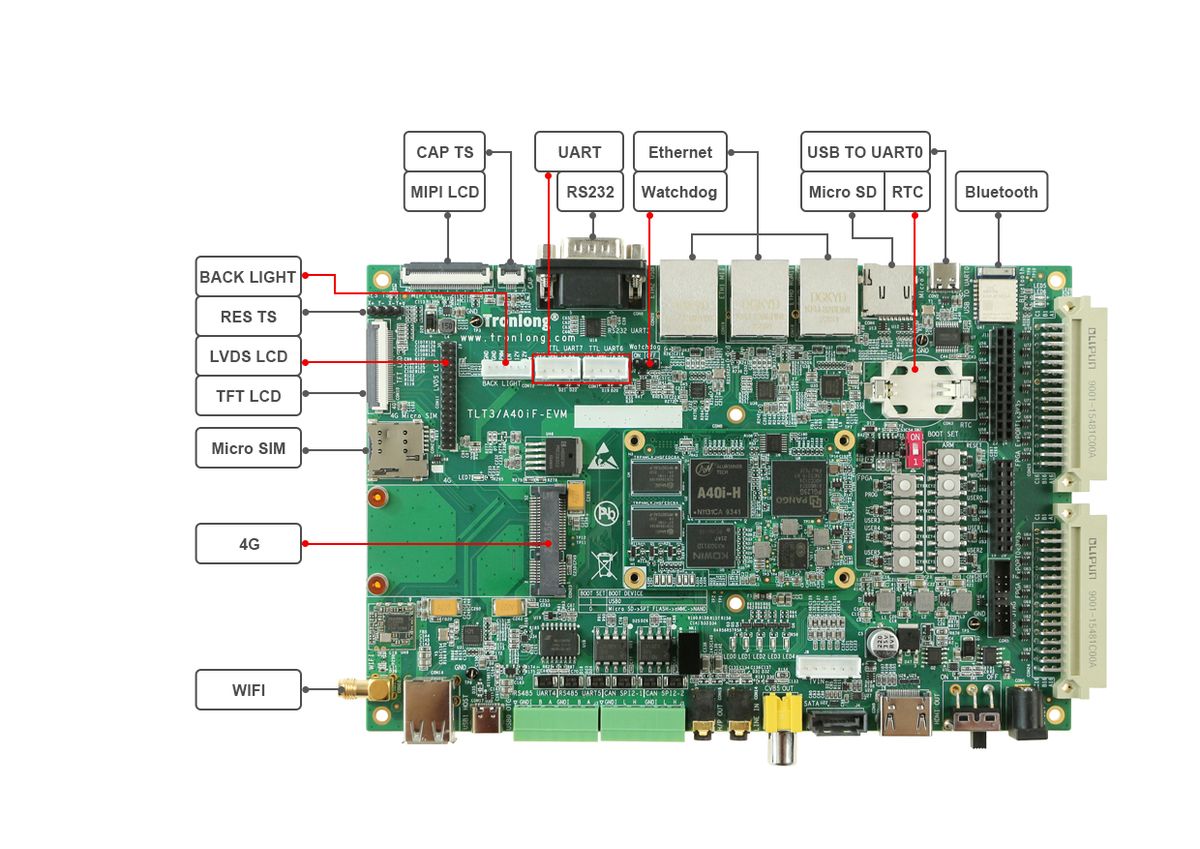

图 1 评估板硬件资源图解1

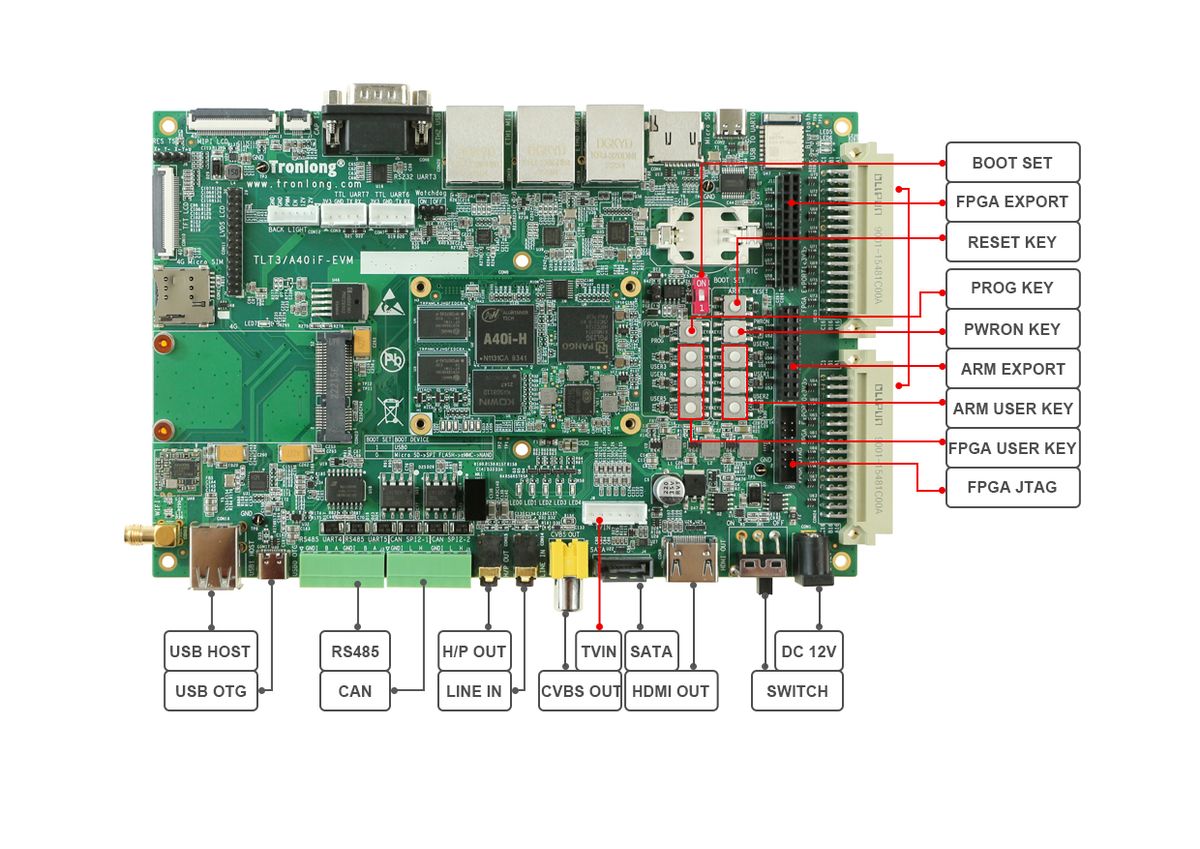

图 1 评估板硬件资源图解1 图 2 评估板硬件资源图解2

图 2 评估板硬件资源图解2MIPI LCD接口

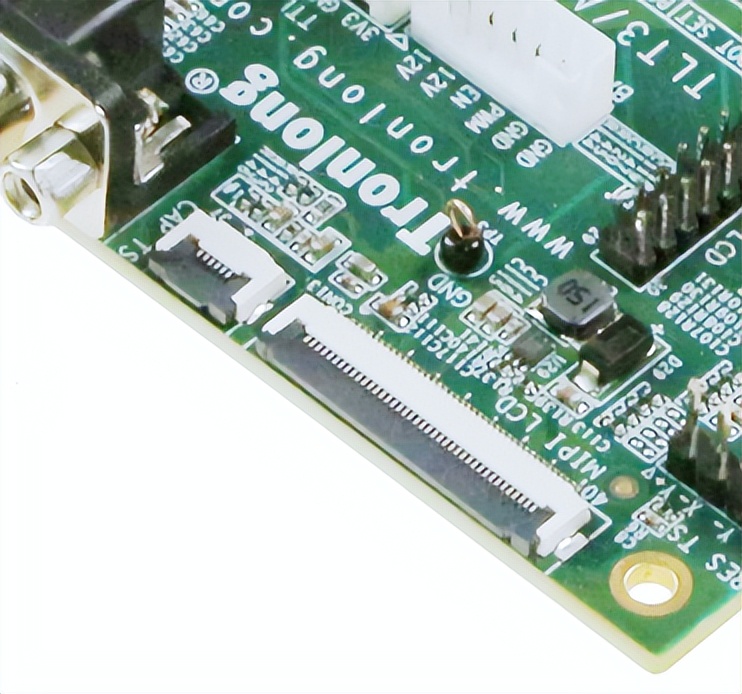

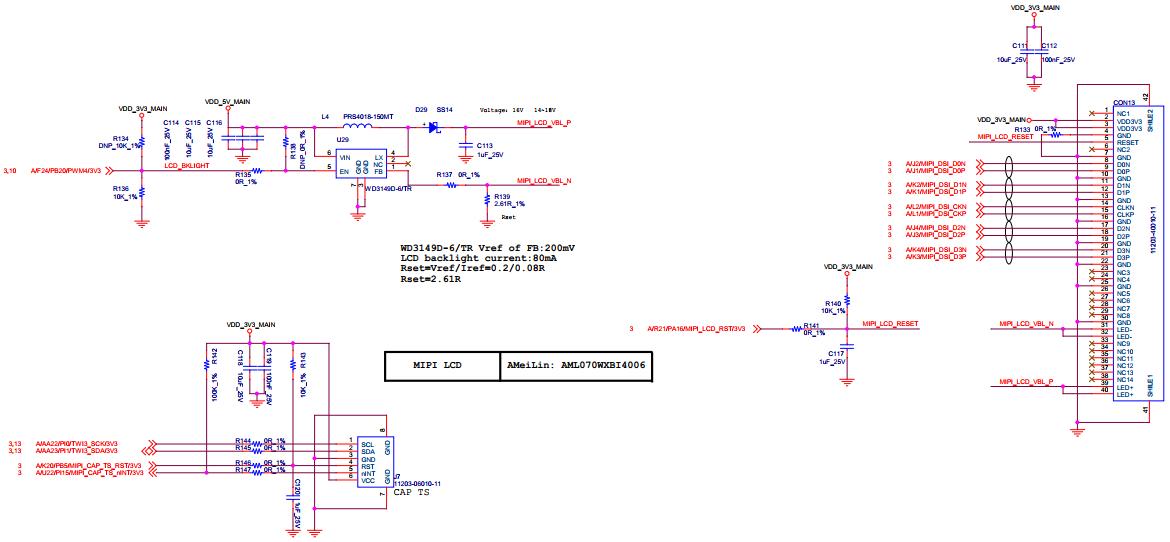

CON13为MIPI LCD接口,采用40pin FFC连接器,间距0.5mm。

J7为MIPI LCD的电容触摸接口CAP TS,采用6pin FFC连接器,间距0.5mm。

图 42

图 42 图 43

图 43设计注意事项:

(1)若CAP TS(J7)的nINT引脚需分配使用其他IO,请使用引脚信号名称包含EINTx字段(支持中断功能)的IO引脚。

TFT LCD接口

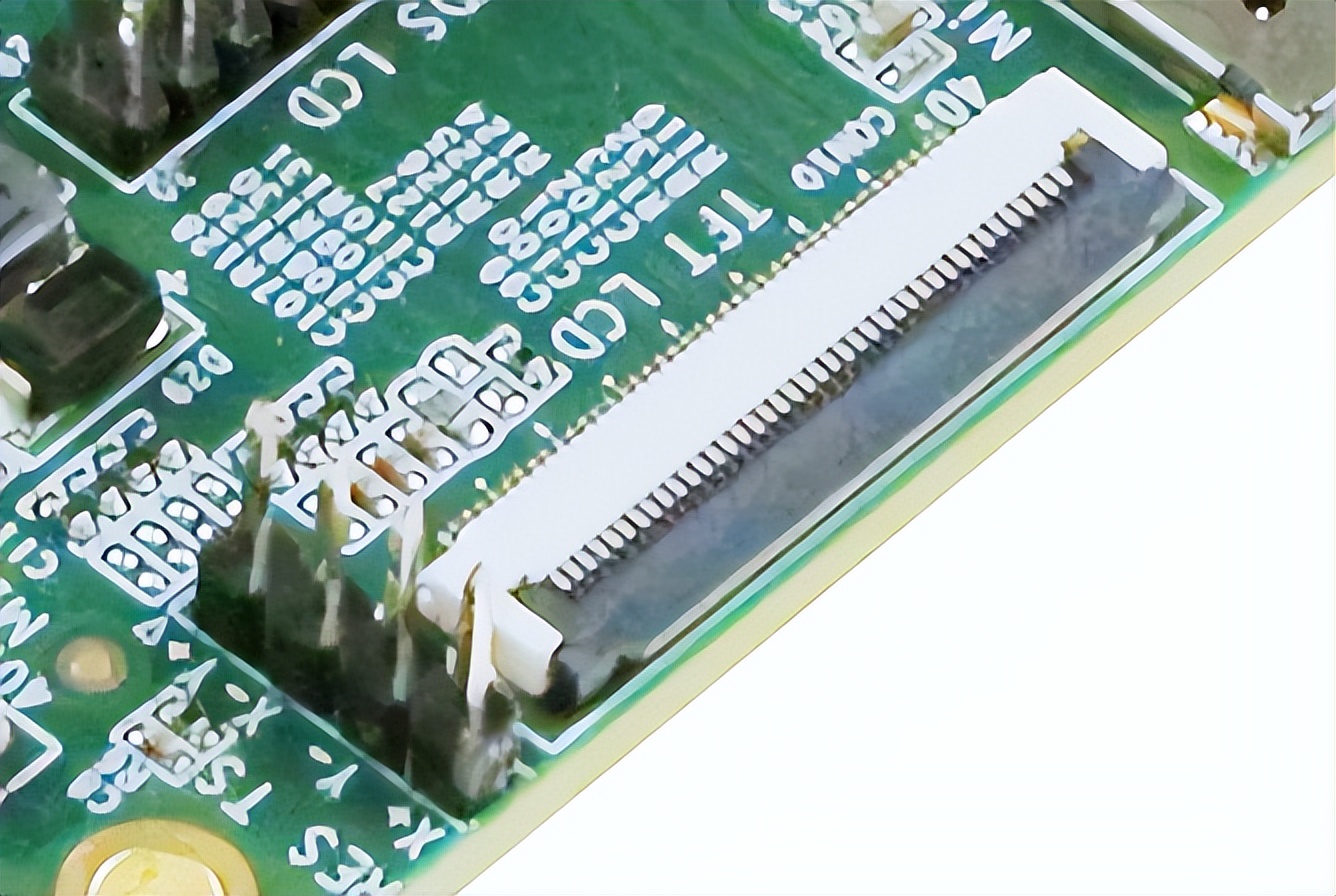

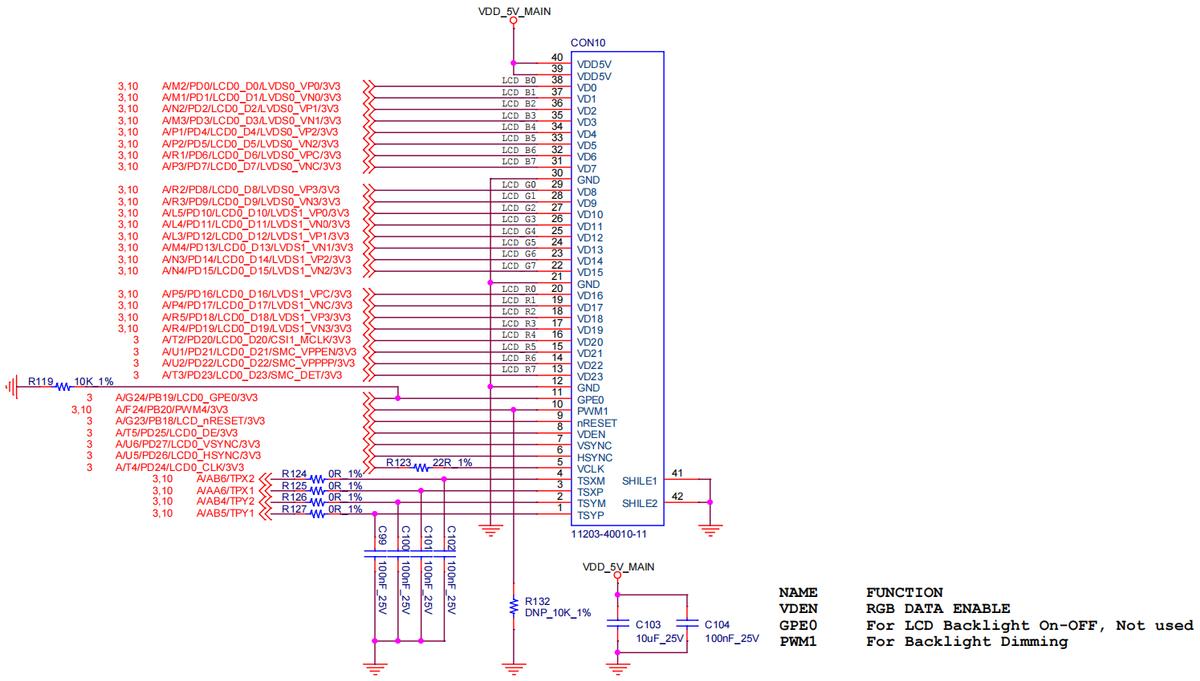

CON10为TFT LCD接口,采用40pin FFC连接器,间距0.5mm。

图 44

图 44 图 45

图 45设计注意事项:

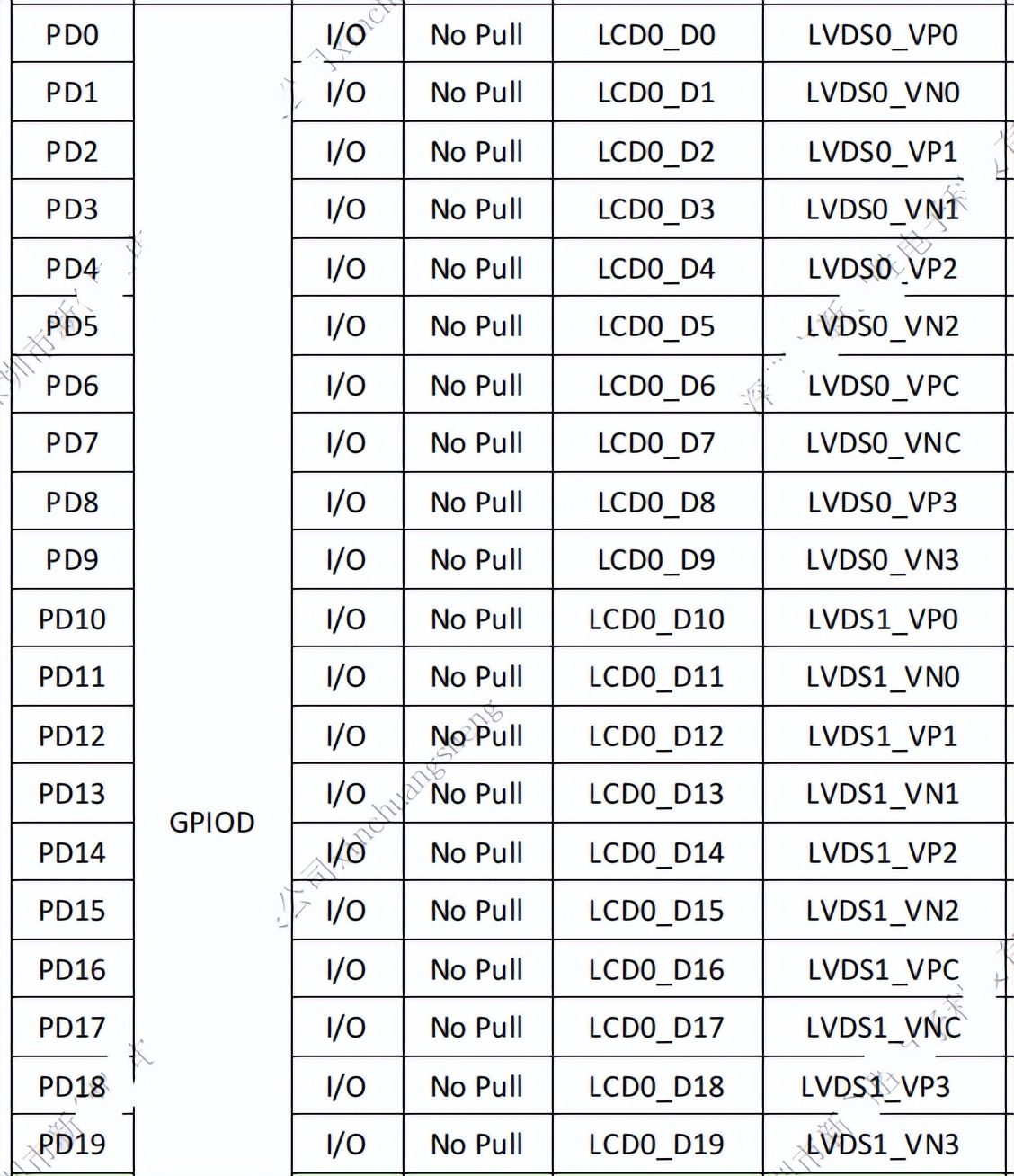

- TFT LCD接口使用的LCD0信号与LVDS0、LVDS1信号为复用关系,如下图所示。

图 46

图 46通过A/F24/PB20/PWM4/3V3引脚输出PWM控制LCD背光,外部预留下拉10K电阻到地。

TFT LCD接口、LVDS LCD接口已同时连接TPX1、TPX2、TPY1、TPY2四线电阻触摸信号,请勿同时连接两种显示设备。

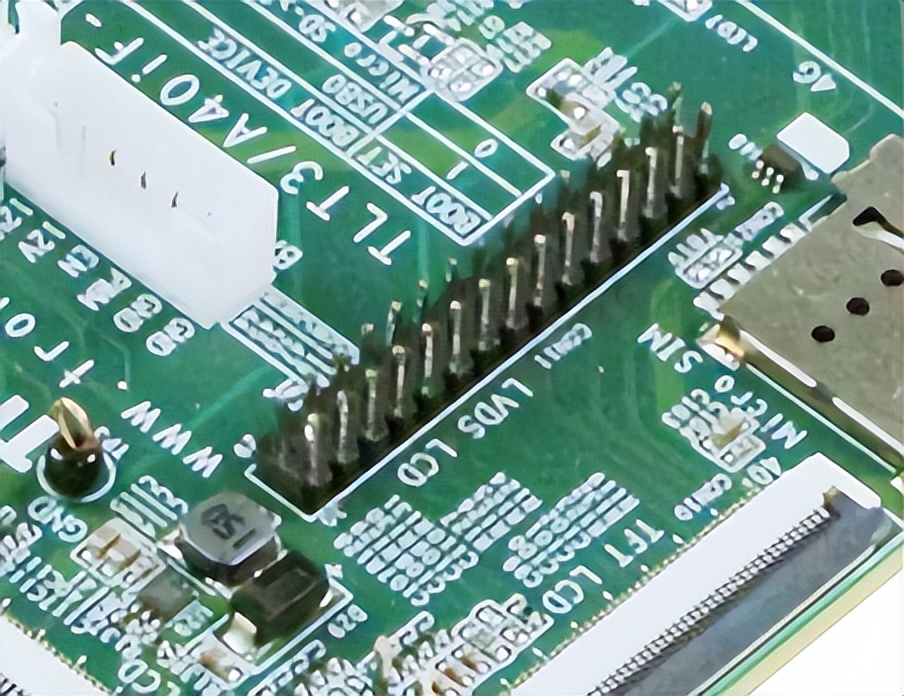

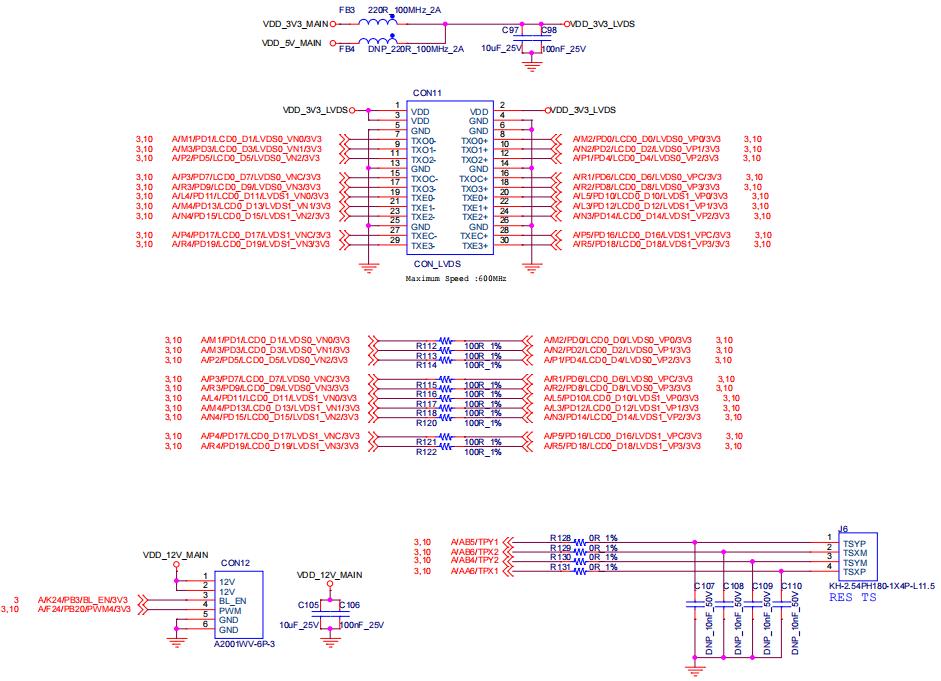

LVDS LCD接口

CON11为双路8bit LVDS LCD接口,采用2x 15pin双排针,间距2.0mm,包含LVDS信号及供电电源。CON12为背光控制接口,采用6pin白色端子座,间距2.54mm。J6为电阻触摸屏接口,采用4pin排针,间距2.54mm。

图 47

图 47 图 48

图 48设计注意事项:

- LVDS0、LVDS1信号与LCD0信号为复用关系。

- LVDS LCD接口、TFT LCD接口同时连接了TPX1、TPX2、TPY1、TPY2四线电阻触摸信号,请勿同时连接两种显示设备。

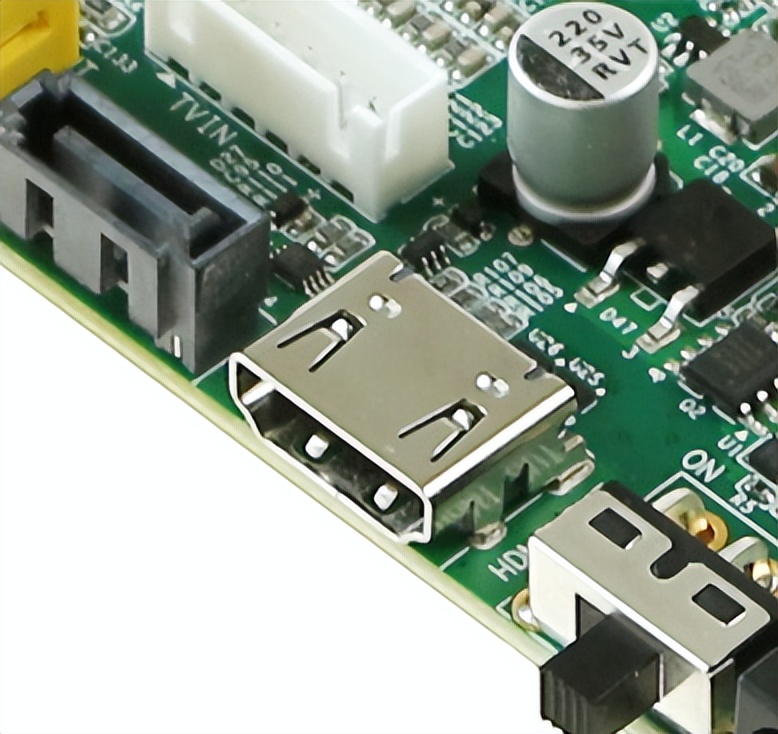

HDMI OUT接口

CON9为HDMI OUT视频输出接口,采用标准19pin HDMI座。

图 49

图 49设计注意事项:

- HDMI座子的HPLG信号需下拉38.3K电阻到地,当外部设备接入时,会将此信号拉高。

- A/V9/HDMI_HSCL/3V3和A/W9/HDMI_HSDA/3V3的IO电平为3.3V,需转换为5V电平再引出至HDMI座。

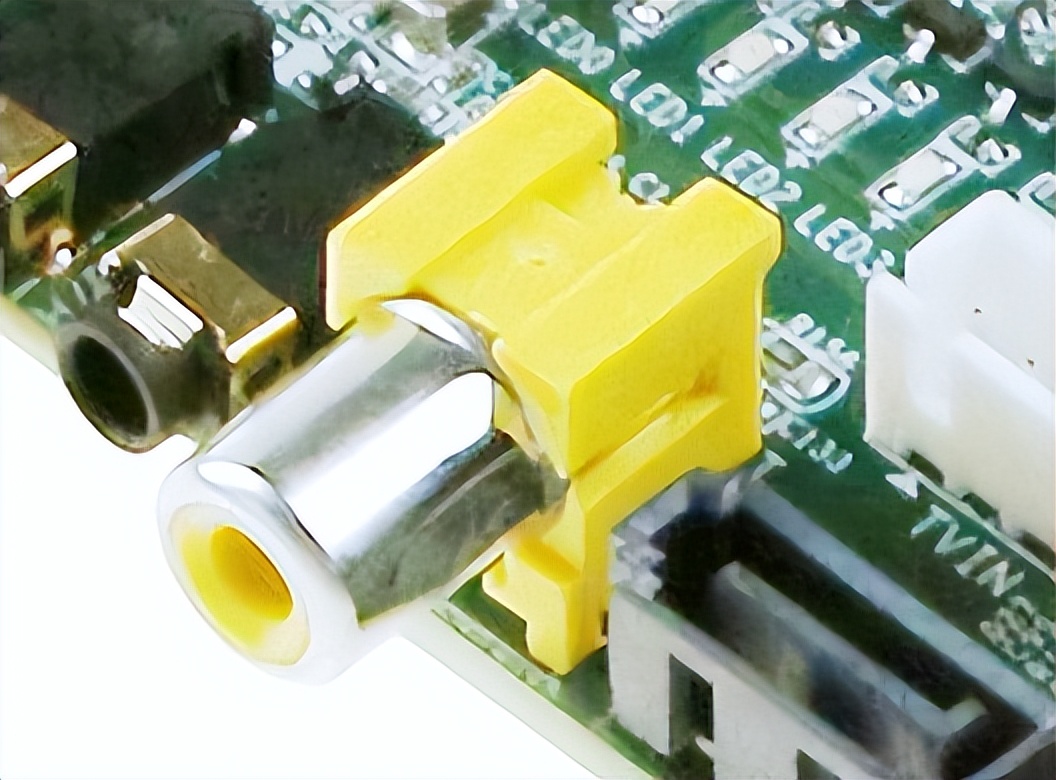

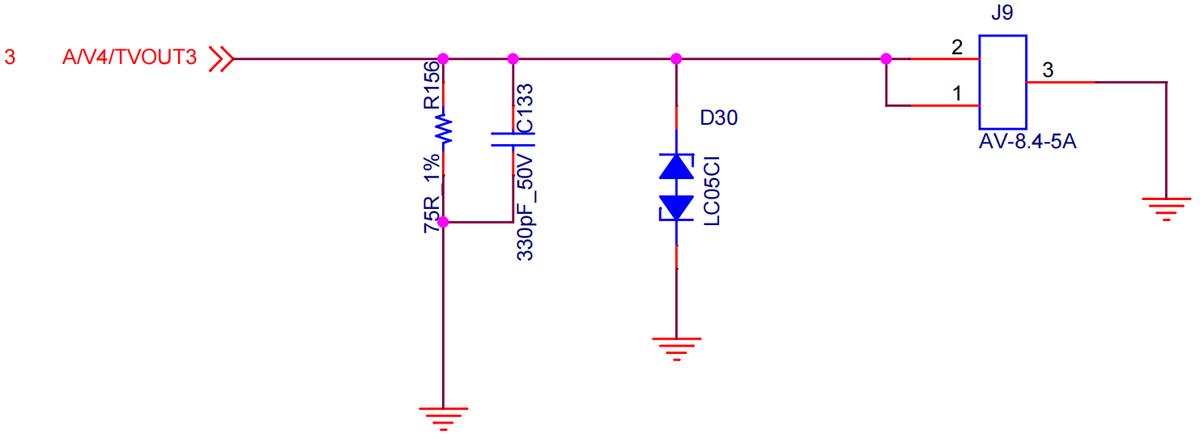

CVBS OUT接口

J9为CVBS OUT接口,由TVOUT3引出,采用RCA莲花座。

图 52

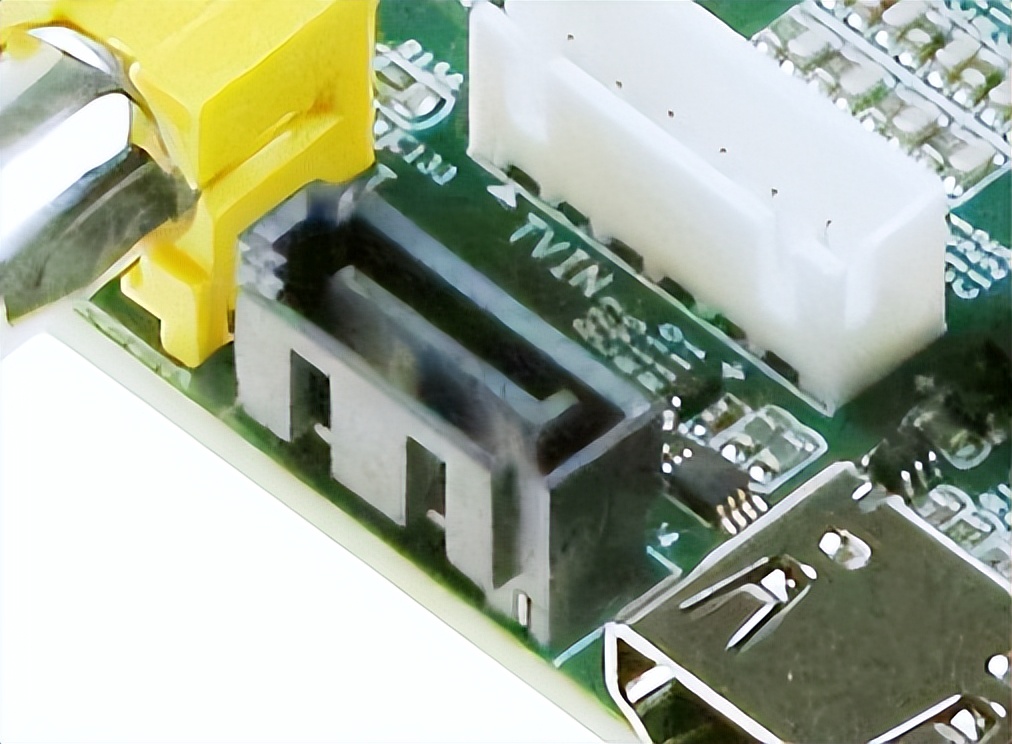

图 52TVIN接口

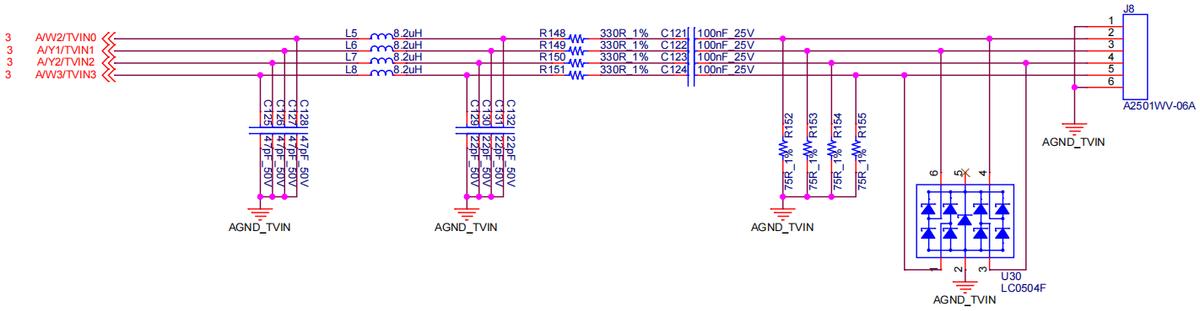

J8为TVIN接口,由TVIN0、TVIN1、TVIN2、TVIN3引出,采用6pin 2.54mm白色端子形式。

图 53

图 53 图 54

图 54USB接口

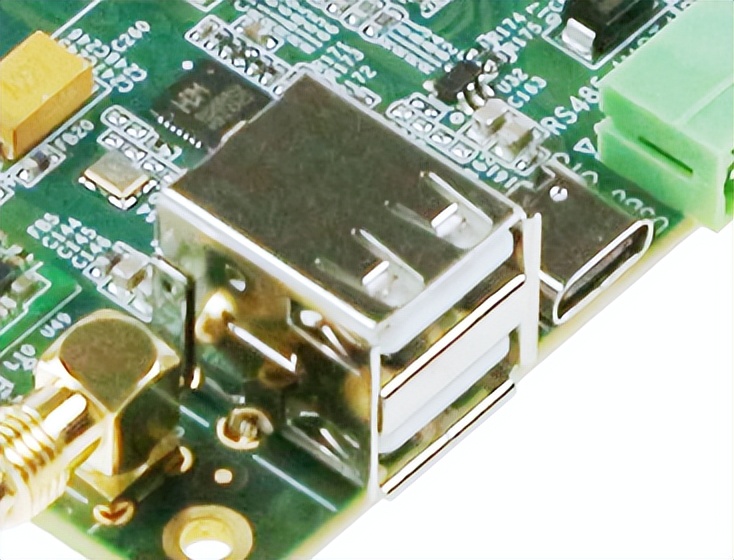

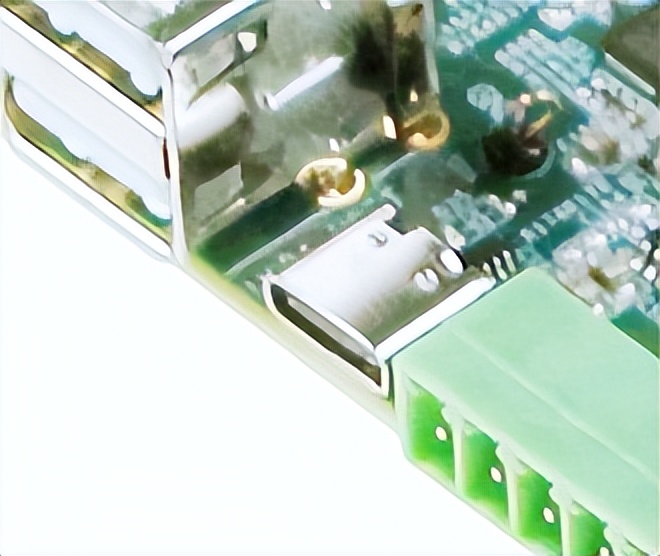

CON16(USB1 HOST)为USB2.0 HOST接口,采用双层Type-A型连接器;CON17(USB0 OTG)为USB2.0 OTG接口,采用Type-C连接器。

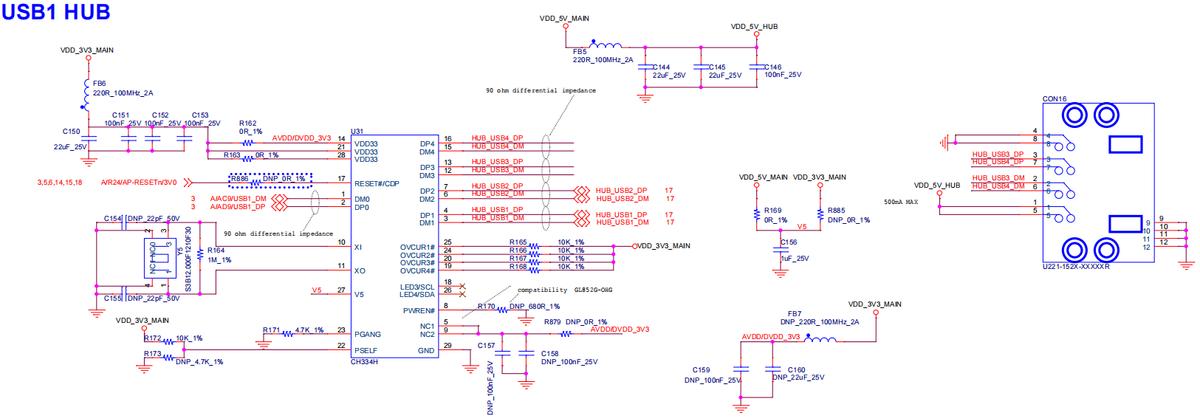

USB1 HOST接口

评估底板通过USB HUB芯片将USB1总线拓展为4路USB HOST总线,将其中2路引出至USB1 HOST接口。

图 55

图 55 图 56

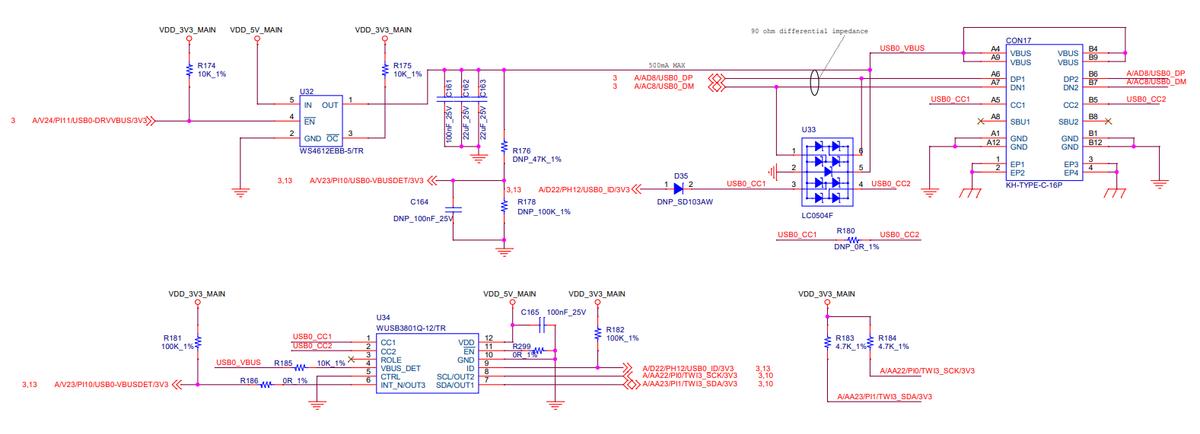

图 56USB0 OTG接口

USB0 OTG接口直接由USB0总线引出。

图 57

图 57 图 58

图 58Ethernet接口

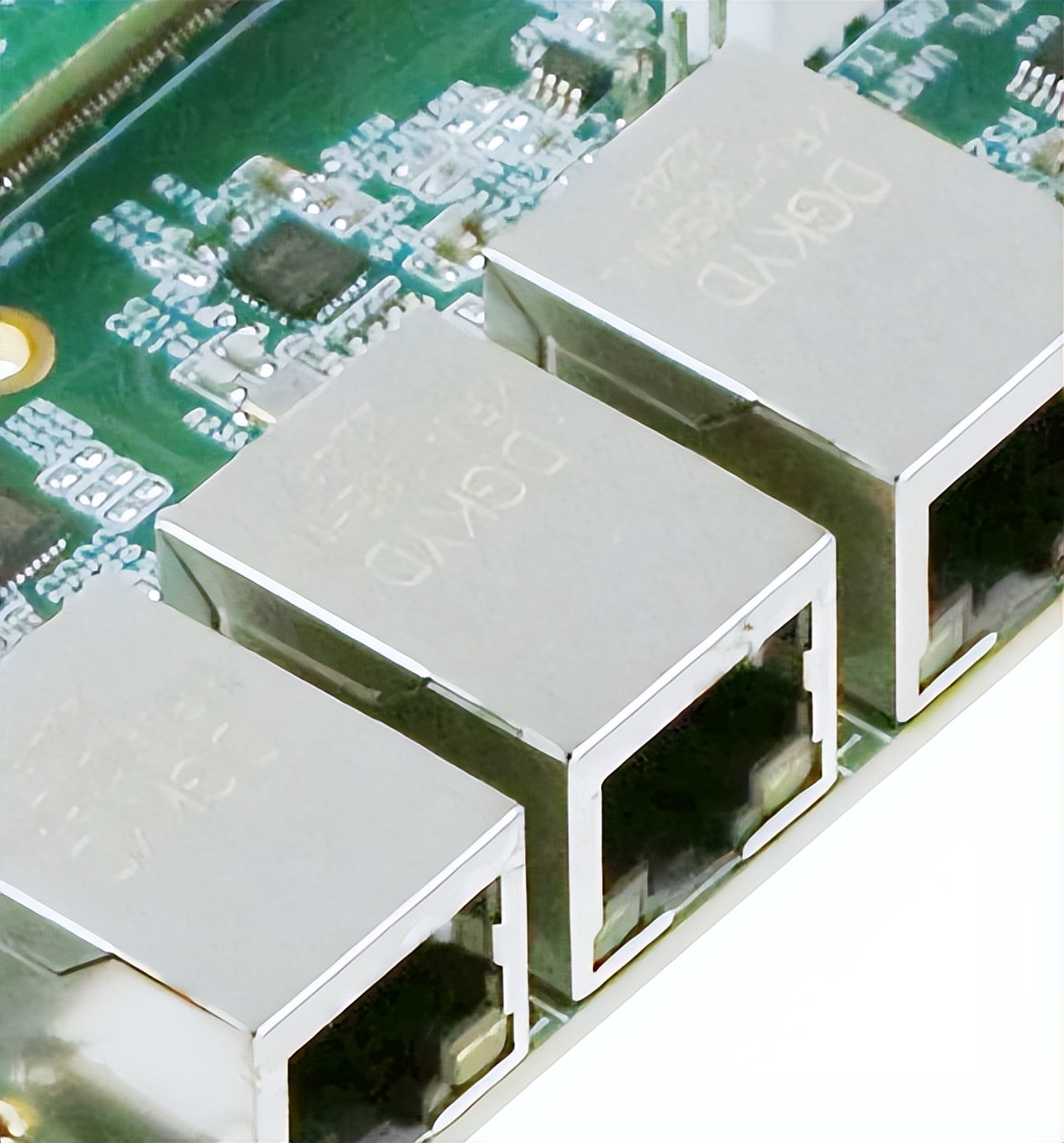

评估板包含1个ETH0 RGMII千兆网口、1个ETH1 MII百兆网口和1个ETH2 USB百兆网口。

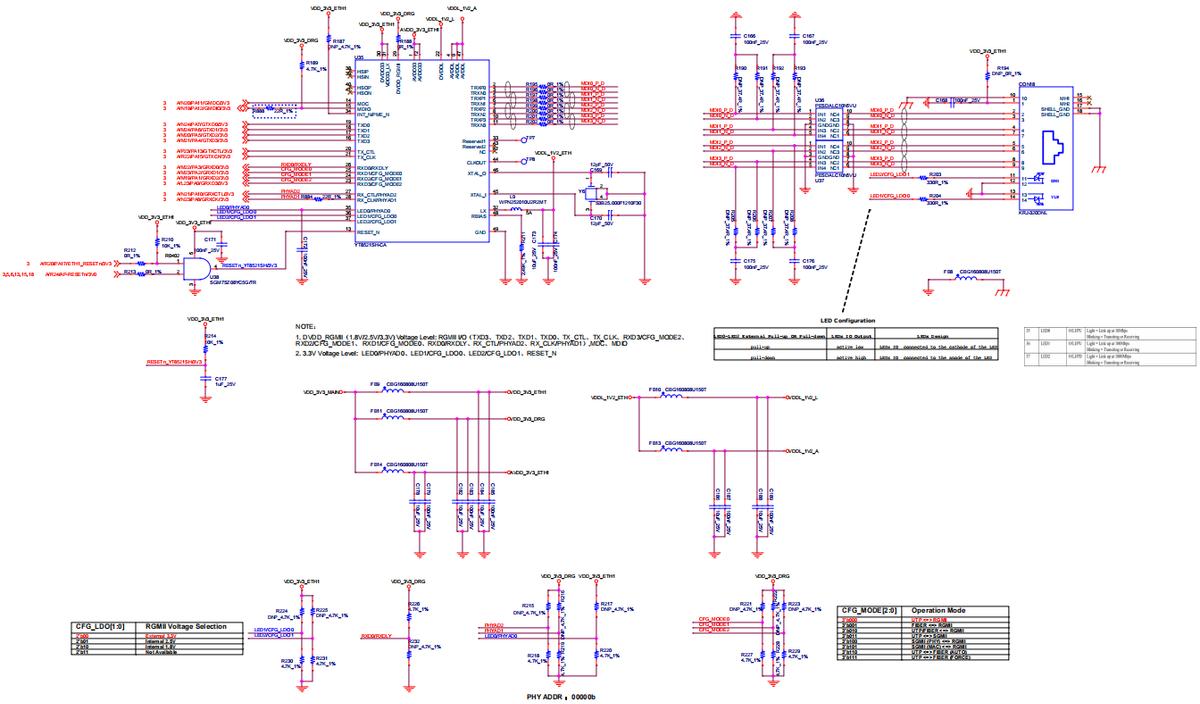

ETH0 RGMII千兆网口

CON18为ETH0 RGMII千兆网口,RJ45连接器已内置隔离变压器。

备注:A40i处理器内部集成1个GMAC控制器,支持1路RGMII千兆网口。

图 59

图 59 图 60

图 60设计注意事项:

- VDDL_1V2_ETH电源为YT8521SH-CA内部输出,请勿用于其它负载供电。

- XTAL_I、XTAL_O引脚接入25MHz无源晶振。如需使用25MHz有源晶振,可从XTAL_I引脚接入,XTAL_O引脚悬空处理。

- YT8521SH-CA芯片要求在供电稳定后,保持10ms后再拉高复位信号。请参考评估底板的复位电路方案,使用IO控制网口复位。

- YT8521SH-CA芯片管脚LED0/PHYAD0、LED1/CFG_LDO0、LED2/CFG_LDO1、RESET_N的信号电平皆为3.3V,上拉配置时,请上拉到3.3V;其他信号管脚上拉配置时,请上拉到DVDD_RGMII(1.8V/2.5V/3.3V)电源。

图 61

图 61ETH1 MII百兆网口

CON19为ETH1 MII百兆网口,采用RJ45连接器,已内置隔离变压器。

备注:A40i处理器内部集成1个EMAC控制器,支持1路MII百兆网口。

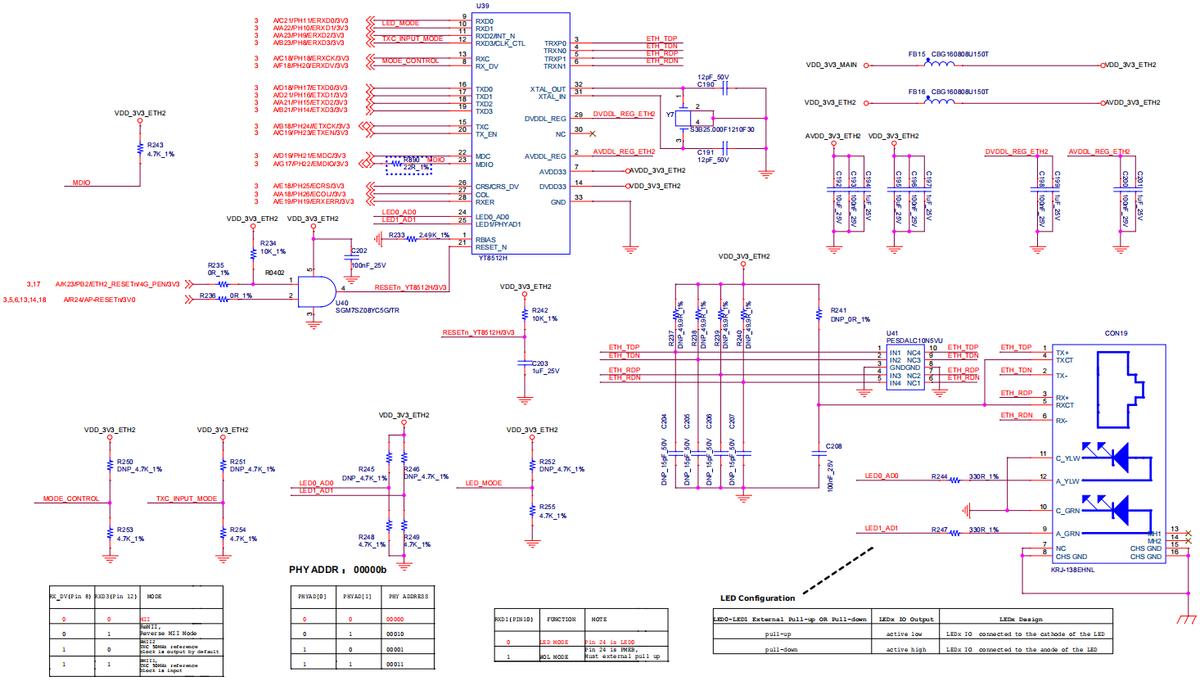

图 62

图 62 图 63

图 63设计注意事项:

- XTAL_IN、XTAL_OUT引脚接入25MHz无源晶振。如需使用25MHz有源晶振,可从XTAL_IN引脚接入,XTAL_OUT引脚悬空处理。

- YT8512H芯片要求在供电稳定后,保持10ms后再拉高复位信号。请参考评估底板的复位电路方案,使用IO控制网口复位。

ETH2 USB百兆网口

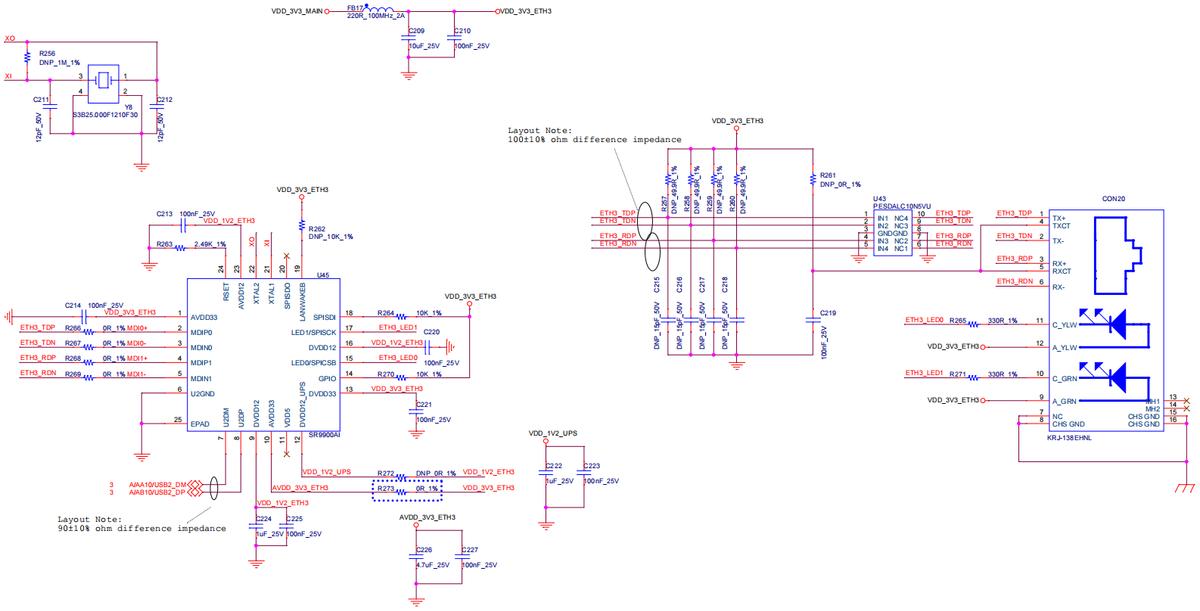

CON20为ETH2 USB百兆网口,采用RJ45连接器,已内置隔离变压器。

图 64

图 64 图 65

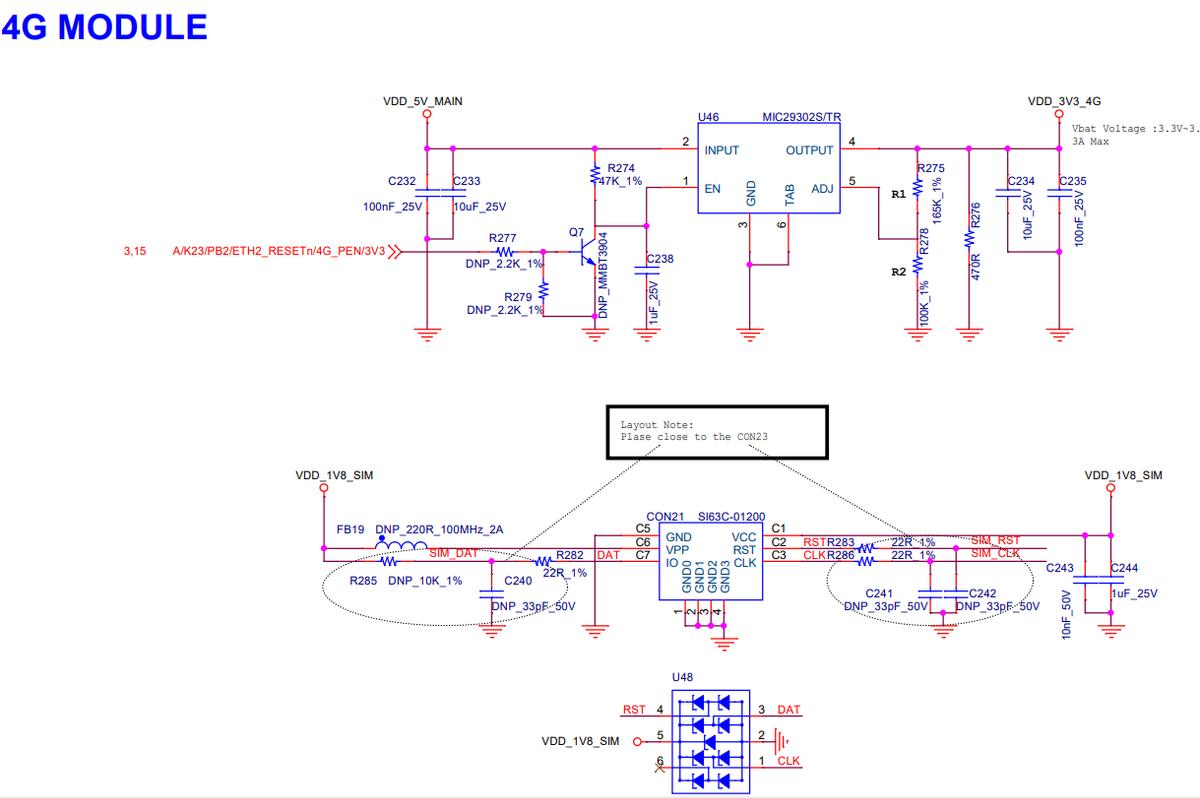

图 654G模块拓展接口

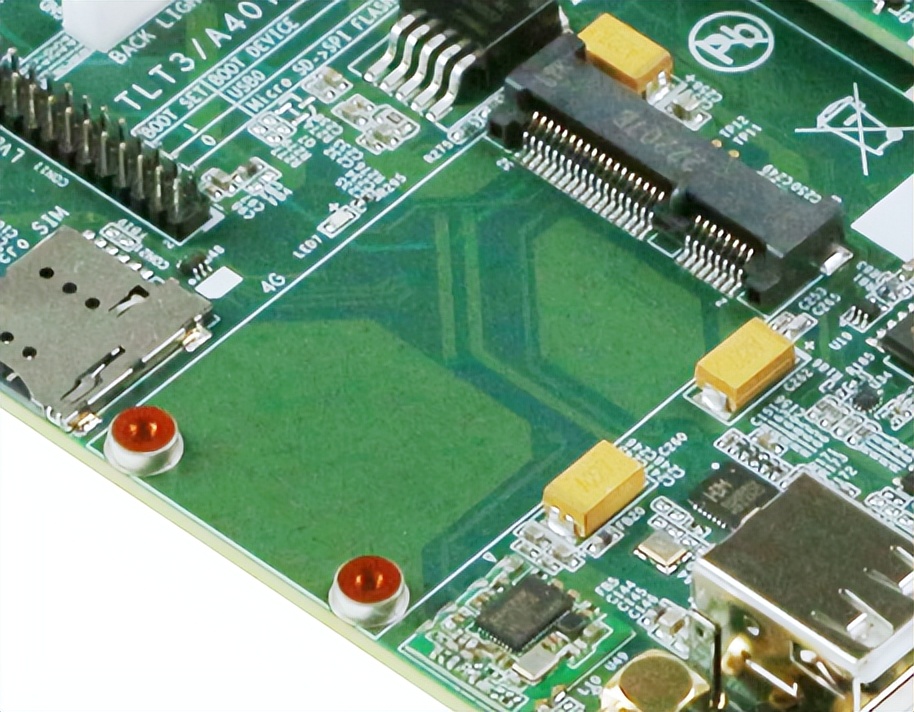

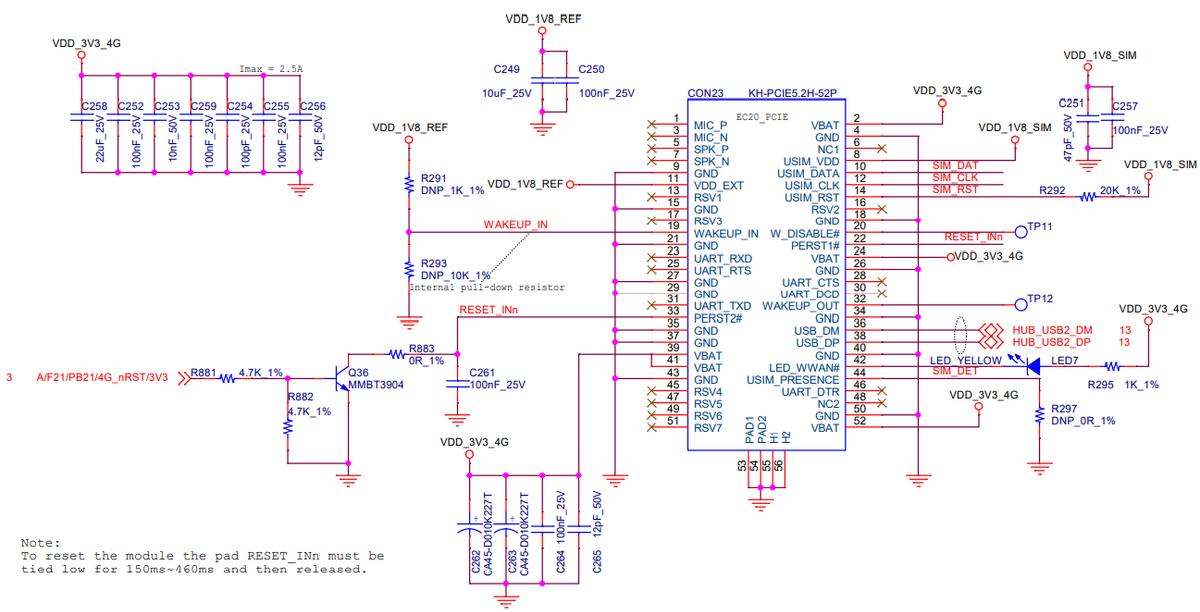

CON23为4G模块拓展接口,采用Mini PCIe插槽。评估底板通过USB HUB芯片将USB1总线拓展为4路USB HOST总线,其中引出一路进行4G模块拓展。

图 66

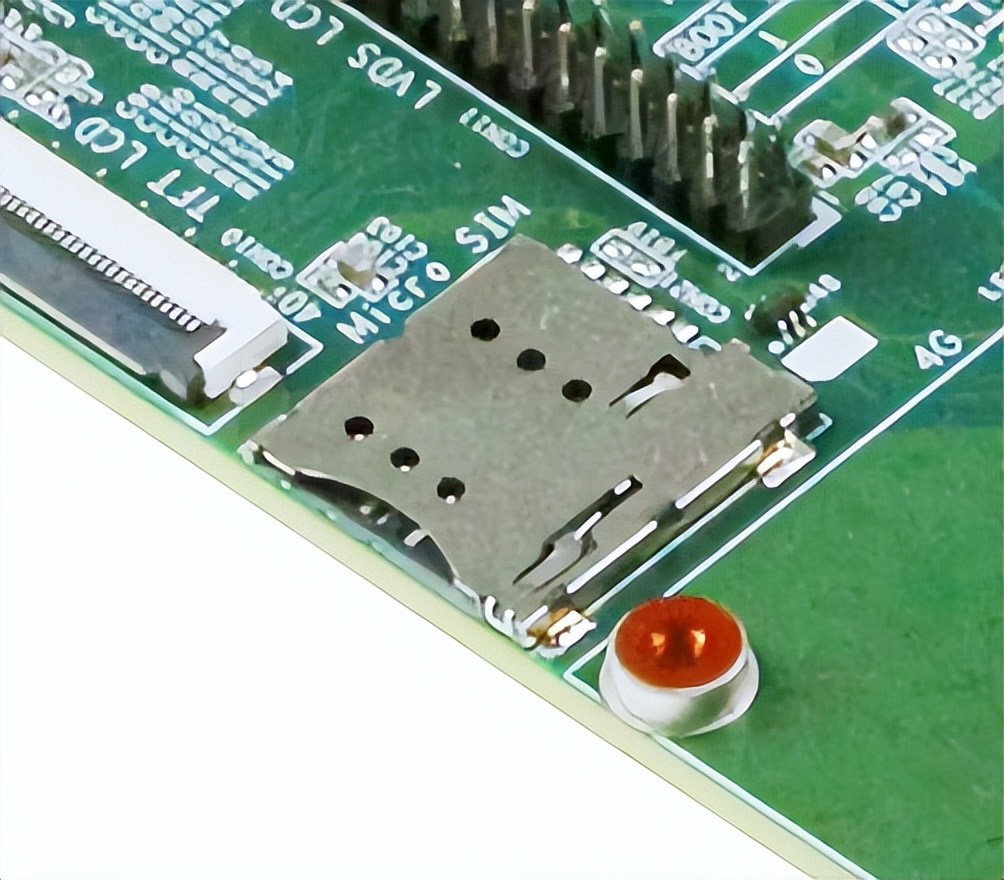

图 66CON21为Micro SIM卡座,采用插卡自弹形式,不带检测引脚。

图 67

图 67 图 68

图 68 图 69

图 69设计注意事项:

- 为保证4G模块有稳定的电源供应,其3.3V电源需由MIC29302S/TR(U46)独立供电,至少提供2A电流输出。如要替换其他电源,建议使用LDO,详细请参考4G模块数据手册要求。

- 如需控制4G模块供电,可贴上R277、R279电阻和Q7三极管,通过GPIO来控制4G模块电源使能状态。

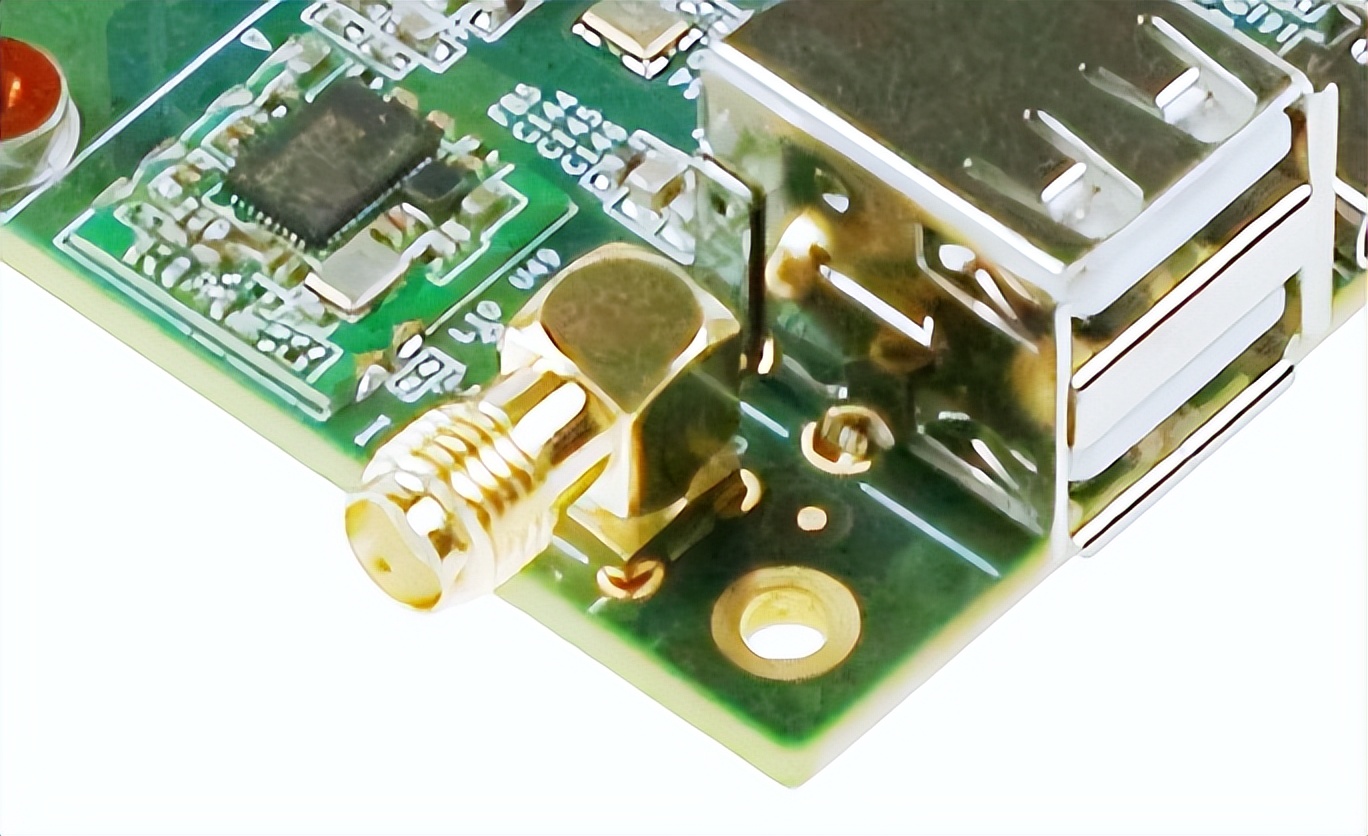

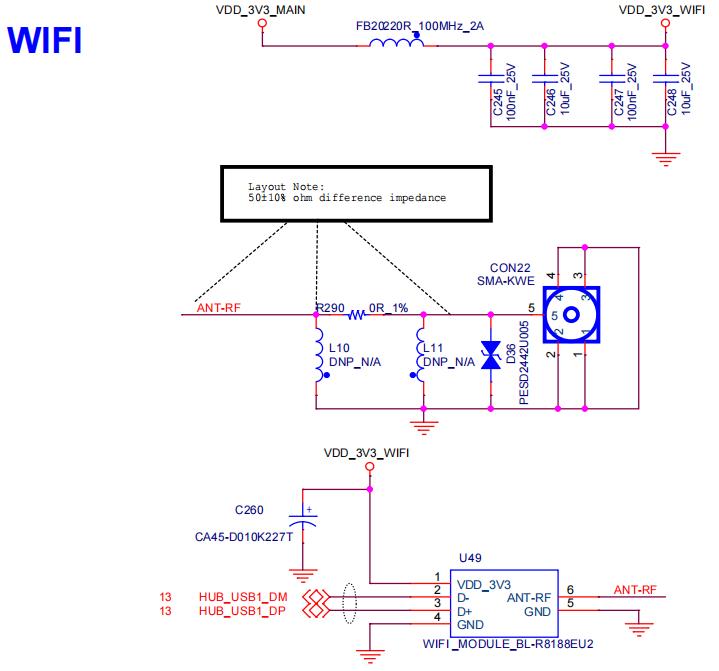

WIFI模块

评估底板通过USB HUB芯片将USB1总线拓展为4路USB HOST总线,其中引出一路进行WIFI模块拓展。板载WIFI模块(U49)型号为:必联BL-R8188EU2,采用邮票孔连接方式。

备注:WIFI模块芯片生产商为台系厂家。

CON22为SMA接口,用于外接WIFI模块的2.4G天线。

图 70

图 70 图 71

图 71蓝牙模块

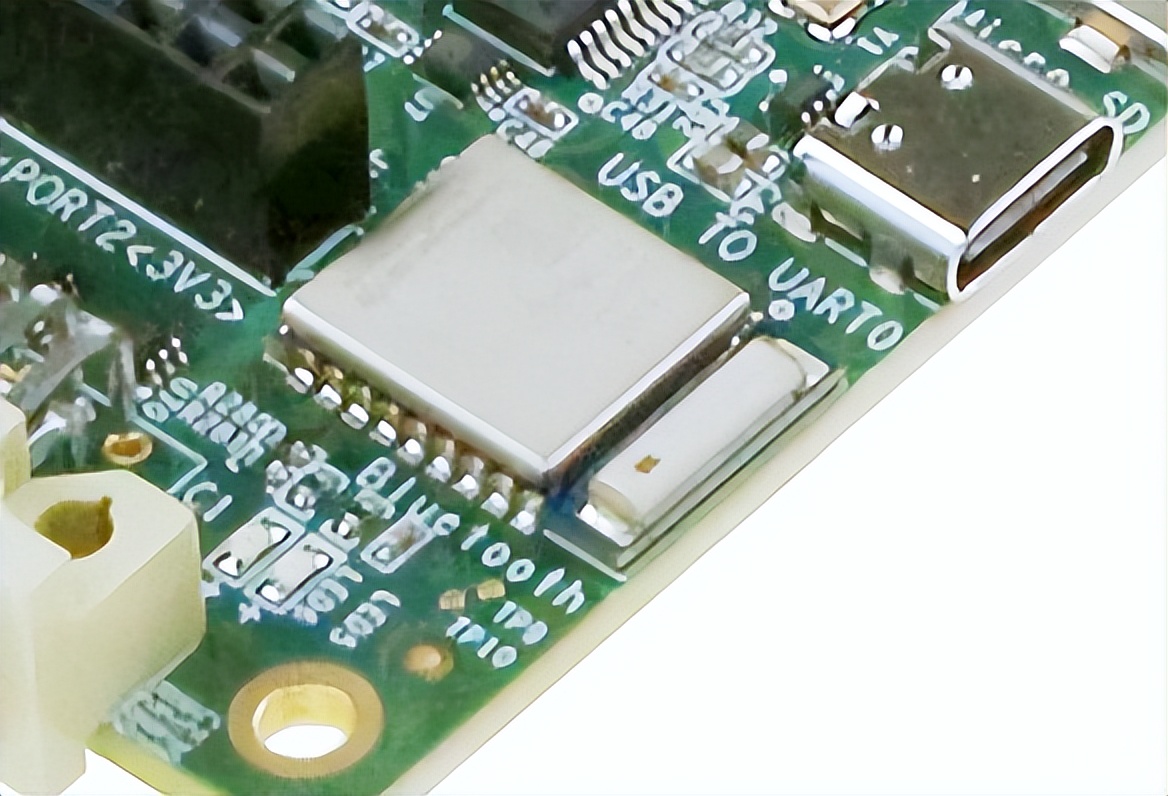

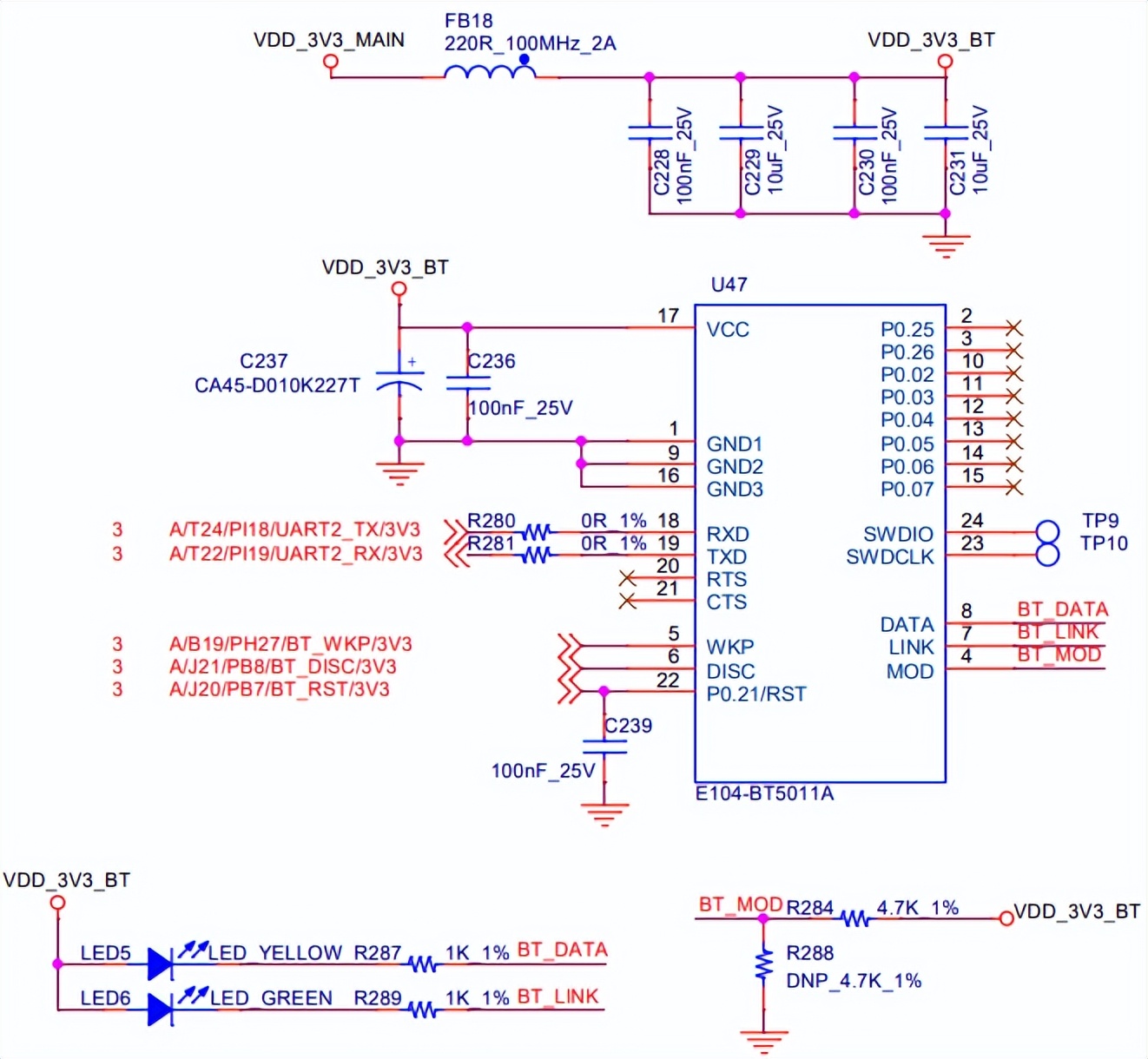

U47为板载蓝牙模块,通过UART2进行蓝牙模块拓展。型号为:亿佰特E104-BT5011A,采用邮票孔连接方式。模块自带PCB板载天线,无需外接天线。

备注:蓝牙模块芯片生产商为挪威厂家。

图 72

图 72 图 73

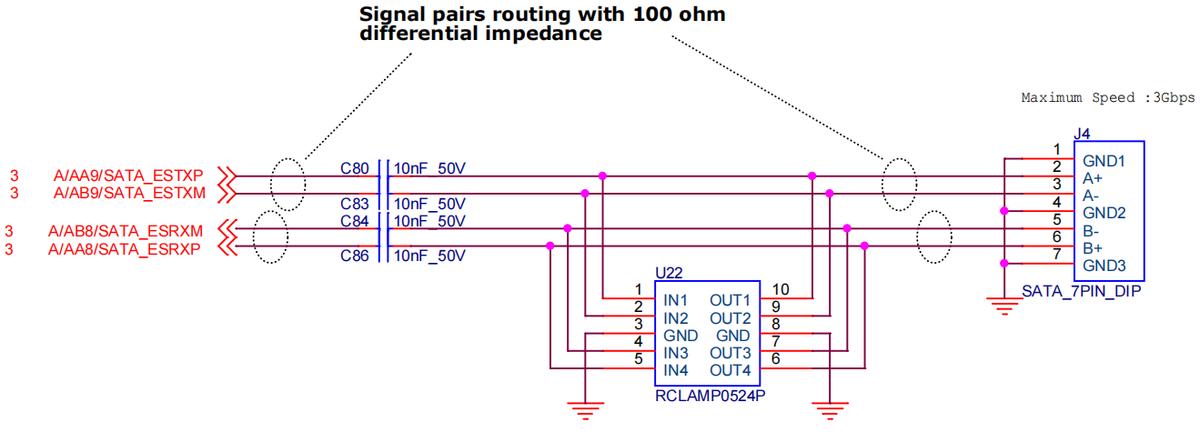

图 73SATA接口

J4为标准7pin SATA硬盘接口。

图 74

图 74 图 75

图 75设计注意事项:

- SATA_ESTXP/M和SATA_ESRXP/M线路需靠近J4放置10nF的AC耦合电容。

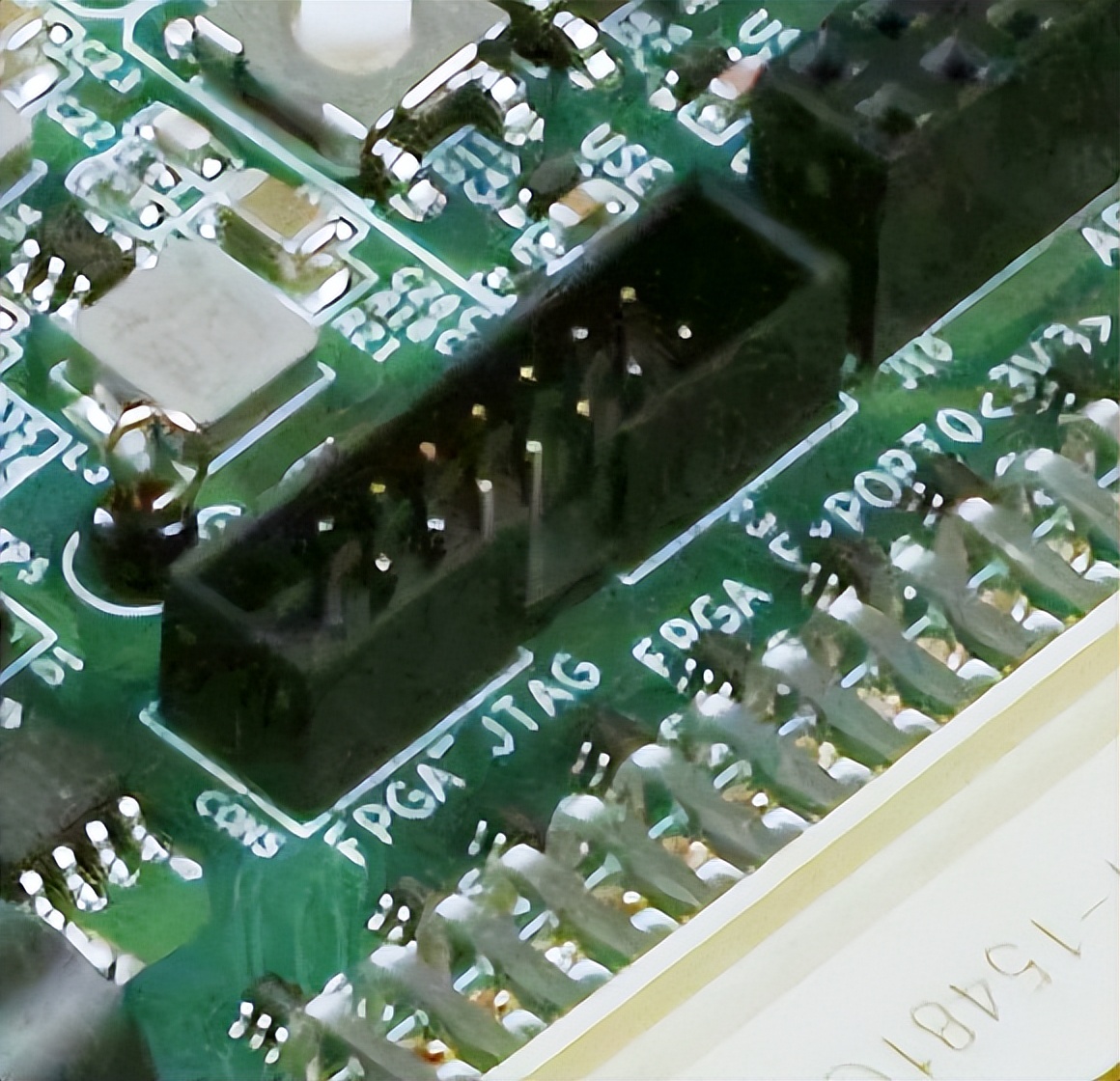

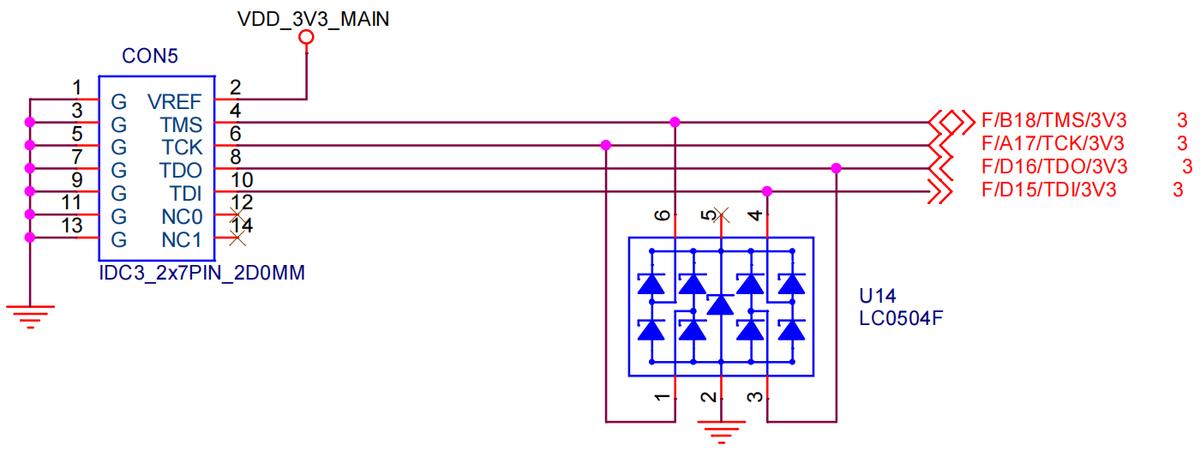

FPGA JTAG接口

CON5为FPGA JTAG仿真调试接口,采用14pin简易牛角座连接器,间距2.0mm,可适配创龙科技的TL-PGMCable下载器。

图 76

图 76 图 77

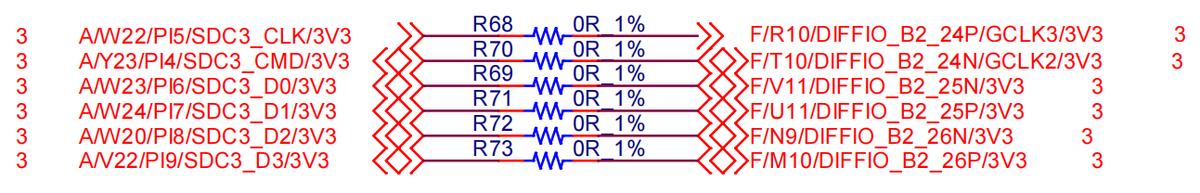

图 77SDIO接口

SDIO总线在核心板已用作ARM端与FPGA端的通信,在底板上不作为外设。

图 78

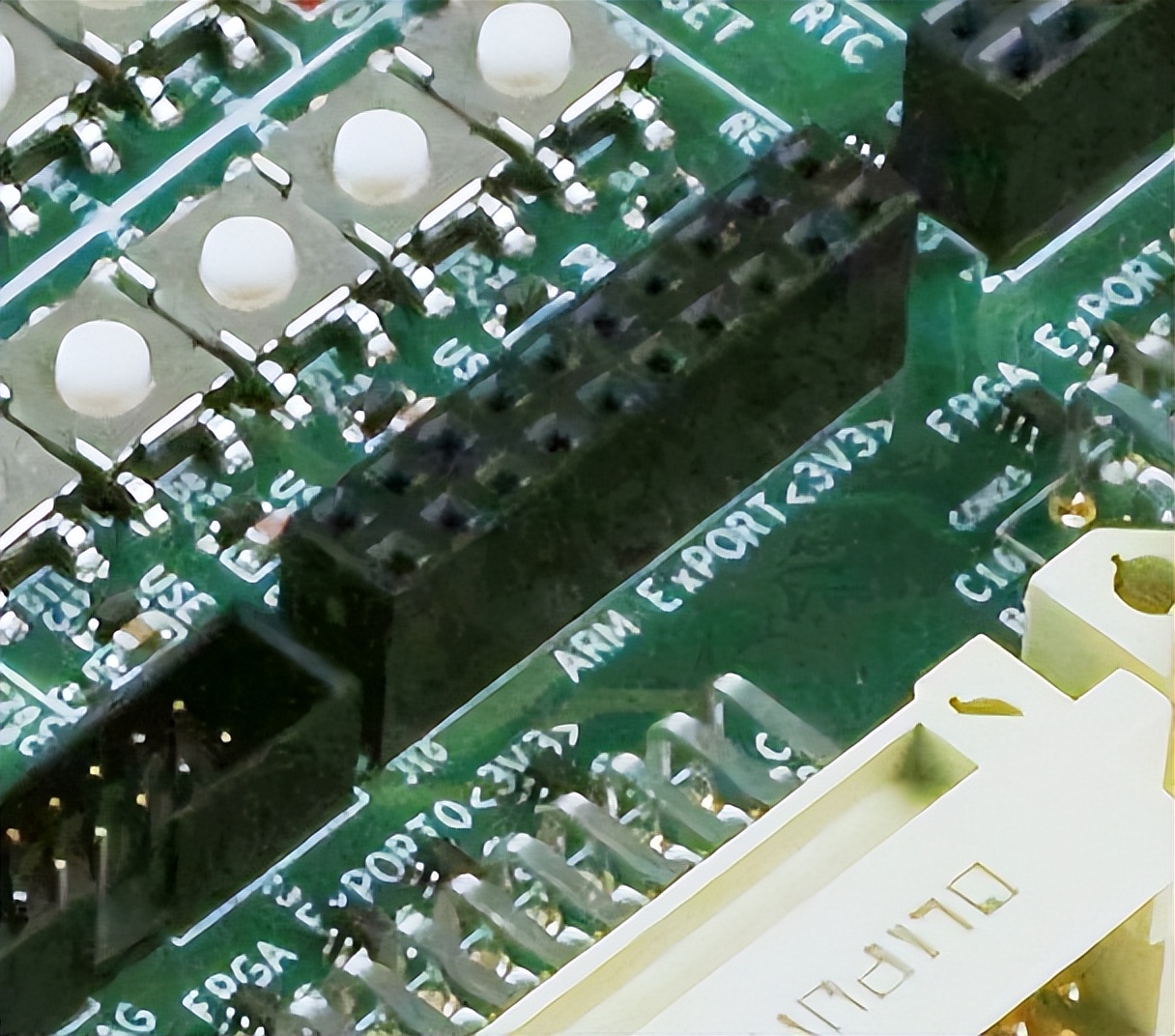

图 78ARM端拓展IO信号接口

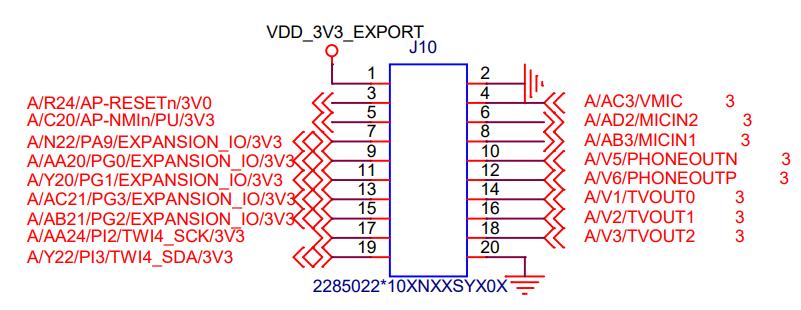

J10为ARM ExPORT0接口,采用2x 10pin排母,间距2.54mm,引出SYS_RESETn、AP-NMIn、Audio Codec、GPIO等拓展信号。

图 79

图 79 图 80

图 80FPGA端拓展IO信号接口

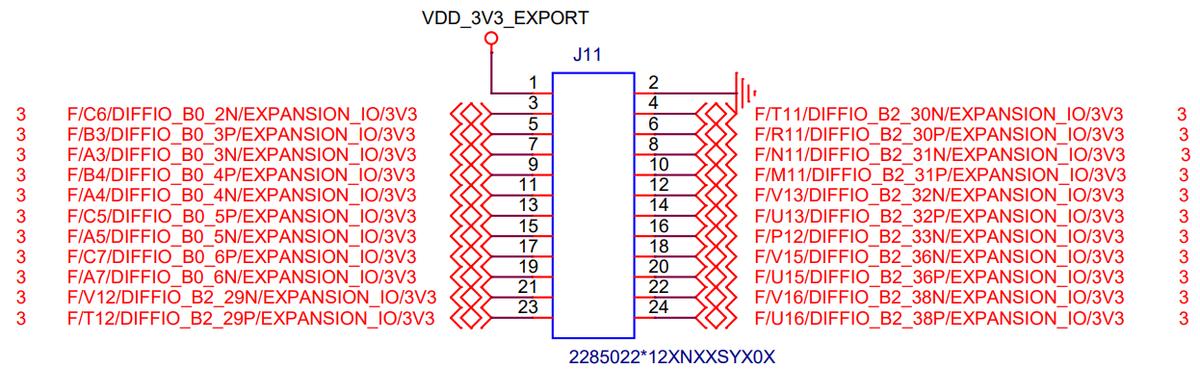

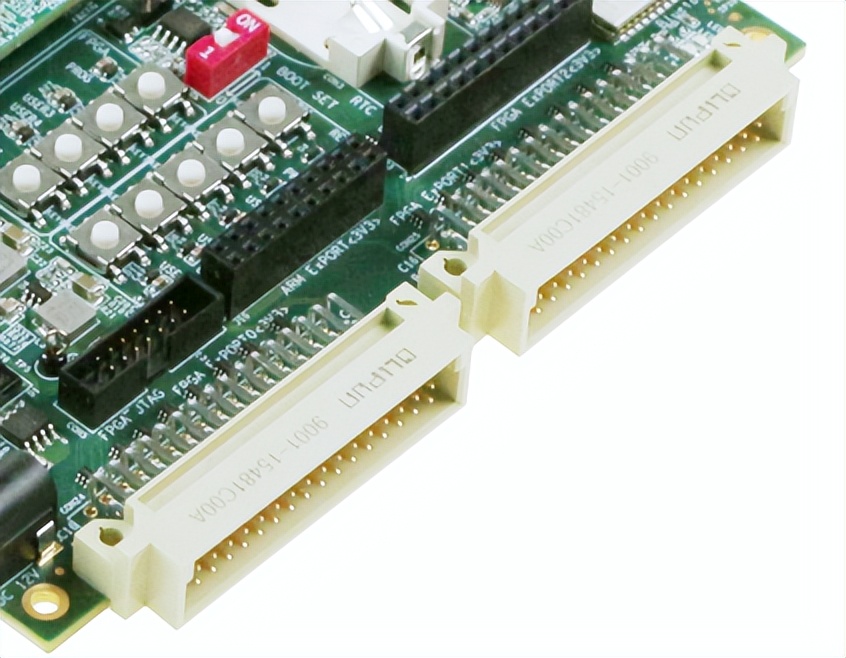

J11为FPGA ExPORT1接口,采用2x 12pin排母,间距2.54mm,引出FPGA端的IO拓展信号。

图 81

图 81 图 82

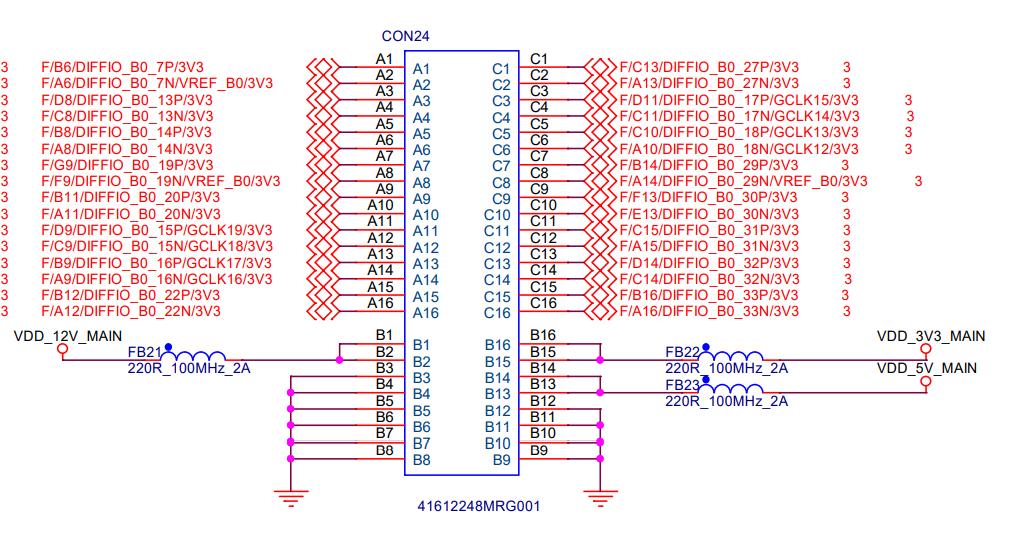

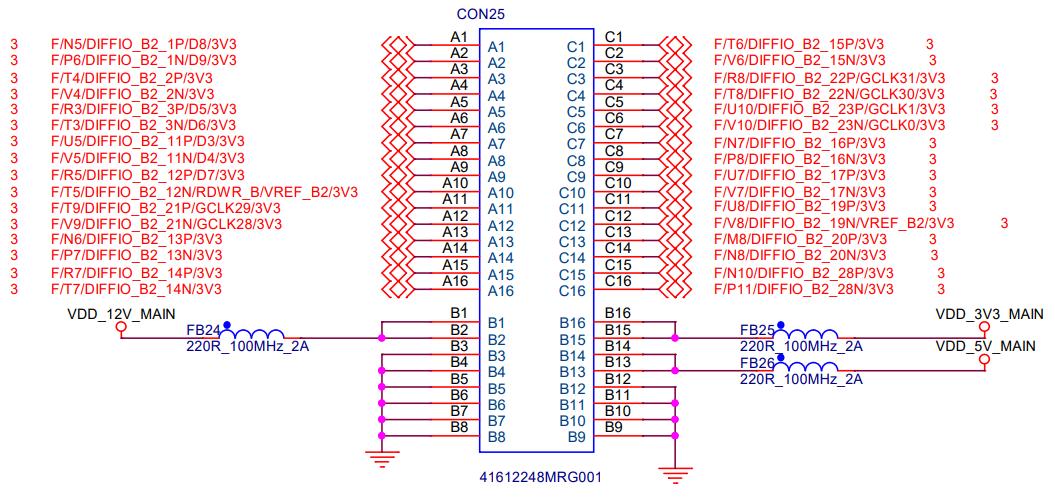

图 82CON24和CON25为3x 16pin欧式端子公座,间距2.54mm,引出FPGA端的IO拓展信号。

图 83

图 83 图 84

图 84 图 85

图 85全志A40i+Logos FPGA开发板(4核ARM Cortex-A7)硬件说明书(下)的更多相关文章

- 关于DE2-115 FPGA开发板无法烧写程序的解决方法

友晶科技推出的DE2-115 FPGA开发板,有时候莫名奇妙,无法烧写或者固化程序.利用JTAG 向DE2-115开发板烧写.sof文件失败,并提示以下错误,如图1和图2所示 图1 图2 解决方法:只 ...

- FPGA 开发板入手途径有哪些呢?

买到一块 FPGA 开发板,你如何入手呢? 根据博主的经验,你可以通过如下途径来学习: 1.如果你是淘宝上买的,那么可以在淘宝上搜索你的开发板(一般 FPGA 开发板生厂商在淘宝上卖都会附带教程,如米 ...

- 迅为三星Exynos 4412开发板四核Cortex-A9ARM安卓linux开发板

开发板光盘资料包含:原理图(PDF格式).底板PCB(Allegro格式).驱动程序源码.芯片和LCD数据手册.开发环境.产品使用手册. 4412开发板简介: iTOP-Exynos4412开发板采用 ...

- FPGA开发板

kingst.cnblogs.com 各种应用需要的接口不同: 做数字信号处理的,需要有AD/DA, 做图像处理,需要有图像接口.如果是通信的,需要有通信的接口,例如PCI/LVDS等.... 然后根 ...

- 至芯FPGA培训中心-1天FPGA设计集训(赠送FPGA开发板)

至芯FPGA培训中心-1天FPGA设计集训(赠送开发板) 开课时间2014年5月3日 课程介绍 FPGA设计初级培训班是针对于FPGA设计技术初学者的课程.课程不仅是对FPGA结构资源和设计流程的描述 ...

- SoC FPGA开发板的FPGA配置数据下载和固化

小梅哥编写,未经许可,严禁用于任何商业用途 2018年7月2日星期一 soc fpga的烧写和固化方式与传统的纯fpga固化方式即存在形式上的相同,也存在细节上的差异,特整理此文. AC501-So ...

- 使用FPGA开发板驱动VGA显示器

1. 本次使用的是cyclone4开发板,先看下原理图,因为右边的RGB应该是模拟信号量,但是本次例程只接了3根线,那就是说颜色只有8种. 2. 代码,输出信号有R,G,B三色,就是上图右边的,行同步 ...

- JZ2440开发板:修改ARM芯片时钟(学习笔记)

想要修改ARM芯片的时钟,需要去查询芯片手册和原理图,获取相关的信息(见下方图片) 首先来看时钟的结构图 根据结构图可以看出,时钟源有两种选择:1. XTIpll和XTOpll所连接的晶振 2. EX ...

- 【STM32-V7】STM32H743XIH6开发板,丰富软件资源,强劲硬件配置,大量软件解决方案持续更新中(2019-12-12)

说明: 争取做更多的实战性应用,分享更多的嵌入式技术,希望能在实际项目中帮到大家. (1)V7将大力加强对初学者的支持力度,已经更新至63章,下载链接,后37章和一批视频教程将加紧制作. (2)事隔五 ...

- 【ARM-Linux开发】ARM7 ARM9 ARM Cortex M3 M4 有什么区别

ARM7 ARM9 ARM Cortex M3 M4 区别 arm7 arm9 可以类比386和奔腾, 不同代,arm9相比arm7指令集和性能都有所增强,arm7和arm9都有带mmu和无mmu的版 ...

随机推荐

- 01.windows 环境设置

windows下可以安装Git工具, 使用git bash操作 Windows 10 环境下,通过-/.bash_profile 设置 git bash 别名: 打开 git bash,需切换到当前用 ...

- SpringBoot-RSA加密

前言 最近由于工作业务的需要,需要对指定的字段信息进行非对称加解密:由于需要加密的内容过于庞大:自己执行程序会出现:Data must not be longer than 117 bytes 的异常 ...

- uniapp中利用renderjs引入leaflet

由于uniapp中要使用地图,虽然uni-app有地图组件map,但是很难用,而且性能很差.在app中是不能操作dom,所以直接用leaflet是不可能的.最终发现了renderjs,官网提出,在ap ...

- 小程序 image 高度自适应及裁剪问题

在做微信小程序的商品详情页,商品的详情是图片集合,渲染完成后发现图片加载的很不自然,后来我把样式设置宽度 100%,并对 image 组件添加属性 mode="widthFix"解 ...

- angular响应式表单笔记

angular 在开发过程中对于表单的验证 import {ReactiveFormsModule, FormsModule, FormControl, FormGroup, Validators} ...

- 【活动访谈】发力数字基座 推动物联创新—航天科技控股集团AIRIOT4.0平台发布会活动专访

近日,由航天科技控股集团股份有限公司主办的"数字基座 智慧物联-AIRIOT4.0平台发布会"在北京圆满落幕.航天三院科技委总工程师王连宝应邀出席本次会议并接受媒体采访,共同参与访 ...

- echarts下划线实现

echarts中无下划线实现,我采用图片填充文本块背景的方式实现 这是从 长空雁叫霜晨月 的博客中得到启发https://www.cnblogs.com/volodya/p/Echarts.html ...

- iOS符号表手工还原

1.通过Xcode的Device工具导出app.crash文件 2.将.crash 和 .dSYM符号 app放在同一个目录中 3.寻找symbolicatecrash,将symbolicatecra ...

- itest work(爱测试) 开源一站式接口测试&敏捷测试工作站 9.0.5. Rc4

(一)itest work 简介 itest work (爱测试) 一站式工作站让测试变得简单.敏捷,"好用.好看,好敏捷" ,是itest wrok 追求的目标.itest w ...

- windows报错

如果说你dns没有权威的话1.先去long.com上面右键属性把"区域传送给所有服务器打勾"2.右键属性,在名称分析器中,输入要添加为辅助dns的服务器的ip显示解析成功就可以了