Altera三速以太网IP核使用(下篇)--- 百兆网接口设计与使用

MAC IP核的主要作用是:实现数据链路层协议,分为TX方向与RX方向,TX方向实现的是在原包文的前面加上7个55和1个D5,RX方向则相反。在使用这个 MAC IP核之前,首先确认下自己使用的网卡是支持千兆网卡还是百兆网卡,我自己的电脑是百兆网卡,百兆网卡只支持百兆速率的传输,要按照百兆网卡进行管脚配置。

管脚配置

根据数据手册P54、P55进行硬件管脚引出:

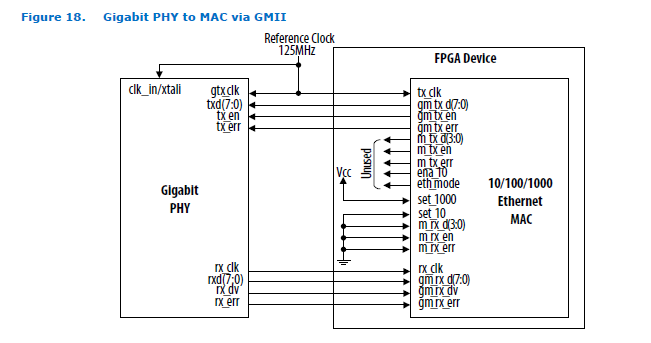

千兆网连接模式

千兆网的PHY芯片数据接收与发送管脚txd与rxd均是8bit,需要用pll倍频125M给PHY芯片的gtx_clk以及MAC IP核的tx_clk,PHY芯片会根据发送速率产生一个随路时钟给MAC IP核的rx_clk。

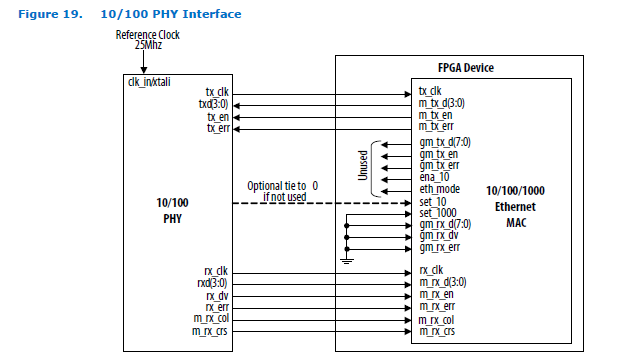

百兆网连接模式

百兆网的PHY芯片数据接收与发送管脚txd与rxd均是4bit,并且只需要给一个Reference Clock 至PHY芯片,PHY芯片就会产生25M的tx_clk与rx_clk至MAC IP核,这里注意要把m_rx_col 与m_rx_crs芯片管脚也引出来作为MAC IP核的m_rx_col 与m_rx_crs输入,要注意的是千兆网PHY芯片的使用是不需要这两个管脚的。

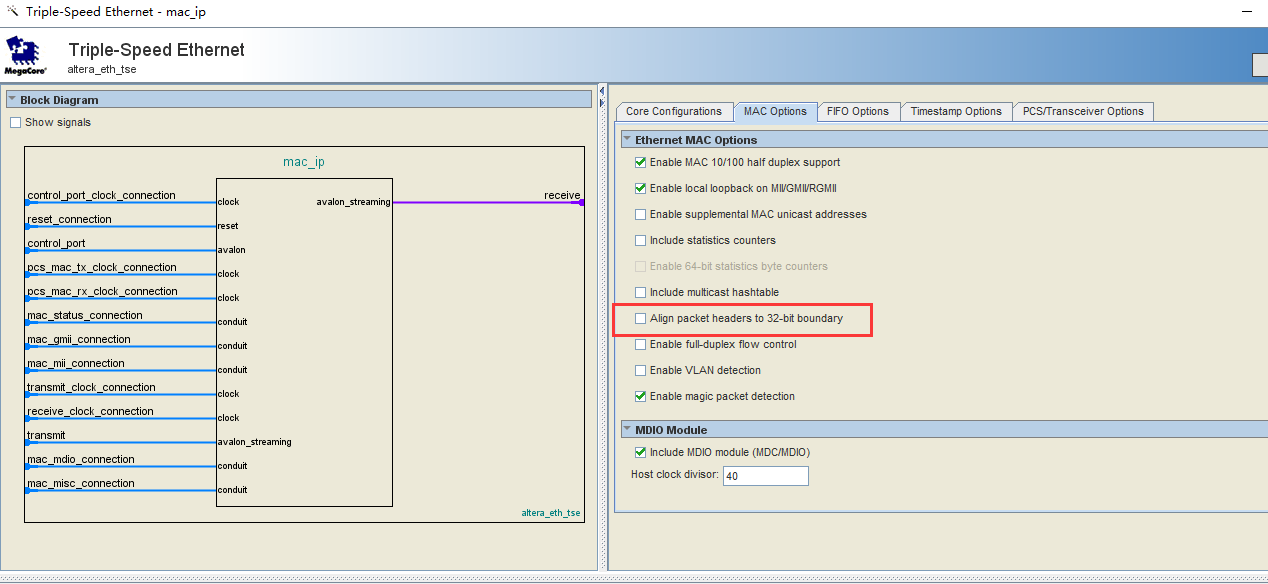

MAC IP核生成注意事项

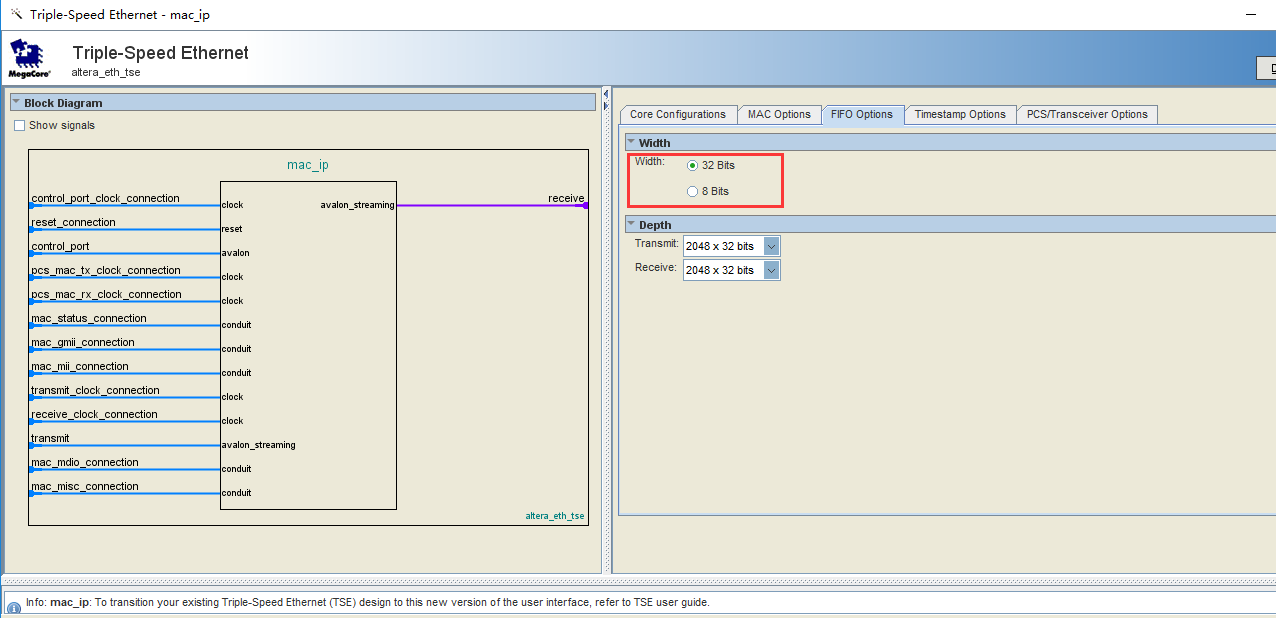

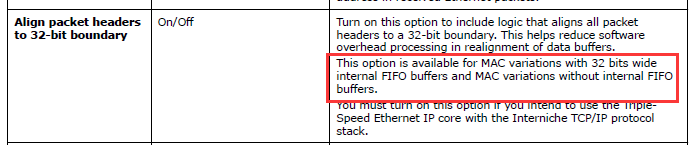

如果选择的是生成32bit数据位宽的内部 FIFO,那么“Align packet headers to 32-bit boundary"就是一个可选择项,具体见数据手册:

特别要注意的是:

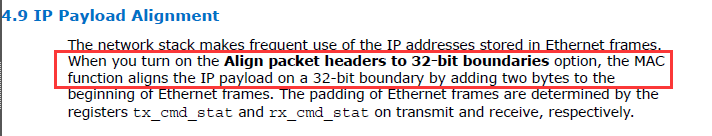

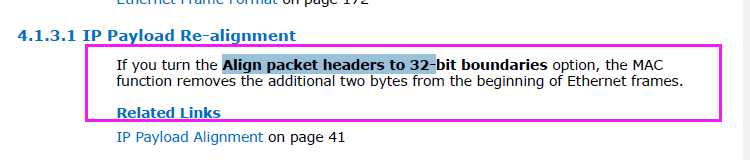

“Align packet headers to 32-bit boundary"这个选项的作用就是为了对齐数据,自动往TX方向/RX方向减少或者增加两个字节。因为按照TX方向发送包文格式:

目的地址(6字节)+源地址(6字节)+类型(2字节)+数据

目的地址(6字节)+源地址(6字节)+类型(2字节)=14(字节),MAC 内部FIFO是32bit,也就是一次发送4byte,14字节不是4的倍数,因此,“Align packet headers to 32-bit boundary"这个选项是为了对齐数据,避免一个时钟周期内地址与数据混合发送,如果不勾选此选项,FPGA与PC端通讯的数据字节数会保持一致。

传输速率要求

1、对于千兆网,只要保证用户侧速率>1G即可;

2、对于百兆网,只要保证用户侧速率>100M即可;

我这里选用32bit的内部FIFO,用PLL分频出10M时钟给MAC IP核的ff_tx_clk 、ff_rx_clk以及clk,这样用户侧速率就是32bit X 10M > 100M,符合速率传输要求。

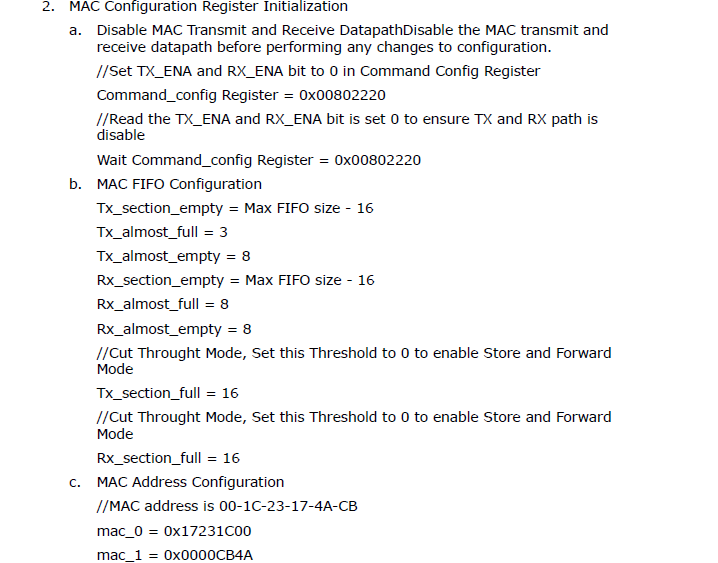

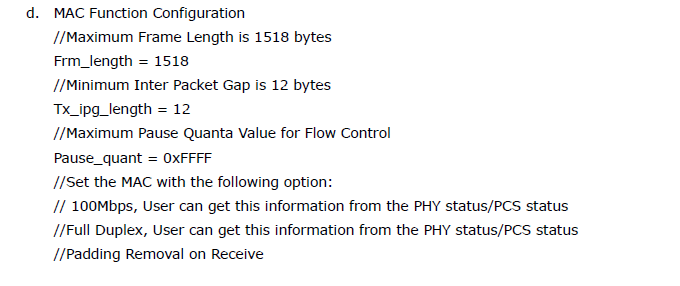

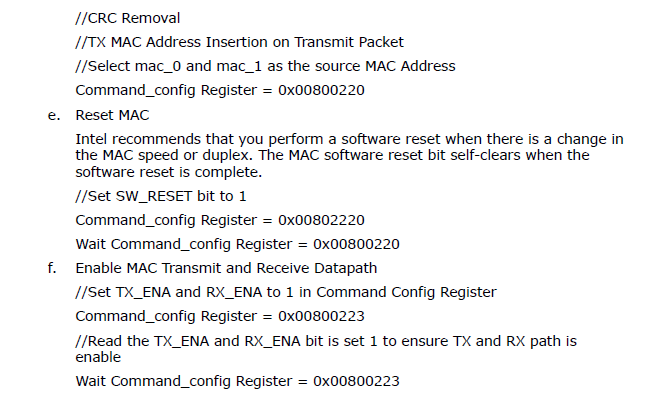

MAC IP核的初始化配置

关于MAC IP核的初始化配置非常重要,如果实在看不懂Command_config Register的配置,请严格按照数据手册P97-P98配置即可

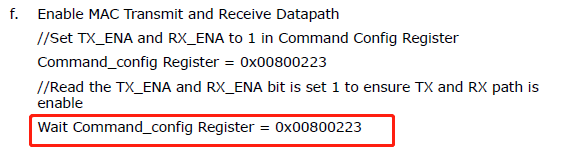

唯一要注意的是最后要保证TX与RX的使能端口已经开启,因此最后要读下16‘h02这个地址,以确保Command_config Register 已经等于0x00800223。

我的初始化配置表如下所示:

parameter REG_NUM = ; always @(*)begin

case(reg_cnt)

:add_wdata = {'b110,8'h02,'h00802220};//common

:add_wdata = {'b110,8'h09,'d2032 };//tx_section_emty

:add_wdata = {'b110,8'h0e,'d4 };//tx_almost_full

:add_wdata = {'b110,8'h0d,'d08 };//tx_almost_empty

:add_wdata = {'b110,8'h07,'d2032 };//rx_section_empty

:add_wdata = {'b110,8'h0c,'d08 };//rx_almost_full

:add_wdata = {'b110,8'h0b,'d08 };//rx_almost_emty

:add_wdata = {'b110,8'h0a,'d16 };//tx_section_full

:add_wdata = {'b110,8'h08,'d16 };//rx_section_full

:add_wdata = {'b110,8'h03,'h01020304};//MAC0

:add_wdata = {'b110,8'h04,'h00000605};//MAC1

:add_wdata = {'b110,8'h05,'d1518 };//MAX FRAME LENGTH

:add_wdata = {'b110,8'h17,'d12 };//TX IPG LEGNTH

:add_wdata = {'b110,8'h06,'h0000ffff};//pause_quant :add_wdata = {'b110,8'h02,'h00800220};//.. :add_wdata = {'b110,8'h02,'h00802220};//common,rst,set SW_RESET bit to 1

:add_wdata = {'b001,8'h00,'h00010_0000};//wait

:add_wdata = {'b010,8'h02,'h00800220 };//wait

:add_wdata = {'b110,8'h02,'h00800223};//common,enable tx and rx // default:add_wdata = ;

endcase

end

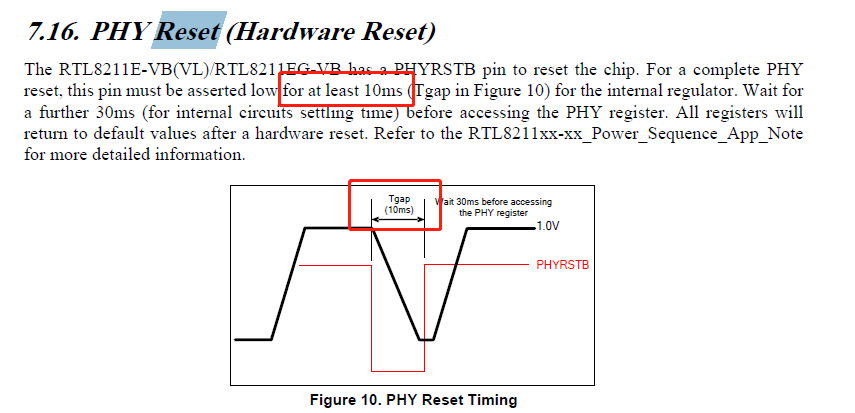

PHY芯片的复位时间

由数据手册可以看到,PHY芯片的上电复位时间至少要维持10ms,以50M输入时钟为例,我的设计如下:

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_phy_reset <= ;

end

else if(add_cnt_phy_reset)begin

if(end_cnt_phy_reset)

cnt_phy_reset <= ;

else

cnt_phy_reset <=cnt_phy_reset + ;

end

end assign add_cnt_phy_reset = flag== ;

assign end_cnt_phy_reset = add_cnt_phy_reset && cnt_phy_reset== 10_00_000 ; //拉低10ms always @(posedge clk or negedge rst_n)begin

if(rst_n=='b0)begin

flag <= ;

end

else if(end_cnt_phy_reset)begin

flag <= ;

end

end always @(posedge clk or negedge rst_n)begin //phy_reset

if(rst_n=='b0)begin

phy_reset <= ;

end

else if(flag==&&add_cnt_phy_reset && cnt_phy_reset == 500_000)begin

phy_reset <= ;

end

else if(end_cnt_phy_reset)begin

phy_reset <= ;

end

end

测试验证

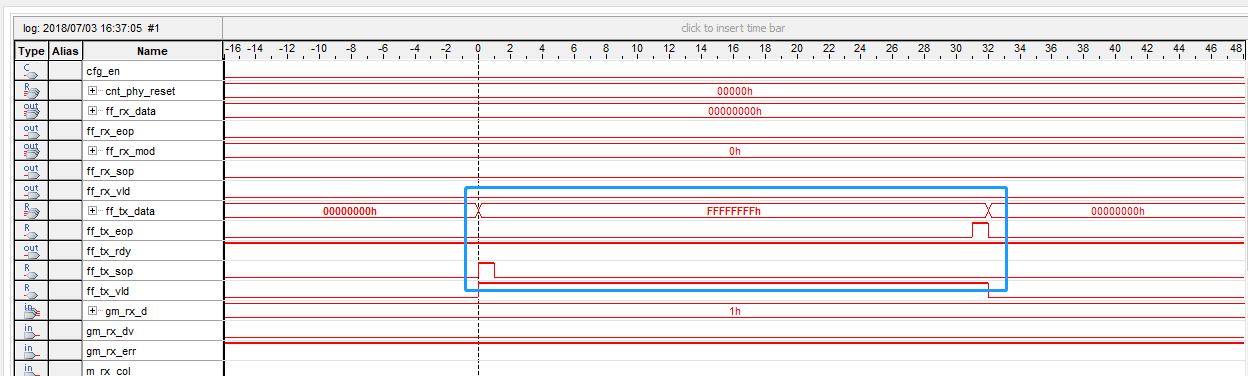

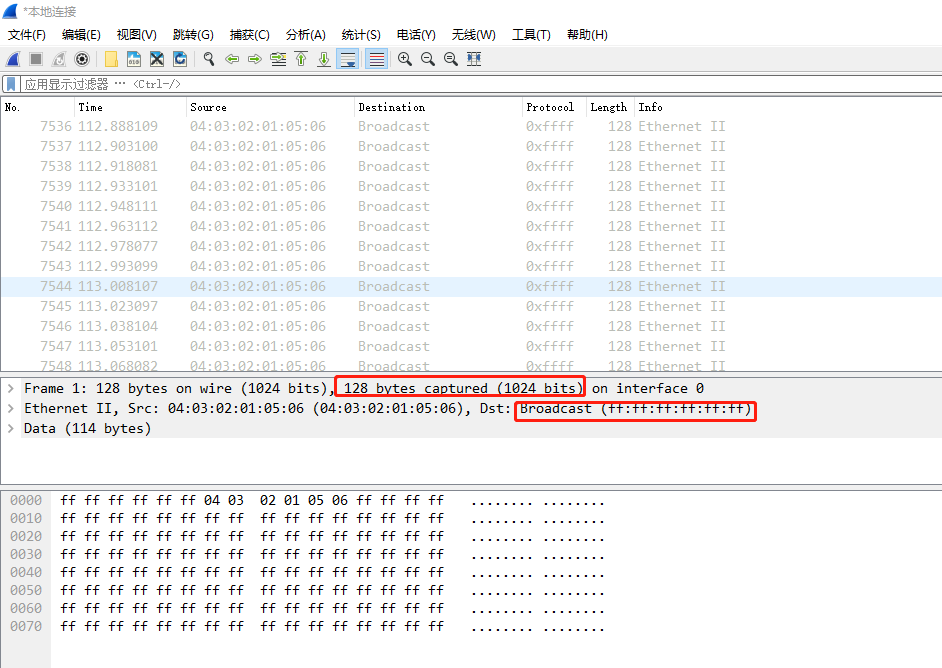

TX 方向: 初始化完成后,自动产生MAC 层包文,经过MAC IP 进行数据链路层处理后,将包文发 给PHY 芯片RTL8211,PHY 芯片经过PHY 层处理后再传给PC,PC 使用wireshark 软件采集包文观察。

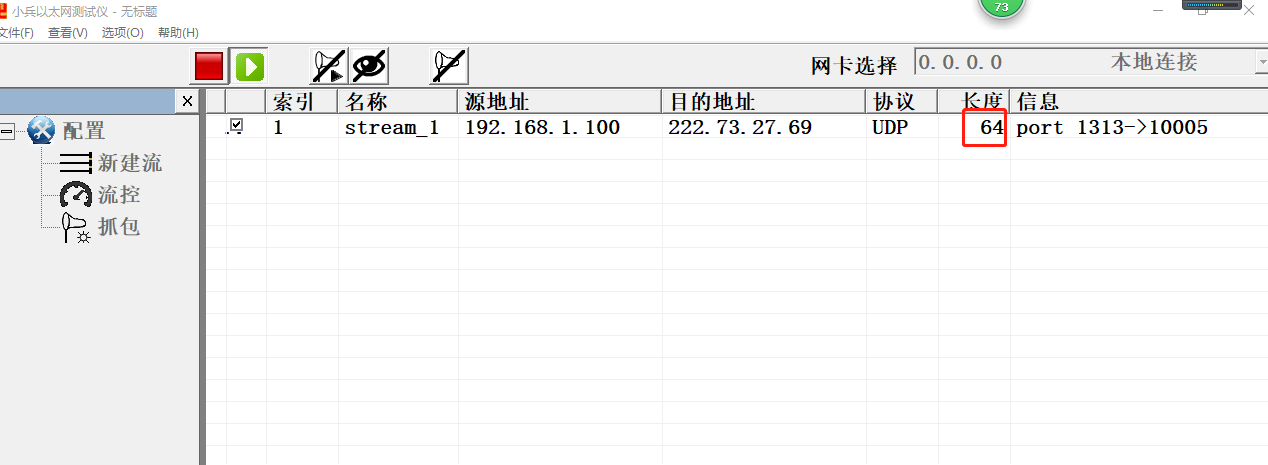

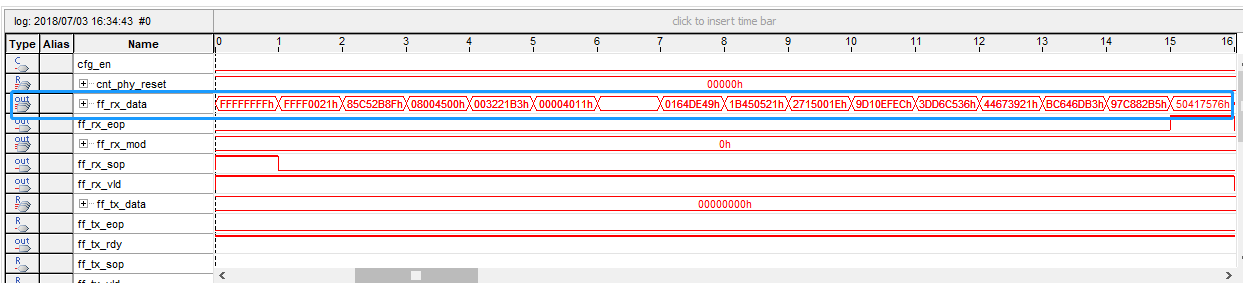

RX 方向: PC 发广播包文给PHY 芯片,PHY 芯片经过PHY 层处理后送给FPGA,FPGA 接到后经过数据链路层处理后,用SIGNALTAP 观测最后的信号。

用到的辅助测试软件:

1、小兵发包:往FPGA 发数据

2、wireshark:捕获发送与接收包文

TX方向,FPGA往PC发128字节长度的广播包

PC端收到完好的128个字节的广播包

(2)RX方向

小兵发64字节的广播包

FPGA收到完好的64个字节的广播包

至此,有关该MAC IP核百兆网的设计与使用完毕,有关MAC IP核千兆网的使用与它类似,只需要注意PHY芯片的gtx_clk时钟由PLL倍频得到125M作为输入以及接收/发送数据端口均为8bit即可。

注意:未经允许,禁止转载,违法必究!

Altera三速以太网IP核使用(下篇)--- 百兆网接口设计与使用的更多相关文章

- Altera三速以太网IP核快速仿真与使用(上篇)

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的 ...

- 用Modelsim SE 直接仿真 Altera(Intel PSG) IP核 需要注意的问题

如果我们直接用Modelsim SE仿真 Altera IP核,首先会进入Quartus II目录下找到IP核对应的仿真库源文件,然后在Modelsim SE中进行编译,添加到Modelsim SE的 ...

- 浅析Xilinx 三速以太网MAC IP核

之前在使用Altera的三速以太网MAC IP的基础上,完成了UDP协议数据传输.此次为了将设计移植到xilinx FPGA上,需要用到xilinx的三速以太网MAC IP核,当然也可以自己用HDL编 ...

- EMAC IP 核

在有线连接的世界里,以太网(Ethernet)无所不在.以太网具有各种速度模式.接口方式.以及灵活的配置方式.现在的以太网卡都是10/100/1000Mbps自适应网卡.以太网的物理层(PHY)通常使 ...

- 从Xilinx FFT IP核到OFDM

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109.关于 ...

- dubbo调用外网接口 注册外网ip到zookeeper 暴露外网ip

dubbo注册时会通过主机名寻找ip,会将内网ip注册到zookeeper 如果我们调用外网服务器server的话是找不到的 会报如下错误 [DUBBO] client reconnect to 12 ...

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

随机推荐

- 通过Windows Server 2008 R2建立iSCSI存储

名词解释:iSCSI技术是一种由IBM公司研究开发的,是一个供硬件设备使用的可以在IP协议的上层运行的SCSI指令集,这种指令集合可以实现在IP网络上运行 SCSI协议,使其能够在诸如高速千兆以太网上 ...

- Linux Samba配置文件常用参数详解

目录 1.全局参数 2.共享参数 Samba的主配置文件叫smb.conf,默认在/etc/samba/目录下. smb.conf含有多个段,每个段由段名开始,直到下个段名.每个段名放在方括号中间 ...

- C++类知识总结

c++类 1.初始化const或引用类型数据成员的唯一机会是在构造函数初始化列表中. 2.使用成员初始化列表时成员初始化的次序:第一个成员首先被初始化.然后是第二个,依次类推. 构造函数初始化列表为类 ...

- 深入浅出SharePoint2013——常用术语

CAS(Code Access Security)自定义代码访问安全性 Sandboxed solution 沙箱解决方案

- HTTP协议图--HTTP 协议报文结构

1.HTTP 报文 用于 HTTP 协议交互的信息被称为 HTTP 报文.请求端(客户端)的 HTTP 报文叫做请求报文:响应端(服务器端)的叫做响应报文.HTTP 报文本身是由多行(用 CR[car ...

- 认识 Java(配置环境变量)

1. Java 简介 Java由Sun Microsystems公司于1995年5月推出,是一种面向对象的编程语言.在2009年4月20号,ORACLE (甲骨文)收购了 Sun 公司,也就是说 Ja ...

- python选课系统

程序名称: 选课系统 角色:学校.学员.课程.讲师 要求: 1. 创建北京.上海 2 所学校 2. 创建linux , python , go 3个课程 , linux\py 在北京开, go 在上海 ...

- Java类修饰符的使用与作用以及常见问题

首先明确,类是放在文件里的,在文件里面的不同位置就有不同的作用,就是不同类型的类. 1, 顶级类or外部类:包括两种,一个文件中与文件名同名称的类我们称作顶级类(也是外部类),如果在一个文件中的一个类 ...

- weblogic之CVE-2016-3510反序列化分析

将反序列化的对象封装进了weblogic.corba.utils.MarshalledObject,然后再对MarshalledObject进行序列化,生成payload字节码.由于Marshalle ...

- ubuntu16.04 Detectron目标检测库配置(包含GPU驱动,Cuda,Caffee2等配置梳理)

Detectron概述 Detectron是Facebook FAIR开源了的一个目标检测(Object Detection)平台. 用一幅图简单说明下Object Detection.如Mask R ...