NAND Flash【转】

转自:http://www.cnblogs.com/lifan3a/articles/4958224.html

以Micron公司的MT29F2G08为例介绍NAND Flash原理和使用。

1. 概述

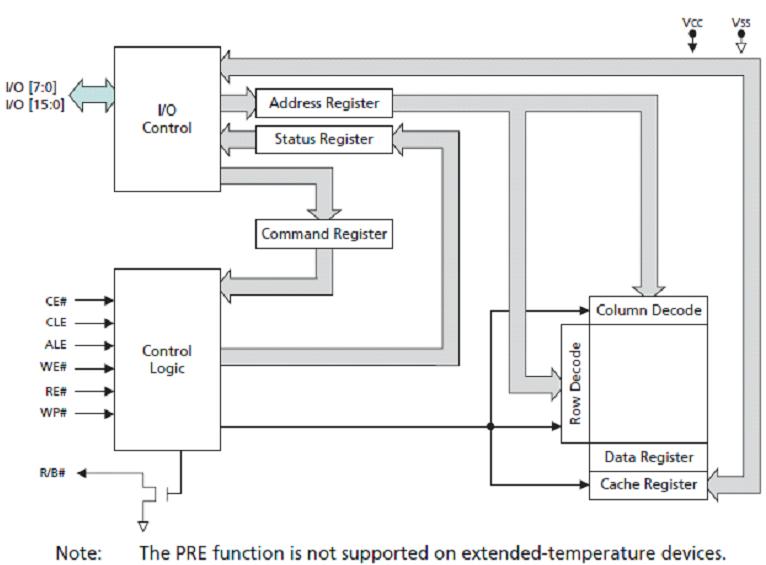

MT29F2G08使用一个高度复用的8-bit总线(I/O[7:0])来传输数据、地址、指令。5个命令脚(CLE、ALE、CE#、WE#)实现NAND命令总线接口规程。3个附加的脚用作: 控制硬件写保护(WP#)、监视芯片状态(R/B#),和发起上电自动读特征(PRE-仅3V芯片支持)。注意, PRE功能不支持宽温芯片。

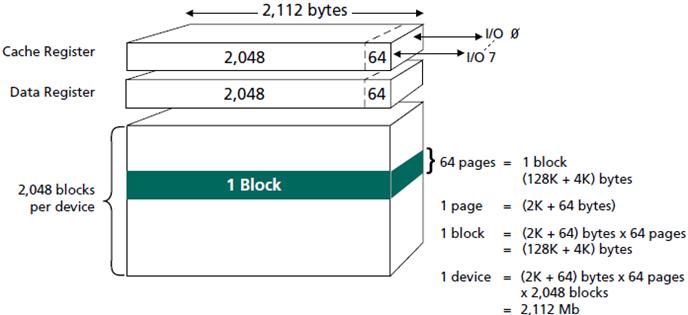

MT29F2G08内部有2048个可擦除的块,每个块分为64个可编程的页,每个页包含2112字节(2048个字节作为数据存储区,64个备用字节一般作为错误管理使用)。

每个2112个字节的页可以在300us内编程,每个块(64x2112=132K)可以在2ms内被擦除。片上控制逻辑自动进行PROGRAM和ERASE操作。

NAND的内部存储阵列是以页为基本单位进行存取的。读的时候,一页数据从内部存储阵列copy到数据寄存器,之后从数据寄存器按字节依次输出。写(编程)的时候,也是以页为基本单位的:起始地址装载到内部地址寄存器之后,数据被依次写入到内部数据寄存器,在页数据写入之后,阵列编程过程启动。

为了增加编程的速度,芯片有一个CACHE寄存器。在CACHE编程模式,数据先写入到CACHE寄存器,然后再写入到数据寄存器,一旦数据copy进数据寄存器后,编程就开始。在数据寄存器被装载及编程开始之后,CACHE寄存器变为空,可以继续装载下一个数据,这样内部的编程和数据的装载并行进行,提高了编程速度。

内部数据搬移命令(INTERNAL DATA MOVE)也使用内部CAHCE寄存器,通常搬移数据需要很长时间,通过使用内部CACHE寄存器和数据寄存器,数据的搬移速度大大增加,且不需要使用外部内存。

2. 功能框图

3. 管脚

|

名称 |

类型 |

描述 |

|

ALE |

I |

地址锁存使能。ALE为高时,在WE#下降沿,地址信息通过I/O[7:0]锁存片内的地址寄存器。如果传输的不是地址信息,ALE应该为低。 |

|

CE# |

I |

片选。一旦器件进入PROGRAM或ERASE操作,CE#可以变无效。 |

|

CLE |

I |

命令锁存使能。CLE为高时,在WE#上升沿,命令通过I/O[7:0]锁存到命令寄存器,当不传输命令时,CLE应该为低。 |

|

PRE |

I |

上电读使能。 |

|

RE# |

I |

读使能。 |

|

WE# |

I |

写使能。 |

|

WP# |

I |

写保护。当为低时候,所有的PROGRAM和ERASE都被禁止。 |

|

I/O[7:0] |

I/O |

数据输入/输出。传输命令、数据、地址。仅在读操作时,数据是输出。 |

|

R/B#, R/B2 |

O |

准备好/忙。集电极开路输出。外部需要接上拉电阻,这个脚表示芯片正在进行PROGRAM或ERASE操作。在读操作期间,表示数据正从阵列中传输到串行数据寄存器中,一旦这些操作完成,R/B#回到High-Z状态。 |

|

Vcc |

电源 |

电源 |

|

Vss |

地 |

地 |

4. 寻址

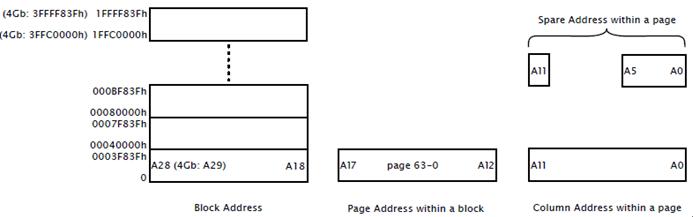

Block地址和页地址 = 实际的页地址,希望通过这个图,我们能理解块、页、块地址,页地址,列地址,备份空间,备份地址

|

Cycle |

I/O7 |

I/O6 |

I/O5 |

I/O4 |

I/O3 |

I/O2 |

I/O1 |

I/O0 |

|

1 |

CA7 |

CA6 |

CA5 |

CA4 |

CA3 |

CA2 |

CA1 |

CA0 |

|

2 |

LOW |

LOW |

LOW |

LOW |

CA11 |

CA10 |

CA9 |

CA8 |

|

3 |

RA19 |

RA18 |

RA17 |

RA16 |

RA15 |

RA14 |

RA13 |

RA12 |

|

4 |

RA27 |

RA26 |

RA25 |

RA24 |

RA23 |

RA22 |

RA21 |

RA20 |

|

5 |

LOW |

LOW |

LOW |

LOW |

LOW |

LOW |

LOW |

RA28 |

CAx:列地址;RAx=行地址

5. 总线操作

|

CLE |

ALE |

CE# |

WE# |

RE# |

WP# |

PRE# |

MODE |

|

|

H |

L |

L |

上升沿 |

H |

X |

X |

读模式 |

命令输入 |

|

L |

H |

L |

上升沿 |

H |

X |

X |

地址输入 |

|

|

H |

L |

L |

上升沿 |

H |

H |

X |

写模式 |

命令输入 |

|

L |

H |

L |

上升沿 |

H |

H |

X |

地址输入 |

|

|

L |

L |

L |

上升沿 |

H |

H |

X |

数据输入 |

|

|

L |

L |

L |

H |

下降沿 |

X |

X |

依次读和数据输出 |

|

|

L |

L |

L |

H |

H |

X |

X |

在读期间(忙) |

|

|

X |

X |

X |

X |

X |

H |

X |

在编程期间(忙) |

|

|

X |

X |

X |

X |

X |

H |

X |

在擦除期间(忙) |

|

|

X |

X |

X |

X |

X |

L |

X |

写保护 |

|

|

X |

X |

H |

X |

X |

0V/Vcc |

0V/Vcc |

待机 |

|

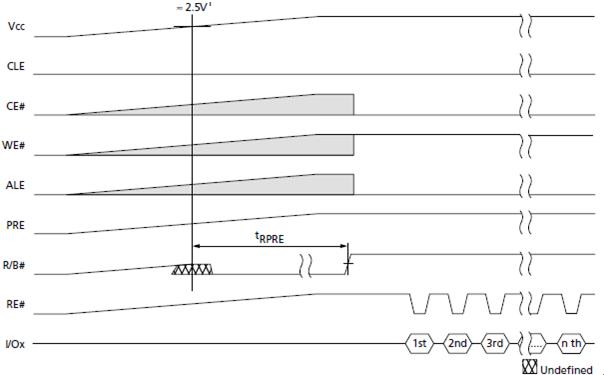

上电自动读:在上电期间,PRE为VCC,3V VCC器件自动传输第一页到数据寄存器,而无需要发布一个命令或地址锁存序列。在VCC达到大约2.5V的时候,内部电压检测器触发上电自动读功能。在第一页数据copy到数据寄存器过程中,R/B#为低,当copy结束后,R/B#变高,在RE#脉冲的作用下第一页数据可以依次输出。

6. 命令表

|

操作 |

周期1 |

周期2 |

在忙期间有效 |

|

PAGE READ |

0x00 |

0x30 |

NO |

|

PAGE READ CACHE MODE START |

0x31 |

- |

NO |

|

PAGE READ CACHE MODE START LAST |

0x3F |

- |

NO |

|

READ for INTERNAL DATA MOVE |

0x00 |

0x35 |

NO |

|

RANDOM DATA READ |

0x05 |

0xE0 |

NO |

|

READ ID |

0x90 |

- |

NO |

|

READ STATUS |

0x70 |

- |

NO |

|

PROGRAM PAGE |

0x80 |

0x10 |

NO |

|

PROGRAM PAGE CACHE |

0x80 |

0x15 |

NO |

|

PROGRAM for INTERNAL DATA MOVE |

0x85 |

0x10 |

NO |

|

RANDOM DATA INPUT for PROGRAM |

0x85 |

- |

NO |

|

BLOCK ERASE |

0x60 |

0xD0 |

NO |

|

RESET |

0xFF |

- |

YES |

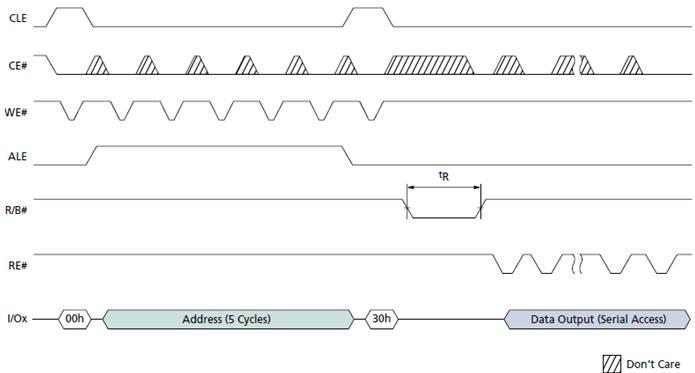

7. PAGE READ,0x00-0x30

5个地址周期,确定了读出的起始地址,数据才RE#脉冲的作用下,从这个起始地址开始依次输出,直到这一页的结束。

8. RANDOM DATA READ,0x05-0xE0

随机数据读,是为了用户能够设定新的列地址,增加数据读出的灵活性,随即读模式在页读(0x00-0x30序列)后使能。这个命令的发布次数是不受限制的。但仅仅是当前页数据的读出。

9. PAGE READ CACHE MODE START,0x31;PAGE READ CACHE MODE START LAST,0x3F

发布PAGE READ命令后,在R/B#变高后,在发送0x31命令,这时启动将数据寄存器的内容传给CACHE寄存器,然后就可以顺序从CACHE里读第一个PAGE READ命令获得数据,由于这是数据寄存器是没有用的,因此,芯片自动启动读下一页的PAGE READ命令,将下一页读到数据寄存器,可以看出这么做提高的读出的速度,除了第一个PAGE READ命令外,其他PAGE READ命令都是后台自动进行的。再最后一次使用0x3F命令,以便禁止芯片再次自动发布PAGE READ命令。

10. READ ID,0x90

读出厂家的芯片标识。

11. READ STATUS,0x70

读出芯片的8bit状态。可以通过RE#脉冲,反复读。

12. 编程操作

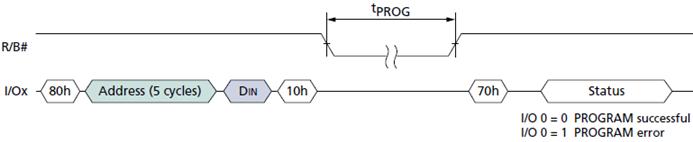

PROGRAM PAGE 0x80-0x10:

Micron NAND FLASH仅支持页的编程,在一个块以内,页必须从一个块的页最低位到这个块的页的最高位连续编程,禁止随机页地址的编程。

芯片也支持页的部分编程操作,这意味着任何单个位在需要一个擦除之前仅可以被编程一次,然而,这种页能被划分成在需要一个擦除之前允许最大8个编程操作。

SERIAL DATA INPUT 0x80:

PAGE PROGRAM操作要求加载SERAIL DATA INPUT(0x80)命令进入命令寄存器,随着5个地址周期之后,串行数据通过连续的WE#周期加载到值得的起始地址,PROGRAM(0x10)命令在数据输入完成之后被写入,内部写状态周期自动执行合适的编程算法,并控制所有必要的定时编程和比较操作。写比较仅仅检测“1”是否被成功地编程为“0”了。

R/B#在阵列编程期间(tPROG)为低,在编程操作期间,仅READ STATUS和RESET命令有效,状态寄存器的Bit6反映R/B#的状态,当芯片准备好时,读Bit0的状态确定编程操作是否成功或失败,命令寄存器在新的有效命令写入之前,一直停留在读状态寄存器模式。

RANDOM DATA INPUT 0x85:

在发起数据集输入之后,可以通过RANDOM DATA INPUT命令向新的列地址写入数据。在发布0x10命令之前,可以对同一页多次使用0x85命令。

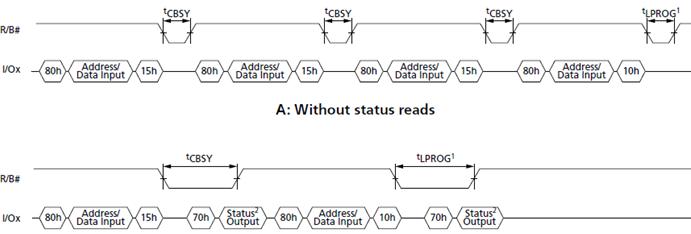

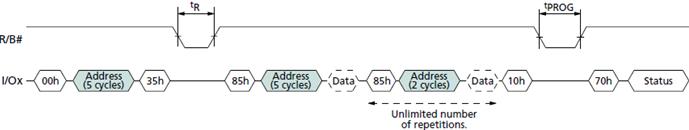

PROGRAM PAGE CACHE MODE 0x80-0x15:

CACHE编程实际上是标准的页编程命令的带缓冲编程模式,编程开始是发布SERIAL DATA INPUT(0x80)命令,随后是5个地址周期,以及页的全部或部分数据,数据copy到CACHE寄存器,然后发布CACHE WRITE(0x15)命令。数据在WE#的上升沿锁存到数据寄存器,在这个锁存期间,R/B#为低,锁存结束之后,R/B#变高,编程开始。

当R/B#变高之后,新的数据可以通过发布另一个CACHE PROGRAM命令来写入,R/B#保持低的时候由实际的编程时间来控制,第一次等于数据从CACHE寄存器写入到数据寄存器需要的时间,之后,只有数据寄存器的内容被编程进阵列之后,CACHE寄存器才能锁存到数据寄存器,所有,以后的R/B#为低的实际应该更长一些。

状态寄存器中反映CACHE R/B#的Bit6可以通过READ STATUS命令读出,以便确定什么时候,CACHE寄存器准备好接受新的数据了。

状态寄存器中反映R/B#的Bit5可以被查询,以确定什么时候当前编程周期的实际阵列编程完成。

如果仅使用R/B#来确定编程是否完成,那么编程序列的最后一页必须使用PROGRAM PAGE(0x10)来替代CACHE PROGRAM(0x15)。如果CACHE PROGRAM命令每次都使用,状态寄存器的Bit5必须用来确定编程是否结束。

当状态寄存器的bit6为1时,状态寄存器Bit0返回前一页的编程是否成功,当前PROGRAM操作的成功与否的状态是:Bit5为“1”(准备好状态)时的Bit0状态

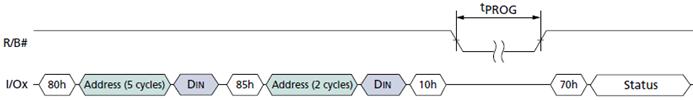

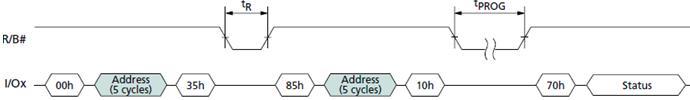

13. 内部数据搬移

内部数据搬移需要两个命令序列,先发布一个READ FOR INTERNAL DATA MOVE(0x00-0x35),然后发布一个INTERNAL DATA MOVE(0x85-0x10)命令,数据搬移仅仅支持被读数据die范围。

READ FOR DATA MOVE 0x00-0x35:先将00写到命令寄存器,然后是内部源地址(5个周期),之后,将0x35写到命令寄存器,这将起动从内存传输一页到CACHE寄存器。尽管5个周期的地址被发布,但是列地址是被忽略的。现在芯片准备接受INTERNAL DATA MOVE(0x85-0x00)命令。

INTERNAL DATA MOVE 0x85-0x10:在READ FOR INTERNAL DATA MOVE命令发布之后,以及R/B#变高,就可以发布INTERNAL DATA MOVE命令了,这个命令将CACEH寄存器内容传输到数据寄存器,然后编程到新的目标地址,再INTERNAL DATA MOVE命令以及地址序列之后,R/B#变低,同时内部控制逻辑自动将数据编程到新的页,READ STATUS命令和状态寄存器的bit6能代替R/B#,以确定编程什么时候完成。状态寄存器Bit0指示操作是否成功。在INTERNAL DATA MOVE命令序列期间,RANDOM DATA INPUT(0x85)用来修改原始数据的一个或多个字:首先,使用0x00-0x35命令序列将数据copy到CACHE寄存器,然后,使用带要修改的数据地址的命令RANDOM DATA INTPUT(0x85),新的数据输入呈现在外部数据脚,这将copy新的数据进入CACHE寄存器。当0x10写入命令寄存器时候,原始数据+修改的数据被传输到数据寄存器。编程新的一页将开始,如果有必要RANDOM DATA INPUT命令可以在启动编程序列(0x10)之前发布多次。因为INTERNAL DATA MOVE操作并不使用外部内存,所以ECC不可能在编程之前用来检查错误,这将可能或导致数据错误。在这种情况下,执行多次INTERNAL DATA MOVE操作,这些位错误可能会因没有校正而积累。由于这个原因,我们强烈推荐利用INTERNAL DATA MOVE的系统使用鲁棒ECC方案。这将可以对每个SECTOR校正2个或多个错误。

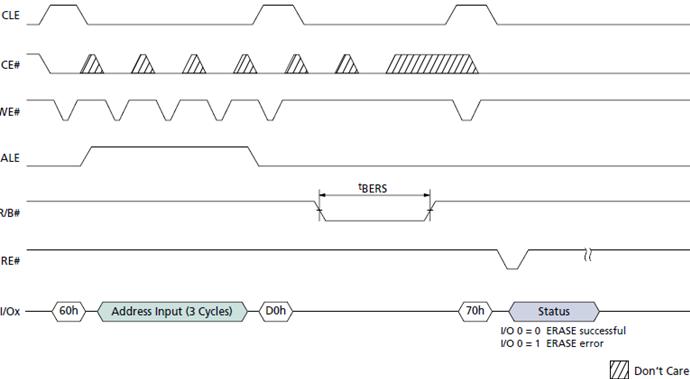

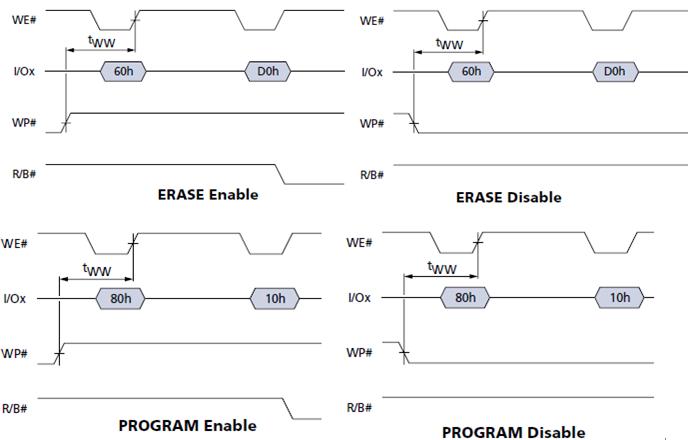

14. 块擦除操作,0x60-0xD0

一次擦除一个块。三个周期的地址A[28:18]被要求,先发布ERASE SETUP(0x60)命令,然后是三个地址周期,之后是ERASE CONFIRM(0xD0)命令。通过READ STATUS RESGISTER命令读擦除操作的状态,当bit6=1时,操作完成,Bit0指示通过/失败条件,0表示通过。

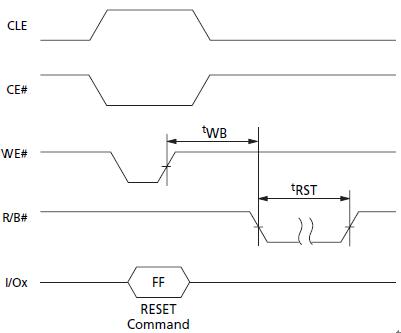

15. 复位操作,0xFF

复位操作使芯片进入一个已知的状态,中断正在处理的命令序列。RANDOM READ、PROGRAM、ERASE命令在芯片忙状态可以被中断,正在被编程的位置或正在擦除的块的内容变无效,数据有可能会部分地被擦除或编程。命令寄存器被清除,准备好进入下一个命令。

复位后状态寄存器内容:

|

条件 |

状态 |

Bit7 |

Bit6 |

Bit5 |

Bit4 |

Bit3 |

Bit2 |

Bit1 |

Bit0 |

Hex |

|

WP#高 |

准备好 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0xE0 |

|

WP#低 |

准备好和写保护 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0x60 |

16. 写保护操作

写保护是为了防止不小心的编程和擦除操作。当WP#为低时候,所有的编程和擦除操作都会被禁止。

17. 错误管理

Micron NAND芯片出厂时并不保证芯片中所有的块都是好的,只要2048个块中有不少于2008个完好块就认为是合格品可以出厂。但是坏的块的存在,并不影响好的块的操作。在应用系统中应该提供坏块影射、替代、错误校正等算法就可以保证数据具有很高的可靠性和完整性。

每个CE#的第一个块(物理块地址是0)绝对是经过测试,是完好无缺的。这就提供了存放BOOT代码和重要信息的存储位置。

在芯片出厂之前,厂家会在每个坏块的第一或第二页的第一个备份位置(列地址是2048)用非0xFF编程来标识坏块。

系统软件在进行任何擦除或编程操作之前应该检查每个块的第一或第二页的第一个备份地址数据。这样创建一个坏块表。

经过一定时间的使用,内存的某些位置可能会不能正确地编程和擦除,为了确保数据的可靠性,应该采取一些预防措施,比如:

l 在写、擦除、或数据搬移操作之后,总是检查状态。

l 使用某些类型的错误检测纠正算法,以便能恢复某些轻微iede1错误。

l 使用坏块替代算法。

NAND Flash【转】的更多相关文章

- 嵌入式Linux驱动学习之路(二十三)NAND FLASH驱动程序

NAND FLASH是一个存储芯片. 在芯片上的DATA0-DATA7上既能传输数据也能传输地址. 当ALE为高电平时传输的是地址. 当CLE为高电平时传输的是命令. 当ALE和CLE都为低电平时传输 ...

- (一)Nand FLASH 原理讲解

NAND FLASH 优势 : 可以用当硬盘 这里好像型号是 K9F2G08 基本结构: 不是很难自己看看,暂时不要看

- NAND flash sub-pages

http://www.linux-mtd.infradead.org/doc/ubi.html#L_subpage NAND flash sub-pages As it is said here, a ...

- Nand Flash,Nor Flash,CFI Flash,SPI Flash 之间的关系

前言: 在嵌入式开发中,如uboot的移植,kernel的移植都需要对Flash 有基本的了解.下面细说一下标题中的中Flash中的关系 一,Flash的内存存储结构 flash按照内部存 ...

- 硬件初始化,nand flash固化操作,系统启动简单流程

2015.3.27星期五 晴 链接脚本定义代码的排放顺序 硬件系统初始化:一:arm核初始化:(里面有指令)初始化ARM核的时候需要看arm核的手册指令:1.异常向量(最起码有个复位异常,初始化模式- ...

- 第8章 NAND FLASH控制器

8.1 NAND Flash介绍和NAND Flash控制器使用 NAND Flash在嵌入式系统中的地位与PC上的硬盘类似 NAND Flash在掉电后仍可保存 8.1.1 Flash介绍 有NOR ...

- s3c2440 移值u-boot-2016.03 第4篇 支持NAND flash 识别

1, /include/configs/smdk2440.h 中添加 #define CONFIG_CMD_NAND 编译 drivers/mtd/nand/built-in.o: In functi ...

- s3c2440 移值u-boot-2016.03 第2篇 支持Nand flash启动

1, 要求:在4K 的代码以内,完成 NOR NAND 类型判断,初始化 NAND 复制自身到 SDRAM ,重定向. 2, 在 /arch/arm/cpu/arm920t/ 文件夹里 添加一个 in ...

- Linux学习 : 裸板调试 之 配置使用NAND FLASH

关于NAND FLASH的结构是以页为单位写,以块为单位来擦除: 1Gb 为大页 page=2048Kb BLOCK=128K 512Mb 为小页 page=512byte ...

- Smart210学习记录----nand flash驱动

[详解]如何编写Linux下Nand Flash驱动 :http://www.cnblogs.com/linux-rookie/articles/3016990.html 当读写文件请求到来的时候, ...

随机推荐

- Gulp压缩JavaScript代码

因为gulp是自动化工具,所以我们得告诉它,需要怎么做,才能达到我们的目的. 我们首先得新建一个js文件,用来编写我们的需求,以便gulp能按着我们的意愿来执行. 我将这个js文件取名叫gulpfil ...

- Matlab中diag函数注意事项

在给李X写SVD代码的时候注意到的. >> a = magic(3) a = 8 1 6 3 5 7 4 9 2 >> diag(a) ans = 8 5 2 >> ...

- Leetcode#109 Convert Sorted List to Binary Search Tree

原题地址 跟Convert Sorted Array to Binary Search Tree(参见这篇文章)类似,只不过用list就不能随机访问了. 代码: TreeNode *buildBST( ...

- GS线程

void GameServer::ProcessThread() { try {//在ui线程里面搞个大try不是说try效率不好吗,难道只是为了出现错误发现在GS线程里面出现的吗 ProcessTh ...

- SQL Server中存储过程 比 直接运行SQL语句慢的原因

问题是存储过程的Parameter sniffing 在很多的资料中都描述说SQLSERVER的存储过程较普通的SQL语句有以下优点: 1. 存储过程只在创造时进行编译即可,以后每次执行存储过 ...

- JavaScript之substring()方法讲解

定义和用法 substring() 方法用于提取字符串中介于两个指定下标之间的字符. 语法 stringObject.substring(start,stop) 参数 描述 start 必需.一个非负 ...

- 获取app版本号

NSDictionary *infoDictionary = [[NSBundle mainBundle] infoDictionary]; NSString *name = [infoDiction ...

- js返回上一页报网页过期问题解决

1.detail详细页面加上返回按钮,返回到list列表页 <input type="button" value=" 返回 " onclick=" ...

- vc++ 获取当前用户名

#include<afxwin.h> #include <stdio.h> int main(void) { char userName[MAX_PATH]; unsigned ...

- ZOJ3238 Water Ring(计算几何)

题意:给你一个圆形和很多个矩形,然后要你求圆形的圆周有多少被矩形覆盖. 思路:比赛的时候是有思路的了,不过一直在调别的题,最后剩下30分钟肯定来不及敲.想法是这样的,要是我们可以求出每个矩形覆盖了圆周 ...