Verilog 加法器和减法器(6)

为了减小行波进位加法器中进位传播延迟的影响,可以尝试在每一级中快速计算进位,如果能在较短时间完成计算,则可以提高加法器性能。

我们可以进行如下的推导:

设 gi=xi&yi, pi = xi +y i

ci+1 = xi&y i+x i&ci+yi&ci=xi&yi + (xi+yi)&ci=g i+pi&c i = gi+pi&(gi-1+pi-1&ci-1)=g i+pi&g i-1+pi&pi-1&ci-1= ….=gi+pi &gi-1+pi &pi-1&gi-2+…+pi&pi-1…p2&p1 &g0+pi &pi-1..p1 &p0&c0; 实现这个逻辑电路的加法器是超前进位加法器。从公式中,可以看出门延时要比行波进位加法器小很多。但是电路复杂,逻辑门的扇入数量将限制超前进位加法器的速度。

由于扇入数量限制,通常我们仅实现4位超前进位加法器和8位超前进位加法器,然后在串联成16/32/64等高位加法器。

下面是4位和8位的超前进位加法器代码:

module adder4_fast(

cin,

x,

y,

s,

cout

); input cin;

input [3:0] x;

input [3:0] y;

output [3:0] s;

output cout; wire [4:0] g,p,c; assign c[0] = cin;

assign p = x | y;

assign g = x & y;

//assign c[1] = g[0] | (p[0] & c[0]);

//assign c[2] = g[1] | (p[1] & (g[0] | (p[0] & c[0])));

//assign c[3] = g[2] | (p[2] & (g[1] | (p[1] & (g[0] | (p[0] & c[0])))));

//assign c[4] = g[3] | (p[3] & (g[2] | (p[2] & (g[1] | (p[1] & (g[0] | (p[0] & c[0])))))));

assign c[1] = g[0] | (p[0] & c[0]);

assign c[2] = g[1] | (p[1]&g[0])|(p[1]&p[0]&c[0]);

assign c[3] = g[2] | (p[2]&g[1])|(p[2]&p[1]&g[0])|(p[2]&p[1]&p[0]&c[0]);

assign c[4] = g[3] | (p[3]&g[2])|(p[3]&p[2]&g[1])|(p[3]&p[2]&p[1]&g[0])|(p[3]&p[2]&p[1]&p[0]&c[0]);

assign s = x^y^c[3:0];

assign cout = c[4]; endmodule

module adder8_fast(

cin,

x,

y,

s,

cout

); input cin;

input [7:0] x;

input [7:0] y;

output [7:0] s;

output cout; wire [8:0] g,p,c; assign c[0] = cin;

assign p = x | y;

assign g = x & y;

//assign c[1] = g[0] | (p[0] & c[0]);

//assign c[2] = g[1] | (p[1] & (g[0] | (p[0] & c[0])));

//assign c[3] = g[2] | (p[2] & (g[1] | (p[1] & (g[0] | (p[0] & c[0])))));

//assign c[4] = g[3] | (p[3] & (g[2] | (p[2] & (g[1] | (p[1] & (g[0] | (p[0] & c[0])))))));

//assign c[5] = g[4] | (p[4] & (g[3] | (p[3] & (g[2] | (p[2] & (g[1] | (p[1] & (g[0] | (p[0] & c[0])))))))));

//assign c[6] = g[5] | (p[5] & (g[4] | (p[4] & (g[3] | (p[3] & (g[2] | (p[2] & (g[1] | (p[1] & (g[0] | (p[0] & c[0])))))))))));

//assign c[7] = g[6] | (p[6] & (g[5] | (p[5] & (g[4] | (p[4] & (g[3] | (p[3] & (g[2] | (p[2] & (g[1] | (p[1] & (g[0] | (p[0] & c[0])))))))))))));

//assign c[8] = g[7] | (p[7] & (g[6] | (p[6] & (g[5] | (p[5] & (g[4] | (p[4] & (g[3] | (p[3] & (g[2] | (p[2] & (g[1] | (p[1] & (g[0] | (p[0] & c[0])))))))))))))));

assign c[1] = g[0] | (p[0] & c[0]);

assign c[2] = g[1] | (p[1]&g[0])|(p[1]&p[0]&c[0]);

assign c[3] = g[2] | (p[2]&g[1])|(p[2]&p[1]&g[0])|(p[2]&p[1]&p[0]&c[0]);

assign c[4] = g[3] | (p[3]&g[2])|(p[3]&p[2]&g[1])|(p[3]&p[2]&p[1]&g[0])|(p[3]&p[2]&p[1]&p[0]&c[0]);

assign c[5] = g[4] | (p[4]&g[3])|(p[4]&p[3]&g[2])|(p[4]&p[3]&p[2]&g[1])|(p[4]&p[3]&p[2]&p[1]&g[0])|(p[4]&p[3]&p[2]&p[1]&p[0]&c[0]);

assign c[6] = g[5] | (p[5]&g[4])|(p[5]&p[4]&g[3])|(p[5]&p[4]&p[3]&g[2])|(p[5]&p[4]&p[3]&p[2]&g[1])|(p[5]&p[4]&p[3]&p[2]&p[1]&g[0])|(p[5]&p[4]&p[3]&p[2]&p[1]&p[0]&c[0]);

assign c[7] = g[6] | (p[6]&g[5])|(p[6]&p[5]&g[4])|(p[6]&p[5]&p[4]&g[3])|(p[6]&p[5]&p[4]&p[3]&g[2])|(p[6]&p[5]&p[4]&p[3]&p[2]&g[1])|(p[6]&p[5]&p[4]&p[3]&p[2]&p[1]&g[0])|(p[6]&p[5]&p[4]&p[3]&p[2]&p[1]&p[0]&c[0]);

assign c[8] = g[7] | (p[7]&g[6])|(p[7]&p[6]&g[5])|(p[7]&p[6]&p[5]&g[4])|(p[7]&p[6]&p[5]&p[4]&g[3])|(p[7]&p[6]&p[5]&p[4]&p[3]&g[2])|(p[7]&p[6]&p[5]&p[4]&p[3]&p[2]&g[1])|(p[7]&p[6]&p[5]&p[4]&p[3]&p[2]&p[1]&g[0])|(p[7]&p[6]&p[5]&p[4]&p[3]&p[2]&p[1]&p[0]&c[0]);

assign s = x^y^c[7:0];

assign cout = c[8]; endmodule

下面的代码把4个超前进位加法器串联起来,形成一个32位加法器。

module addern_fast(

cin,

x,

y,

s,

cout

); input cin;

input [31:0] x;

input [31:0] y;

output [31:0] s;

output cout;

wire [2:0] cout_tmp; adder8_fast adder8_fast_0(.cin(cin),.x(x[7:0]),.y(y[7:0]),.s(s[7:0]),.cout(cout_tmp[0]));

adder8_fast adder8_fast_1(.cin(cout_tmp[0]),.x(x[15:8]),.y(y[15:8]),.s(s[15:8]),.cout(cout_tmp[1]));

adder8_fast adder8_fast_2(.cin(cout_tmp[1]),.x(x[23:16]),.y(y[23:16]),.s(s[23:16]),.cout(cout_tmp[2]));

adder8_fast adder8_fast_3(.cin(cout_tmp[2]),.x(x[31:24]),.y(y[31:24]),.s(s[31:24]),.cout(cout)); endmodule

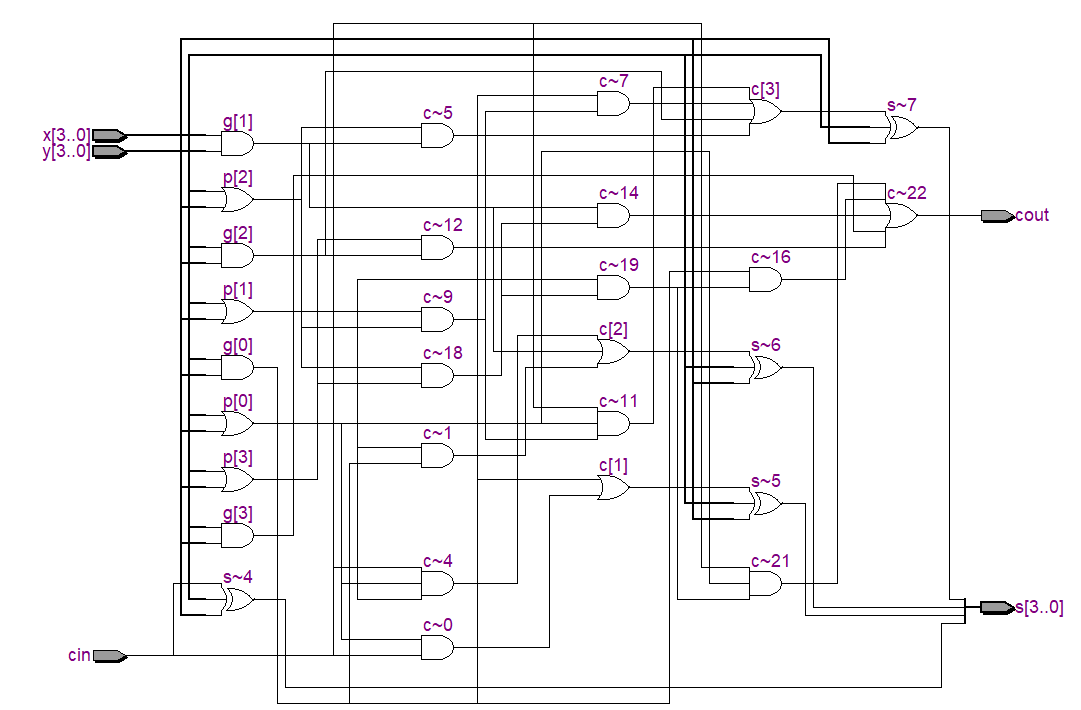

下面是4位超前进位加法器的逻辑图:

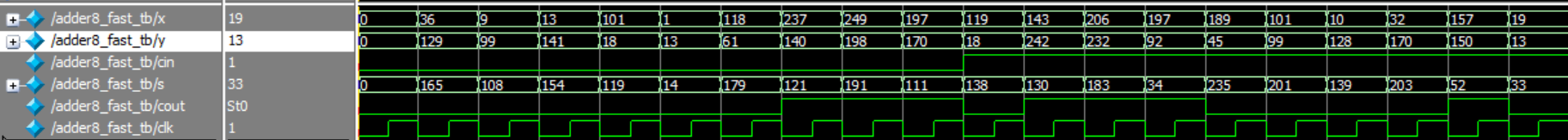

8位超前进位加法器的波形结果。

Verilog 加法器和减法器(6)的更多相关文章

- Verilog 加法器和减法器(8)-串行加法器

如果对速度要求不高,我们也可以使用串行加法器.下面通过状态机来实现串行加法器的功能. 设A=an-1an-2-a0, B=bn-1bn-2-b0,是要相加的两个无符号数,相加的和为:sum=sn-1s ...

- Verilog 加法器和减法器(4)

类似于行波进位加法器,用串联的方法也能够实现多位二进制数的减法操作. 比如下图是4位二进制减法逻辑电路图. 8位二进制减法的verilog代码如下: module subn(x, y, d,cin) ...

- Verilog 加法器和减法器(7)

在计算机中浮点数 表示通常采用IEEE754规定的格式,具体参考以下文章. https://www.cnblogs.com/mikewolf2002/p/10095995.html 下面我们在Veri ...

- Verilog 加法器和减法器(3)

手工加法运算时候,我们都是从最低位的数字开始,逐位相加,直到最高位.如果第i位产生进位,就把该位作为第i+1位输入.同样的,在逻辑电路中,我们可以把一位全加器串联起来,实现多位加法,比如下面的四位加法 ...

- Verilog 加法器和减法器(2)

类似半加器和全加器,也有半减器和全减器. 半减器只考虑当前两位二进制数相减,输出为差以及是否向高位借位,而全减器还要考虑当前位的低位是否曾有借位.它们的真值表如下: 对半减器,diff = x ^y, ...

- Verilog 加法器和减法器(1)

两个一位的二进制数x,y相加,假设和为s,进位为cout,其真值表为: 从真值表中,我们可以得到:s = x^y, cout = x&y,实现两个一位数相加的逻辑电路称为半加器. 实现该电路的 ...

- Verilog 加法器和减法器(5)

前面二进制加法运算,我们并没有提操作数是有符号数,还是无符号数.其实前面的二进制加法对于有符号数和无符号数都成立.比如前面的8位二进制加法运算,第一张图我们选radix是unsigned,表示无符号加 ...

- 基于Xilinx的Synthesize

所谓综合.就是讲HDL语言.原理图等设计输入翻译成由与.或.非们和RAM.触发器登记本逻辑单元的逻辑连接(即网表).并依据目标和要求(约束条件)优化生成的逻辑连接. ISE-XST XST是Xilin ...

- FPGA综合工具--Synplify Pro的常用选项及命令

最近要用到Synplify,但以前没使用过,无基础,找到一篇帖子,隧保存下来. 本文转自:http://blog.sina.com.cn/s/blog_65fe490d0100v8ax.html Sy ...

随机推荐

- [代码审计]云ec电商系统代码审计

0x00 前言 看了一下博客内最新的文章,竟然是3月28号的,一个多月没写文章了,博客都长草了. 主要是临近毕业,事情繁多,也没有啥时间和心情静下来写.. 不过现在的话,毕业的东西告一段落了,几乎没啥 ...

- php模板引擎之featherview

在纯php文件中不加php结束符是一个好习惯,php结束符仅用于在php与html混写时标示php代码结束. <? ?>是短标签,<?php ?>是长标签,在php的配置文件( ...

- List,Set的区别

1.List,Set都是继承自Collection接口2.List特点:元素有放入顺序,元素可重复 ,Set特点:元素无放入顺序,元素不可重复(注意:元素虽然无放入顺序,但是元素在set中的位置是有该 ...

- jQuery方法实现

children 原生JavaScript中,如果希望找到某个元素的子元素,只能通过Node类型上的children方法一步一步获取.如 let li = document.querySelector ...

- Wannafly挑战赛21A

题目链接 Wannafly挑战赛21A 题解 代码 #include <cstdio> #include <cmath> #define MAX 1000005 #define ...

- UVA.11427.Expect the Expected(期望)

题目链接 \(Description\) https://blog.csdn.net/Yukizzz/article/details/52084528 \(Solution\) 首先每一天之间是独立的 ...

- LOJ.2863.[IOI2018]组合动作(交互)

题目链接 通过两次可以先确定首字母.然后还剩下\(n-1\)位,之后每一位只有三种可能. 最简单的方法是每次确定一位,通过两次询问显然可以确定.但是只能一次询问. 首字母只会出现一次,即我们可以将串分 ...

- hdu 4432 第37届ACM/ICPC天津现场赛B题

题目大意就是找出n的约数,然后把约数在m进制下展开,各个数位的每一位平方求和,然后按m进制输出. 模拟即可 #include<cstdio> #include<iostream> ...

- Codeforces Round #394 (Div. 2) C. Dasha and Password 暴力

C. Dasha and Password 题目连接: http://codeforces.com/contest/761/problem/C Description After overcoming ...

- Meta对照表

Http Content_type对照表: 文件扩展名 Content-Type(Mime-Type) 文件扩展名 Content-Type(Mime-Type) .*( 二进制流,不知道下载文件类型 ...