FPGA内部动态可重置PLL讲解(一)

SDRAM驱动需要两个时钟,一个是控制时钟,一个是驱动时钟,这两个时钟有一个相位差,如何产生高精度的时钟是SDRAM能够正常工作的关键,采用FPGA内部动态可重置PLL生成SDRAM所需要的时钟频率。

1.PLL

上图是PLL的 官方文档中的内容。PLL主要由前N分频计数器(pre-divider counter),相位频率检测(PFD) ,电荷泵和环路滤波器,VCO(压控振荡器),反馈乘法器计数器(M计数器)和一个后分频计数器。

上图是PLL的 官方文档中的内容。PLL主要由前N分频计数器(pre-divider counter),相位频率检测(PFD) ,电荷泵和环路滤波器,VCO(压控振荡器),反馈乘法器计数器(M计数器)和一个后分频计数器。

PFD检测参考时钟信号(fREF)和补偿时钟信号(feedback)在相位和频率的差,然后控制电荷泵和环路滤波器,并且将相位差转换成一个控制电压信号,进而控制VCO。当PFD产生上升信号,VCO就增加,反之VCO下降。

上图中电荷泵是接收PFD输出的上升信号和下降信号给CP,CP收到上升信号,电流注入LF增大,反之减小。

LF主要是将上升和下降信号转换为电压,作为VCO的偏置电压。LF还消除了CP的干扰,防止电压过冲,最小化减少VCO的抖动。LF电压决定了VCO的操作速度。

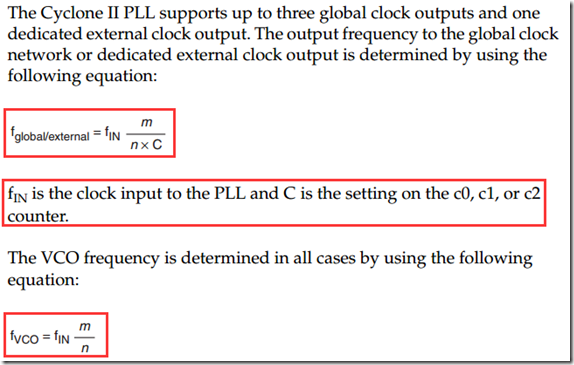

上图是输出频率的计算公式,M和N在quartus II中类似于倍频和分频概念。PLL的精度由M和N的位数决定。

精简结构如下图所示:

2.quartus II 配置PLL操作

在PLL官方手册中可以找到如上图手册,对于其他cyclone XX系列芯片,操作都是类似的。

上图中解释了对于cyclone xx系列最高可以跑到多大时钟频率。

上面公式定义了 fout时钟和VCO时钟,且VCO时钟必须在300~1000Mhz之间。手册有如下解释。

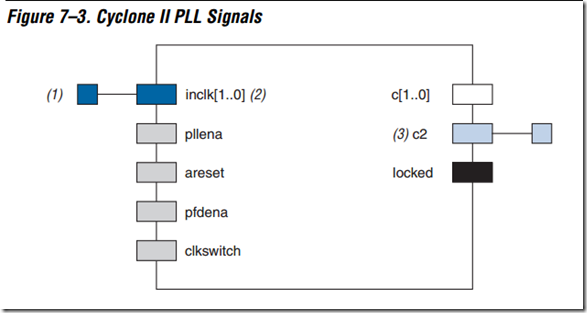

上图是PLL中所需要的信号接口,有些信号可以进行选择性的使用。

inclk为时钟输入引脚,pllena信号在高电平时可以使能和复位PLL。当pllena为低电平时,PLL不工作,高电平PLL开始锁相。

areset引脚要特别注意,此引脚我们经常用,此引脚是高电平复位,低电平时PLL不工作。

3.PLL时钟补偿模式

PLL支持四种补偿模式,正常模式(normal mode),零延时缓冲模式(zero delay buffer mode),非补偿模式(no compensation mode),源同步模式(source synchronous mode)。上述的几种模式都支持倍频和分频,相移以及占空比的可调。

(1)正常模式(normal mode)

在正常模式下,PLL将输入时钟与参考时钟进行锁存对齐,输出时钟或者提前或者延后与PLL的输入时钟。

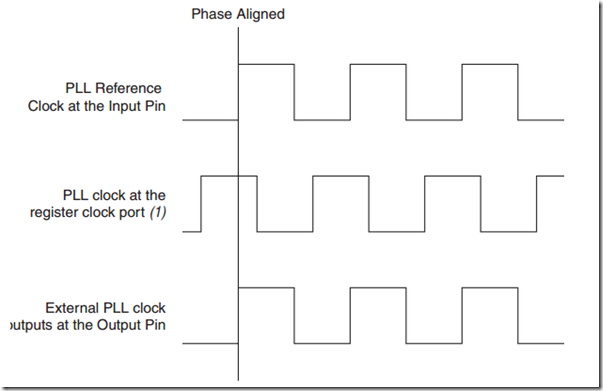

(2)零延时缓冲模式(zero delay buffer mode)

再此模式下,PLL的输入时钟的相位和PLL的输出时钟相位对齐,但是内部时钟会延时或提前于外部输出时钟。在此模式下,altera推荐输入引脚和输出引脚必须是相同的I/O标准。

再此模式下,PLL的输入时钟的相位和PLL的输出时钟相位对齐,但是内部时钟会延时或提前于外部输出时钟。在此模式下,altera推荐输入引脚和输出引脚必须是相同的I/O标准。

(3)非补偿模式(no compensation mode)

在此模式下,PLL不会对任何的相位进行补偿。输出时钟相位超前或迟滞内部时钟。

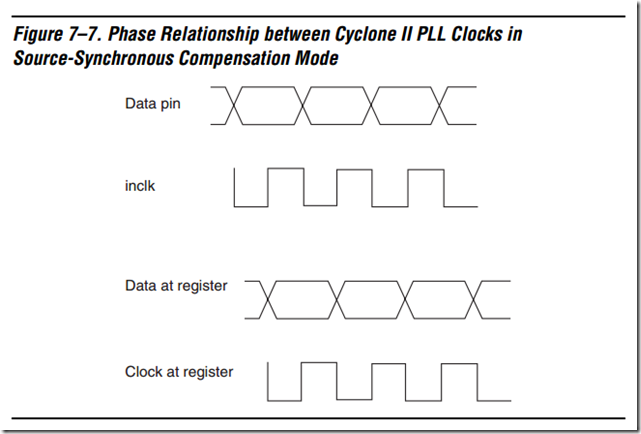

(4)源同步模式(source synchronous mode)

这种情况适用于输入数据和时钟同时到达的情况。

4.多个频率输出情况

上述三个输出时钟都可以驱动全局时钟网络。c2可以驱动一个专用外部I/O引脚(PLL<#>_OUT) 。那么对于多个利用PLL输出的频率,VCO在处理时会倍频。然后在输出时再降频,如从PLL输出需要33MHz和66MHz,那么VCO会被设定到330MHz(这个设定需要在VCO范围内,即300Mhz~1000Mhz)。

上述三个输出时钟都可以驱动全局时钟网络。c2可以驱动一个专用外部I/O引脚(PLL<#>_OUT) 。那么对于多个利用PLL输出的频率,VCO在处理时会倍频。然后在输出时再降频,如从PLL输出需要33MHz和66MHz,那么VCO会被设定到330MHz(这个设定需要在VCO范围内,即300Mhz~1000Mhz)。

FPGA内部动态可重置PLL讲解(一)的更多相关文章

- FPGA内部动态可重置PLL讲解(二)

对于全局时钟的管理,涉及到关于亚稳态的知识,大家可以上网搜索相关资料,这里不再赘述.亚稳态最简单的理解形式是无法判断是处于高电平状态还是处于低电平状态,这样会导致整个系统不稳定,会出现逻辑上的错误. ...

- FPGA 内部详细架构你明白了吗?

FPGA 芯片整体架构如下所示,大体按照时钟域划分的,即根据不同的工艺.器件速度和对应的时钟进行划分: FPGA 内部详细架构又细分为如下六大模块: 1.可编程输入输出单元(IOB)(Input Ou ...

- FPGA内部硬件结构简介

我们知道FPGA内部有很多可供用户任意配置的资源,其中包括:可编程逻辑.可编程I/O.互连线.IP核等资源,很多学过数字电路的人都知道与或非门可以构成几乎所有的数字电路,但是FPGA内部最基本的主要单 ...

- 关于 FPGA 内部信号扇入扇出

扇入.扇出系数 扇入系数是指门电路允许的输入端数目.一般门电路的扇入系数为1—5,最多不超过8.扇出系数是指一个门的输出端所驱动同类型门的个数,或称负载能力.一般门电路的扇出系数为8,驱动器的扇出系数 ...

- 【转】FPGA内部小数计算

FPGA内部计算小数 [转载] 谓定点小数,就是小数点的位置是固定的.我们是要用整数来表示定点小数,由于小数点的位置是固定的,所以就没有必要储存它(如果储存了小数点的位置,那就是浮点数了).既然没有 ...

- FPGA内部信号避免高阻态

RT,否则警告Warning: Tri-state node(s) do not directly drive top-level pin(s),会利用或门代替中间的扇出fan-out. 原因:在进行 ...

- FPGA内部IP核DDS

项目当中需要正弦信号与余弦信号,首先想到了DDS芯片,例如AD9833.AD9834.由于还需要用FPGA 做一些数据处理,后来干脆直接用FPGA 内部的DDSIP核,同时根据IP核内部的相位累加 ...

- 1. FPGA内部的逻辑资源

CLB(包括LUT.加法器.寄存器.MUX(多路选择器)) 时钟网络资源(全局时钟网络,区域时钟网络,IO时钟网络),理解时钟网络的本质和意义 时钟处理单元(PLL,DCM),理解时钟网络资源和时钟处 ...

- FPGA内部RAM的初始化

Altera的RAM初始化文件格式是mif和hex. QuartusII自带的RAM初始化工具很方便产生初始化文件. Xilinx的RAM初始化文件格式是coe, 在vivado中软件会将coe文件变 ...

随机推荐

- python代码制作configure文件

在lua中,一直用lua作为config文件,或承载数据的文件 - 好处是lua本身就很好阅读,然后无需额外写解析的代码,还支持在configure文件中读环境变量,条件判断等. 在lua中通过loa ...

- [svc]ansible自动化模块

ansible命令执行模块 - command模块 [执行远程命令] $ ansible n1 -m command -a 'uname -n' - raw模块 [类似于command模块.支持管道传 ...

- Vue2 原理解析

现代主流框架均使用一种数据=>视图的方式,隐藏了繁琐的dom操作,采用了声明式编程(Declarative Programming)替代了过去的类jquery的命令式编程(Imperative ...

- Sql Server 2008 清除日志

--在SQL2008中清除日志就必须在简单模式下进行,等清除动作完毕再调回到完全模式. USE [master] GO ALTER DATABASE SSCDZ SET RECOVERY SIMPLE ...

- python将列表元素按指定数目分组

比如,有时候,我们需要将列表中的元素,按照每5个分组,分成好几个组时,可以采用下面的代码 a = [1,2,3,4,5,6,7,8,9,10,11] step = 5 b = [a[i:i+step] ...

- openfire 发送 接受 注册 广播 好友列表 在线状态

package cn.zsmy.utils.openfire; import java.io.BufferedReader; import java.io.InputStreamReader; imp ...

- Docker考前突击

dockerfile 介绍 镜像(Image) 容器(Container) 仓库(Repository)

- 基于jQuery左侧大图右侧小图切换代码

基于jQuery左侧大图右侧小图切换代码是一款带右侧缩略图选项卡的jQuery图片切换特效.效果图如下: 在线预览 源码下载 实现的代码. html代码: <div class=" ...

- 基于HTML5手机上下滑动翻页特效

基于HTML5手机上下滑动翻页特效.这是一款手机移动端触屏滑动翻页代码下载.效果图如下: 在线预览 源码下载 实现的代码. html代码: <section class="u-al ...

- Android基础——Fragment控制切换多个页面

今天接着上一篇文章,讲解一下Fragment的控制,主要是切换View和页面替换等操作.还有就是如何获取Fragment的管理对象,以及与Activity的通信方式. (PS:新建的QQ群,有兴趣可以 ...