modelsim-altera

一、

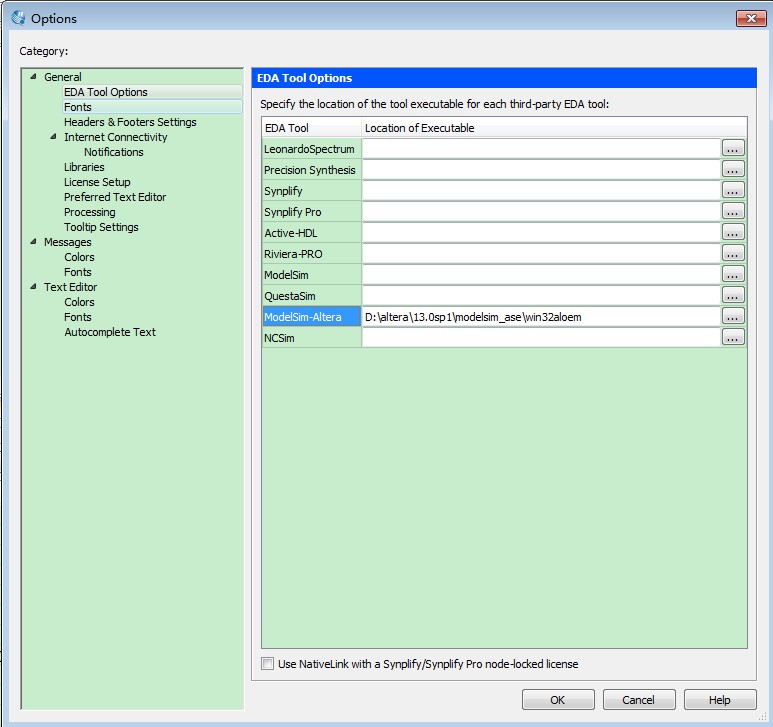

1. Go to the menu Tools > Options.

2. In the “General” category, select “EDA Tool Options”.

3. A dialogue box appears, where you can specify the location of the Modelsim-

Altera executable.

4. Specify the path to the directory with the executable of Modelsim-Altera.

5. Click “OK”.

二、新建一个quartus源文件、testbench文件

1、工程文件

module XGA

(

input clk,

input rst_n

);

reg [:] count ;

always @(posedge clk)

begin

if(!rst_n)

begin

count <= ;

end

else

begin

count <= count + ;

end

end

endmodule

程序

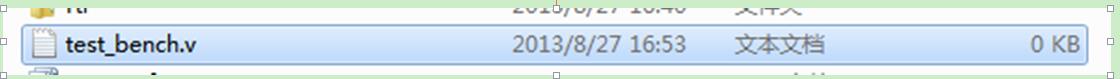

2、仿真测试文件

保存名为test_bench并将代码

module test_bench

(

output reg clk,

output reg rst_n

);

initial

begin

clk=;

rst_n=;

#

rst_n=;

end always

begin

# clk=~clk;

end XGA i1

(

.clk(clk),

.rst_n(rst_n)

); endmodule

bench

拷入其中

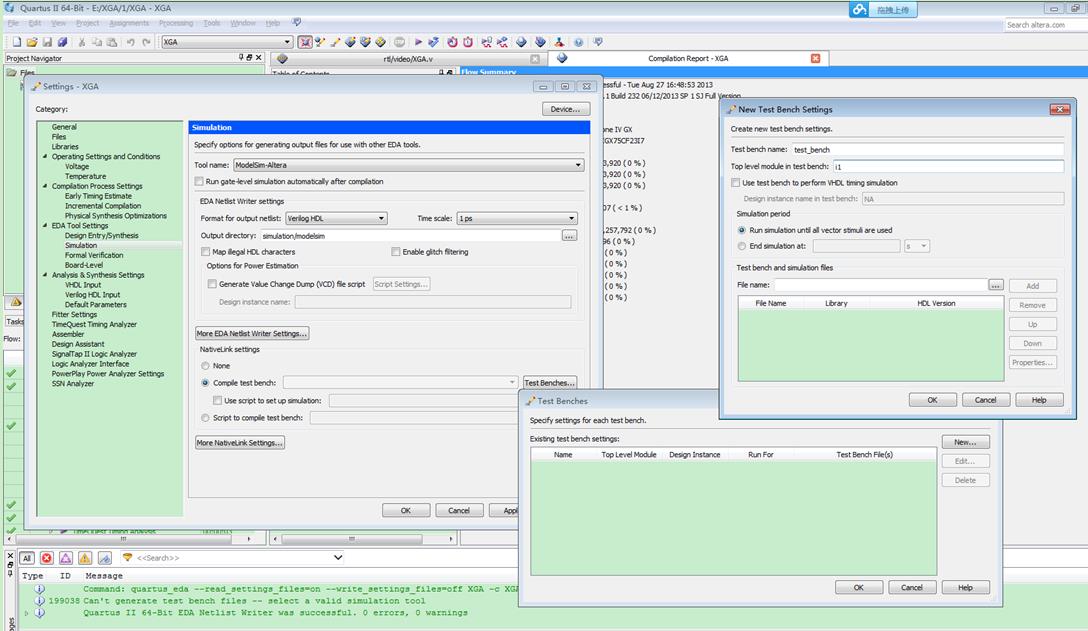

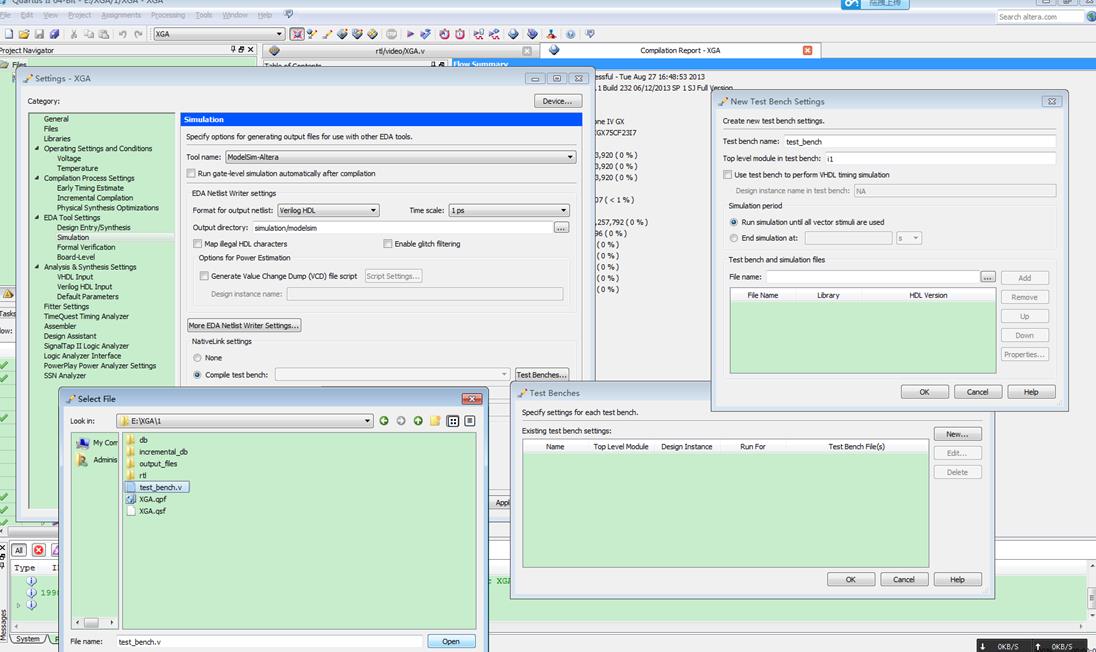

三、NativeLink Settings to configure Modelsim-Altera:

1. Go to the menu Assignments > Settings.

2. Under “EDA Tool Settings” choose “Simulation”.

simulation appears.

3. For Tool Name, choose “Modelsim-Altera”.

4. Select "verilog" as the "Format for Output Netlist"

5. Select "simulation/modelsim" as the "Output Directory".

6. Under NativeLink Settings, Choose "Compile test bench". Then click on "Test

Benches".

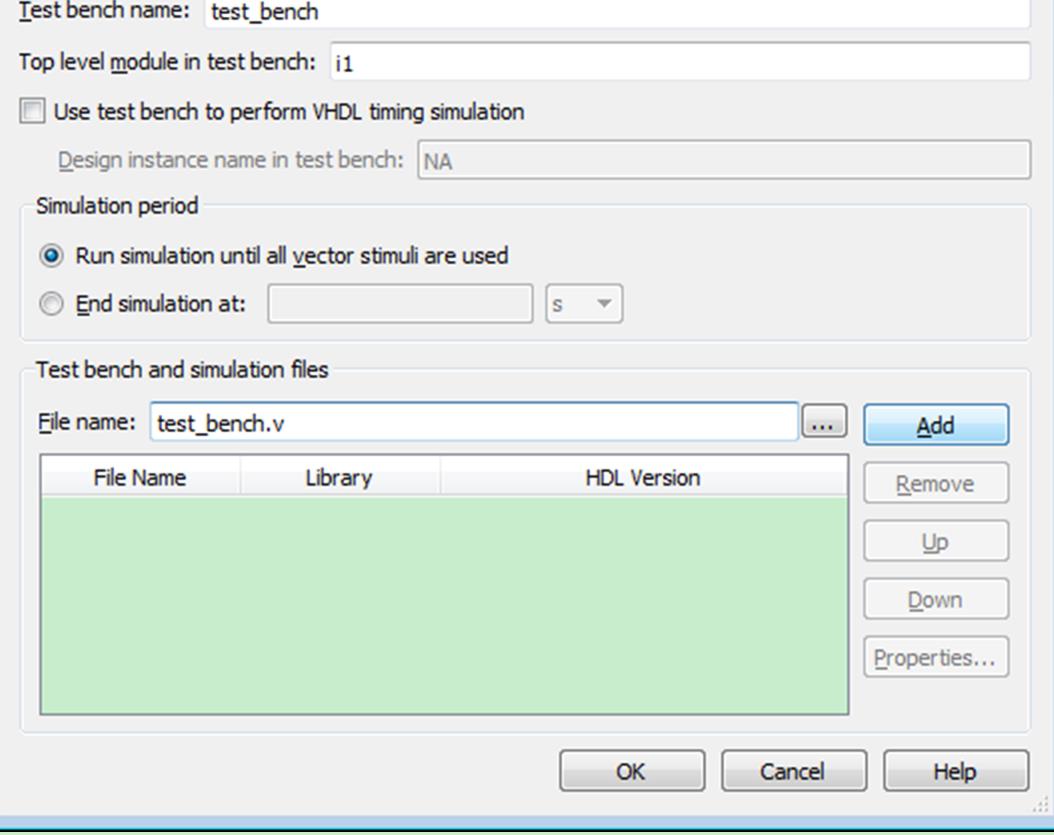

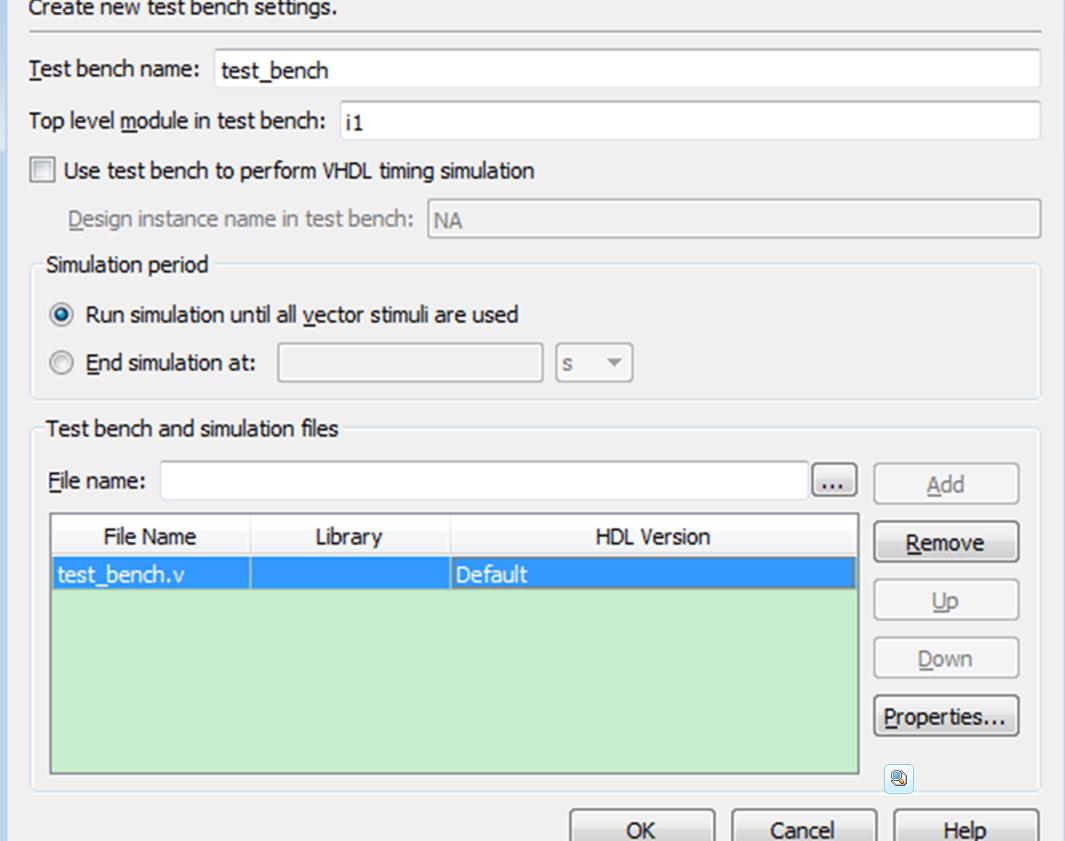

7. A new window appears, select "New".

选择文件

添加成功

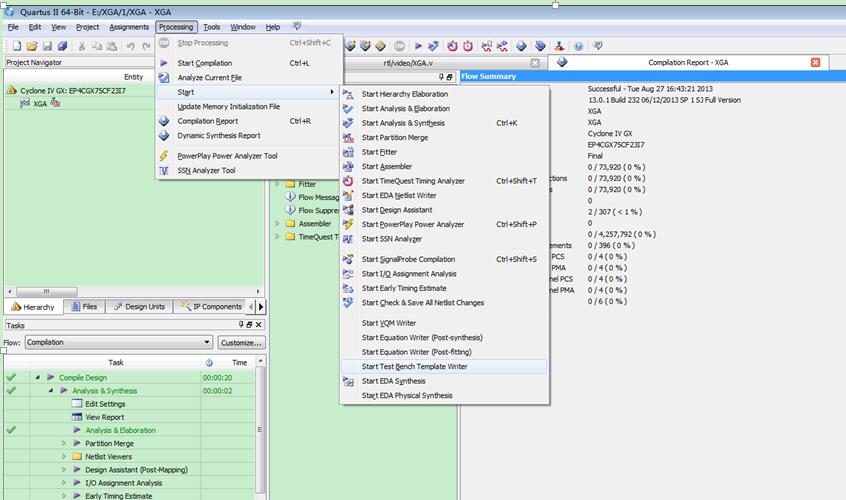

四、链接modelsim-altera

Using the menu “Tools”, click “Run EDA Simulation Tool”, and then click

EDA Gate-level Simulation to automatically run the EDA simulator, compile

all necessary design files, and complete a simulation.

运行仿真。Tools>Run EDA Simulation Tool

其中,RTL Simulation是寄存器传输级仿真,它是理想化的仿真,不包含任何延时信息,通常用作功能检验,也称作前仿真或功能仿真;

Gate-Level Simulation是门级仿真,通常也称为后仿真或时序仿真,它包含逻辑电路、布局布线等延时信息,是对真实电路情况的仿真。要仿真门级仿真,需要在Fitter之后进行。

modelsim-altera的更多相关文章

- Modelsim SE 仿真 ALTERA FPGA IP

Modelsim SE 仿真 ALTERA FPGA IP 最近,有几个朋友问过我是不是有新版本的Modelsim altera,其原因是 Qii 升级为新版本的,但是没配套的modelsim,没办法 ...

- Quartus调用Modelsim SE避免重复编译Altera器件库的方法

最近用Quartus 15.0配合Modelsim SE 10.4的64位版本,简直就是闪电一般的仿真速度.但是众所周知,SE版本最大的问题就是每次由Quartus自动调用时,都要重新编译所使用的器件 ...

- 用Modelsim仿真QuartusII综合后网表时库的添加方法(转)

这两天做综合后仿真,发现FPGA器件库又不会加了,无奈上网找方法.说起来不好意思,很早就接触Modelsim这个仿真软件了,可是没有好好琢磨.把这两天找的方法贴出来,再加上自己的理解,以后忘了可以上博 ...

- 【黑金原创教程】【Modelsim】【第二章】Modelsim就是电视机

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

- modelsim使用常见问题及解决办法集锦③

四.You selected Modelsim-Altera as Simulation Software in EDA Tool Settings,however…… You selected Mo ...

- ModelSim入门

verilog设计进阶 时间:2014年5月5日星期一 主要收获: 1. 安装了ModelSim ALTERA 6.4a; 2. 熟悉基本流程,仿真成功: 3. 了解testbench语法基本. 为什 ...

- EDA : quartus2 17.1lite + modelsim +verilog 使用流程

首先 然后填充好自己写的代码 之后save as 存到自己的文件夹 会自动弹出 配置 Assignments settings 之后第一次编译 成功后processing star ...

- Modelsim-altera 仿真 顶层原理图的解决办法

解决办法:首先需要将.bdf原理图文件转换为Verilog HDL等第三方EDA工具所支持的标准描述文件.在Quartus下,保持*.bdf为活动窗口状态,运行[File]/[Create/Updat ...

- verilog描述表决器的两种方式简易分析

命题:设计一个三变量表决器.真值表如下: 可以写出并简化得出公式:F=AB+BC+AC. 以下是两种算法: 第一种:仅从算法方面描述为:A.B.C的和大于1则输出结果为1,否则为0:源码如下: mod ...

- verilog阻塞与非阻塞的初步理解(一)

通过两个模块来区别两者.测试平台:Modelsim altera 6.5b 阻塞模块: module blocking(clk,a,b,c); :] a; input clk; :] b,c; :] ...

随机推荐

- RSTP介绍

1. 介绍 RSTP(Rapid Spanning Tree Protocol),快速生成树协议,标准为802.1w(已合入802.1D-2004)RSTP是对STP技术的修改和补充,最大特点就是快速 ...

- python脚本传递参数

给python程序传递参数 运行python脚本时有时需要执行实传递参数 在linux下: [root@Test ~]# cat /opt/python.py #!/usr/local/bin/pyt ...

- IDEA 2017.3 新版本中创建 JSF Web 应用程序缺少 web.xml 的解决办法

IDEA 2017.3 新版本中默认创建一个 Web 应用程序很可能不会自动创建 web.xml 文件.虽然说从 JavaEE 6.0 开始 Servlet 3.0 规范中就新增了一些注解可以免去传统 ...

- hdu 2582(数论相关定理+素数筛选+整数分解)

f(n) Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others)Total Submis ...

- nodejs编写实例基础操作

学习视频地址 https://cnodejs.org/topic/5a72c66ace45d440451465c3 初始化项目 首先查看项目中是否有package.json 文件,如果有可执行np ...

- 几个相似的DP题

HDU1398 题意:把一个整数分拆成1.4.9.16.…….256.289(注意:只到289)这17个完全平方数的和,有几种方法. 解法不用说自然是DP,因为搜索显然超时. (这样的题我一般不敢开i ...

- Java NIO.2 使用Files类遍历文件夹

在以前的Java版本中,如果要遍历某个文件夹下所有的子文件.子文件夹,需要我们自己写递归,很麻烦. 在Java7以后,我们可以NIO.2中的Files工具类来遍历某个文件夹(会自动递归). 大致用法: ...

- 比JSONKit还要快的第三方JSON解析器NextiveJson

这款比JSONKit还好用,效率跟iOS5原生的差不多,不过解析后对内存的释放比原生的要多.所以推荐 https://github.com/nextive/NextiveJson 顺便提一下解析XML ...

- iOS博客列表

国外 iOSDevWeekly NSHipster NSBlog objcio Raywenderlich Bignerdranch NSScreencast 需FQ Pilky.me jeremyw ...

- XCode设置竖屏

选中你的项目,在General这个标签内,Deoployment info的这个分组,有一个Device Orientation 标签,内有一个Portrait的选项,选中是竖屏,取消选中是横屏