FPGA学习笔记(一)——初识FPGA

###### 【该随笔部分内容转载自小梅哥】 #########

FPGA(Field-Programmable Gate Array,现场可编程门阵列),正如其名,FPGA内部有大量的可编程逻辑功能块,使用verilog HDL(硬件描述语言)实现设计。

玩过单片机的小伙伴刚接触FPGA可能会有点困惑,其实FPGA与单片机最大的区别就在于:FPGA设计的是电路,单片机设计的是程序。单片机只有一个CPU在工作时钟的驱动下顺序的执行程序(取指、译码、执行),所以工作速度较慢,而FPGA设计出来的是整个电路逻辑系统,根本不需要单片机这么复杂,所以FPGA的工作速度自然很快,在两者各有各的优势下,单片机主要用于进行相关控制,FPGA多用于信号处理相关。

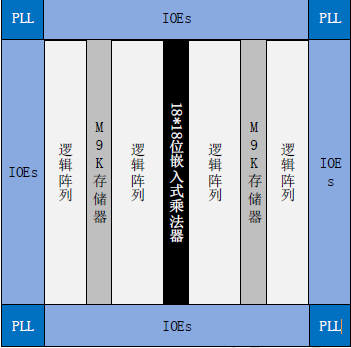

典型的FPGA原理和结构如下图(注:以Cyclone IV E FPGA芯片为例),主要包括三类基本资源:

- 可编程逻辑功能块(Altera-LE(Logic Element) / Xlinx-Slice)

- 可编程内部互连资源

包括各种长度的连线线段和一些可编程连接开关,它们将各个可编程逻辑块或输入/输出块连接起来,构成特定功能的电路。用户可以通过编程决定每个单元的功能以及它们的互连关系,从而实现所需的逻辑功能。

- 可编程输入/输出(I/O)块

完成芯片内部逻辑与外部管脚之间的接口,围绕在逻辑单元阵列四周;

FPGA从简单的逻辑粘合,发展到现在的可编程片上系统,FPGA厂家也在基本的FPGA架构上加入了一些扩展资源,比如时钟管理单元(PLL、DLL)、嵌入式存储器单元和硬件乘法器单元,DSP单元一些高端器件还加入了高速收发器、甚至嵌入式硬核处理器,让FPGA的应用领域更广阔,Cyclone IV E器件加入的扩展资源有:

- PLL锁相环

模拟电路,将输入的周期信号进行分频和倍频,或改变相位,输出一个或多个稳定的时钟信号;

- M9K存储器

嵌入式块RAM,容量大小9Kbit,这些存储器可以被配置成单端口、简单双端口、真双端口RAM、FIFO缓冲器、ROM

- 18*18硬件乘法器

快速进行运算

FPGA中除了三类基本资源和一些扩展资源外,由图中可以看到,FPGA中资源分布也是很精致的:

1、逻辑阵列和M9K存储器交替分布,这样做的优点是缩短数据的传输路径,以获得更优的时序性能;

2、IOEs和PLL单元分布在器件的四周,数据流一般从左侧IO流入,经过处理、运算、存储,通过右侧IO流出,控制信号通过上下IO输入输出;有时候系统需要高质量时钟(比如软核所需工作时钟)通常由PLL单元产生,而这些分布在四周的PLL可以最短时钟源产生工作时钟,另外,PLL属于模拟电路,放在周围更利于和生产;

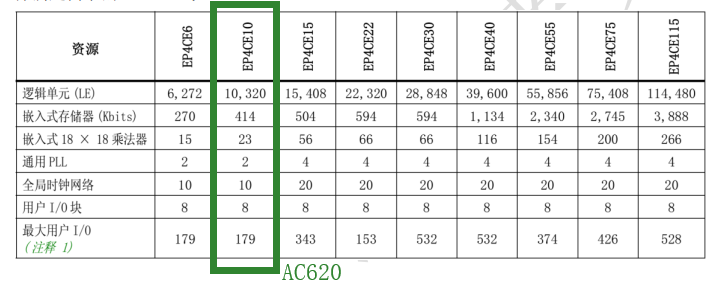

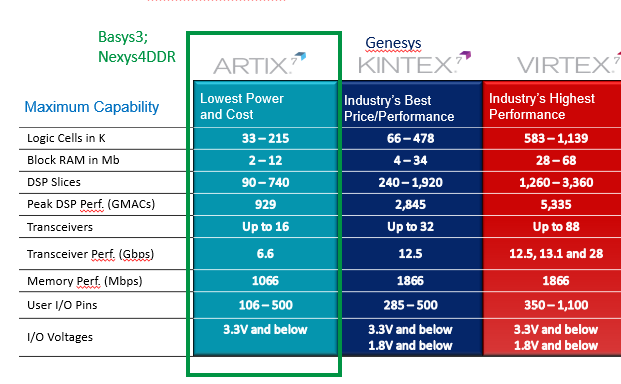

下面具体了解下两种主流FPGA的资源情况:

Altera Cyclone IV E系列FPGA常见硬件资源详情列表:

Xilinx 7 系列FPGA 硬件资源详情:

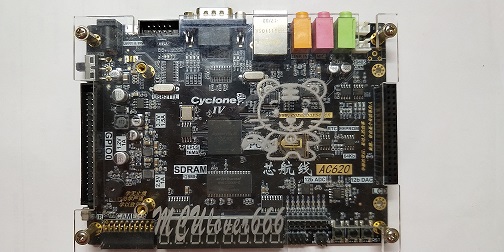

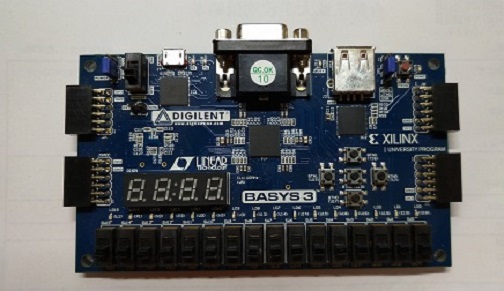

最后,放上两张开发板图片,一块是小梅哥基于Cyclone IV EP4CE10的AC620,一块是Digilent基于Xilinx Artix7的Basys3,两块都很精致有木有~

FPGA学习笔记(一)——初识FPGA的更多相关文章

- FPGA学习笔记之Altera FPGA使用JIC文件配置固化教程(转)

很多做过单片机的朋友都知 道,我们在对MCU烧写完程序固件后,那么该程序固件就存储在了该MCU内部.即使MCU断电了再重新上电,程序也能继续运行.这是因为对MCU烧写固件 的实质就是将程序固件写入到M ...

- Storm学习笔记 - Storm初识

Storm学习笔记 - Storm初识 1. Strom是什么? Storm是一个开源免费的分布式计算框架,可以实时处理大量的数据流. 2. Storm的特点 高性能,低延迟. 分布式:可解决数据量大 ...

- LevelDB学习笔记 (1):初识LevelDB

LevelDB学习笔记 (1):初识LevelDB 1. 写在前面 1.1 什么是levelDB LevelDB就是一个由Google开源的高效的单机Key/Value存储系统,该存储系统提供了Key ...

- FPGA学习笔记(二)——FPGA学习路线及开发流程

###### [该随笔部分内容转载自小梅哥] ######### 一.FPGA学习路线 工具使用 -> 语法学习 -> 逻辑设计 -> IP使用 ->接口设计 -& ...

- Java学习笔记心得——初识Java

初识Java 拿到这本厚厚的<Java学习笔记>,翻开目录:Java平台概论.从JDK到TDE.认识对象.封装.继承与多态...看着这些似懂非懂的术语名词,心里怀着些好奇与担忧,就这样我开 ...

- FPGA学习笔记(三)—— 数字逻辑设计基础(抽象的艺术)

FPGA设计的是数字逻辑,在开始用HDL设计之前,需要先了解一下基本的数字逻辑设计-- 一门抽象的艺术. 现实世界是一个模拟的世界,有很多模拟量,比如温度,声音······都是模拟信号,通过对模拟信号 ...

- FPGA学习笔记(七)——FSM(Finite State Machine,有限状态机)设计

FPGA设计中,最重要的设计思想就是状态机的设计思想!状态机的本质就是对具有逻辑顺序和时序规律的事件的一种描述方法,它有三个要素:状态.输入.输出:状态也叫做状态变量(比如可以用电机的不同转速作为状态 ...

- Xilinx FPGA 学习笔记

一.时序设计 方法1.通过状态机来实现,通过verilog控制FPGA,让它该快的时候快,该慢的时候慢. 方法2.FPGA中运行CPU 把逻辑控制顺序复杂的事情用C代码来实现,而实时处理部分用veri ...

- FPGA学习笔记(八)—— 状态机设计实例之独立按键消抖

###### [该随笔中部分内容转载自小梅哥] ######### 独立按键消抖自古以来在单片机和FPGA中都是个不可避免的问题,首先,解释一下什么叫做按键抖动,如图,按键在按下和松开的那个瞬间存在大 ...

随机推荐

- 实战项目开发细节:C语言分离一个16进制数取出相应的位1或0

最近在公司开发一个关于钢琴的PCBA项目,项目大概是这样的,完成各种功能的测试,准备去工厂量产的时候可以通过软件快速甄别硬件是否短路,断路等问题. 其中,甄别好坏的方法是通过比如按键,或者其它的操作然 ...

- mac os X中关于dayone缓存的实际文件位置

最近刚安装了mac版的dayone软件,感觉蛮不错的!以前一直用iphone版的,mac版是要米的,68米丫!想了想还是一咬牙:买了! 我用的是iCloud同步,虽然资料放在云中,但本地还是会有缓存的 ...

- pyqt5 动画在QThread线程中无法运行问题

自己做了一个tcp工具,在学习动画的时候踩了坑,需求是根据上线变绿色,离线变灰色,如果连接断开了,则变为灰色 问题现象: 可以看到点击"连接","离线"的时候动 ...

- 自定义UICollectionViewLayout 布局实现瀑布流

自定义 UICollectionViewLayout 布局,实现瀑布流:UICollectionView和UICollectionViewCell 另行创建,这只是布局文件, 外界控制器只要遵守协议并 ...

- Spring Aop中,获取被代理类的工具

在实际应用中,顺着过去就是一个类被代理.反过来,可能需要逆向进行,拿到被代理的类,实际工作中碰到了,就拿出来分享下. /** * 获取被代理类的Object * @author Monkey */ p ...

- Http持久连接与HttpClient连接池

一.背景 HTTP协议是无状态的协议,即每一次请求都是互相独立的.因此它的最初实现是,每一个http请求都会打开一个tcp socket连接,当交互完毕后会关闭这个连接. HTTP协议是全双工的协议, ...

- 实例解析Collections源码,Iterator和ListIterator

比如一个视频或文章有多个页面标签设置,我们在看一篇文章或一个视频时,底部有为你推荐栏目. 如何根据这个文章或视频的标签,来实现这个推荐栏目呢. public List<VideoInfoVo&g ...

- SAE提供服务分析

这个分析列表主要关注两个问题,服务能做什么,移植实现难度. AppConfig: 这个东西主要面向SAE本身的一些配置选项,移植时放弃这个东西,所以就不谈难度了Counter :这个东西提供某个操作的 ...

- Google搜索排名优化-面向搜索引擎的网站设计

内容摘要:网站在搜索营销方面最主要的缺点: 行业知识:不知道搜索引擎对吸引的新用户的重要性,在搜索引擎排名服务中追求“傻瓜相关”,购买一些其实没有太多实际意义的行业关键词.其实能够用户输入的关键词越多 ...

- R语言学习 第十篇:操作符

运算符是R语言中最基础的存在,熟悉运算符的使用,是熟练使用R处理数据的基础,操作符,顾名思义,是对数据进行运算的符号,R有自己的一套操作符,实现变量的赋值,引用,运算等功能. 一,赋值符号 为变量赋值 ...