VGA设计(原理说明。Verilog代码实现,仿真结果)

各类显示屏的显示原理大部分是利用人眼的视觉暂留效应。比如之前的数码管显示就是设计每个周期内各个小段按顺序显示,来达到显示一个数字的效果。

VGA同理,显示屏在显示时是一个像素一个像素地显示,在人眼看来所有像素是同时显示的,便构成了一幅图片。

①显示器的分辨率越高(如4k屏:3840*2160),显示的图像越清晰。

②显示器的刷新率(即每秒能够显示几幅图片)越高,显示器越不卡,性能更好。(一个周期内,每个像素点显示的时间长度和显示屏的分辨率以及驱动电路的系统时钟频率决定了显示屏的刷新率。

系统时钟频率越高,显示屏的刷新率越高。)

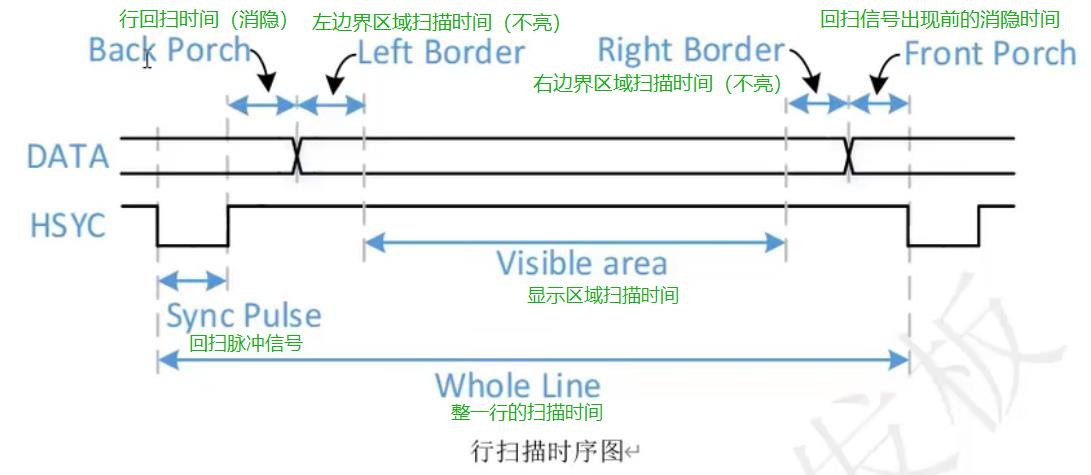

显示器的显示原理:逐个像素点输出RGB值,通过设计时序可以达到这个目的。通过行扫描+列扫描达到显示所有像素点的目的。

VGA是一种显示标准,VGA接口即电脑采用VGA标准输出数据的专用接口。

VGA接口共有15针,分成3排,每排5个孔,显卡上应用最为广泛的接口类型,绝大多数显卡都带有此种接口。它传输红、绿、蓝模拟信号[23:0]RGB_data以及同步信号(水平和垂直信号)(horizontal_sig和vertical_sig)。

设计过程:利用计数器来输出每一个像素以及输出同步信号。

案例:

要求:640*480的显示屏

代码:

module VGA(

clk,

reset,

content_data_request,//数据请求信号

horizontal_sig,//horizontal 水平的

vertical_sig, //vertical 垂直的

content_data,//要显示的内容数据

RGB_data,//输出的内容数据

vis_sig//内容显示同步信号(高电平时显示)

);

input clk ;

input reset ;

output reg content_data_request ;//数据请求信号

output reg horizontal_sig ;

output reg vertical_sig ;

input [23:0]content_data ;

output reg [23:0]RGB_data ;

output reg vis_sig ;//内容显示同步信号

reg h_vis_sig ;//行内容显示同步信号

reg v_vis_sig ;//列内容显示同步信号 //定义时间节点参数

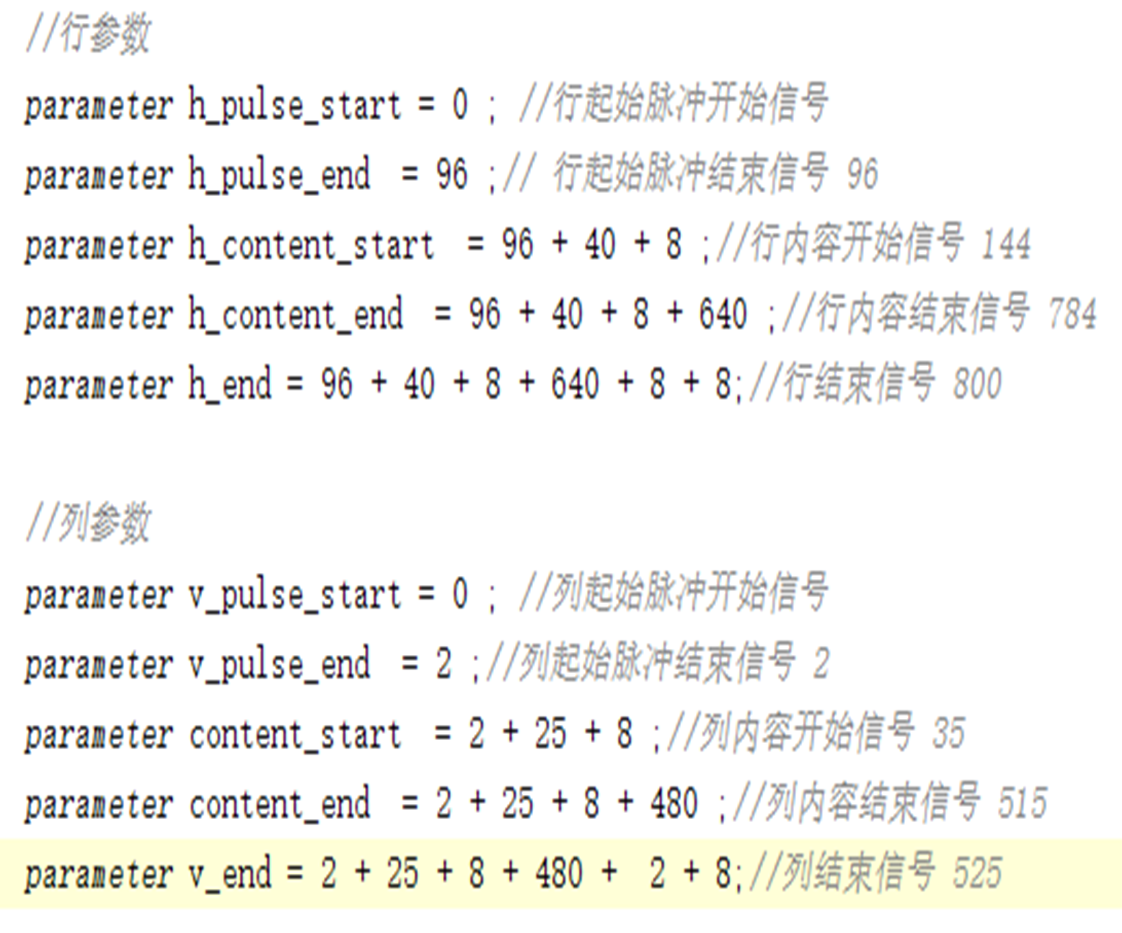

//行参数

parameter h_pulse_start = 0 ; //行起始脉冲开始信号

parameter h_pulse_end = 96 ;// 行起始脉冲结束信号 96

parameter h_content_start = 96 + 40 + 8 ;//行内容开始信号 144

parameter h_content_end = 96 + 40 + 8 + 640 ;//行内容结束信号 784

parameter h_end = 96 + 40 + 8 + 640 + 8 + 8;//行结束信号 800 //列参数

parameter v_pulse_start = 0 ; //列起始脉冲开始信号

parameter v_pulse_end = 2 ;//列起始脉冲结束信号 2

parameter content_start = 2 + 25 + 8 ;//列内容开始信号 35

parameter content_end = 2 + 25 + 8 + 480 ;//列内容结束信号 515

parameter v_end = 2 + 25 + 8 + 480 + 2 + 8;//列结束信号 525 //行与列 计数器

reg [9:0]h_cnt ;

reg [9:0]v_cnt ; always@(posedge clk or negedge reset)//行计数

if(!reset)

h_cnt <= 0 ;

else if ( h_end - 1 <= h_cnt )//0-799

h_cnt <= 0 ;

else

h_cnt <= h_cnt + 1 ; always@(posedge clk or negedge reset)//列计数

if(!reset)

v_cnt <= 0 ;

else if (( v_end - 1 <= v_cnt ) && ( h_end - 1 <= h_cnt ))//0-524

v_cnt <= 0 ;

else if (( h_end - 1 <= h_cnt ) && ( v_end - 1 > v_cnt ))

v_cnt <= v_cnt + 1 ; //产生行起始脉冲

always@(posedge clk or negedge reset)//

if(!reset)

horizontal_sig <= 1 ;

else if( h_cnt == 0 )

horizontal_sig <= 0 ;//1-96 共96

else if ( h_cnt == 96 )

horizontal_sig <= 1 ; //产生列起始脉冲

always@(posedge clk or negedge reset)//

if(!reset)

vertical_sig <= 1 ;

else if(( v_cnt == 0 )&& ( h_end - 1 <= h_cnt ) )

vertical_sig <= 0 ;//1-2 共2

else if (( v_cnt == 2 )&& ( h_end - 1 <= h_cnt ) )

vertical_sig <= 1 ; //产生行显示同步信号

always@(posedge clk or negedge reset)//

if(!reset)

h_vis_sig <= 0 ;

else if (( 144 - 2 <= h_cnt ) && ( 784 - 1 - 2 >= h_cnt )) //提前两拍保证输出在第145拍开始

h_vis_sig <= 1 ;//146 - 785共

else

h_vis_sig <= 0 ; //产生列显示同步信号

always@(posedge clk or negedge reset)//

if(!reset)

v_vis_sig <= 0 ;

else if (( 35 <= v_cnt ) && ( 515 >= v_cnt ) && ( ( h_end - 1 <= h_cnt ) ) )

v_vis_sig <= 1 ;

else if (( 35 > v_cnt ) || ( 515 < v_cnt ) )

v_vis_sig <= 0 ; //请求信号

always@(posedge clk or negedge reset)

if(!reset)

content_data_request <= 0 ;//

else if ( ( v_vis_sig ) && ( h_vis_sig ) )

content_data_request <= 1 ;

else

content_data_request <= 0 ; //显示同步信号

always@(posedge clk or negedge reset)//

if(!reset)

vis_sig <= 0 ;

else if ( content_data_request )

vis_sig <= 1 ;

else

vis_sig <= 0 ; //显示

always@(posedge clk or negedge reset)//

if(!reset)

RGB_data <= 0 ;

else if ( content_data_request )

RGB_data <= content_data ;

else

RGB_data <= 0 ; endmodule

`timescale 1ns / 1ns

module VGB_tb( ); reg clk ;

reg reset ;

wire horizontal_sig ;

wire vertical_sig ;

reg [23:0]content_data ;

wire [23:0]RGB_data ;

wire content_data_request ;//数据请求信号 ;

wire vis_sig ; VGA VGA_sim(

clk,

reset,

content_data_request,//数据请求信号

horizontal_sig,//horizontal 水平的

vertical_sig, //vertical 垂直的

content_data,//要显示的内容数据

RGB_data,//输出的内容数据

vis_sig //内容显示同步信号

); initial clk = 1 ;

always #20 clk = ! clk ;//25MHz

initial begin

reset = 0 ;

content_data = 0 ;

#201

reset = 1 ;

#70000000;

$stop;

end always@(posedge clk or negedge reset)//

if(!reset)

content_data <= 0 ;

else if (content_data_request )

content_data <= content_data + 1 ; endmodule

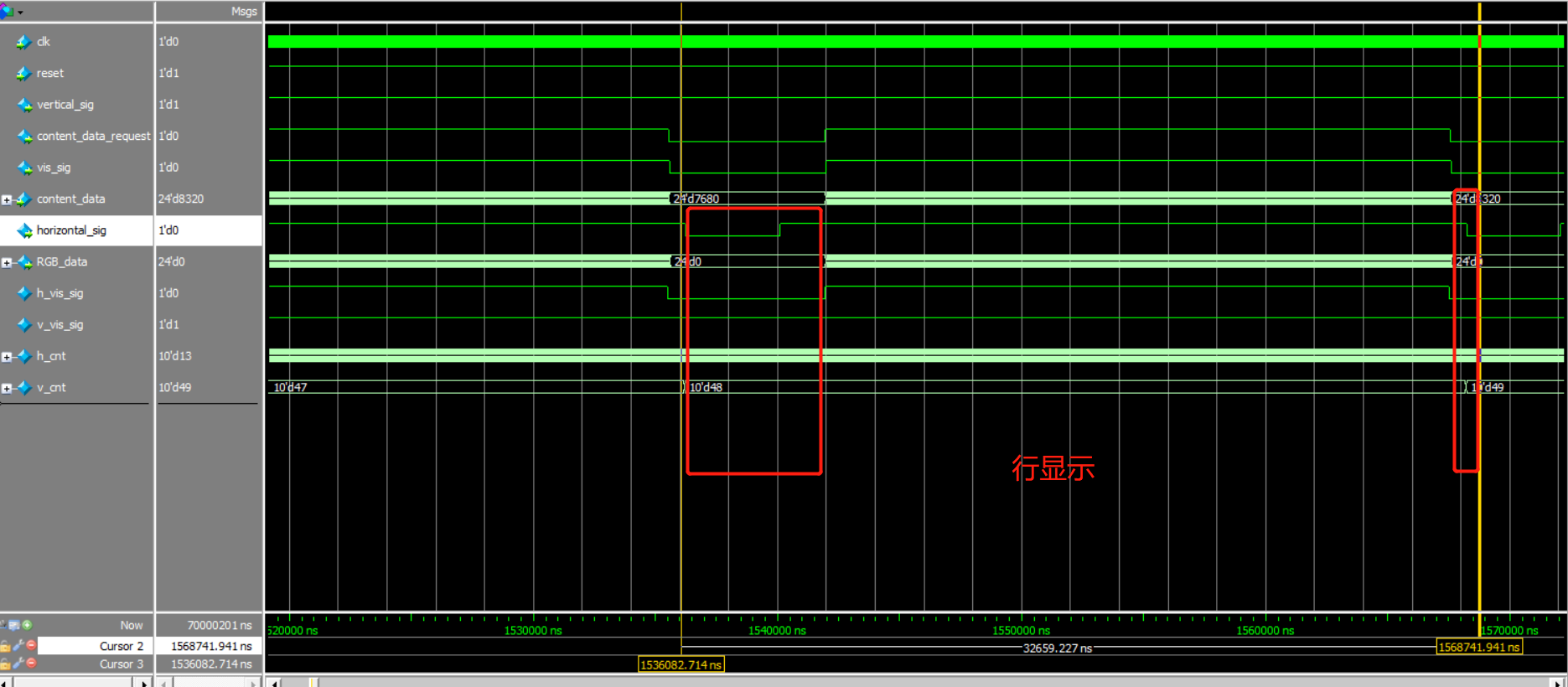

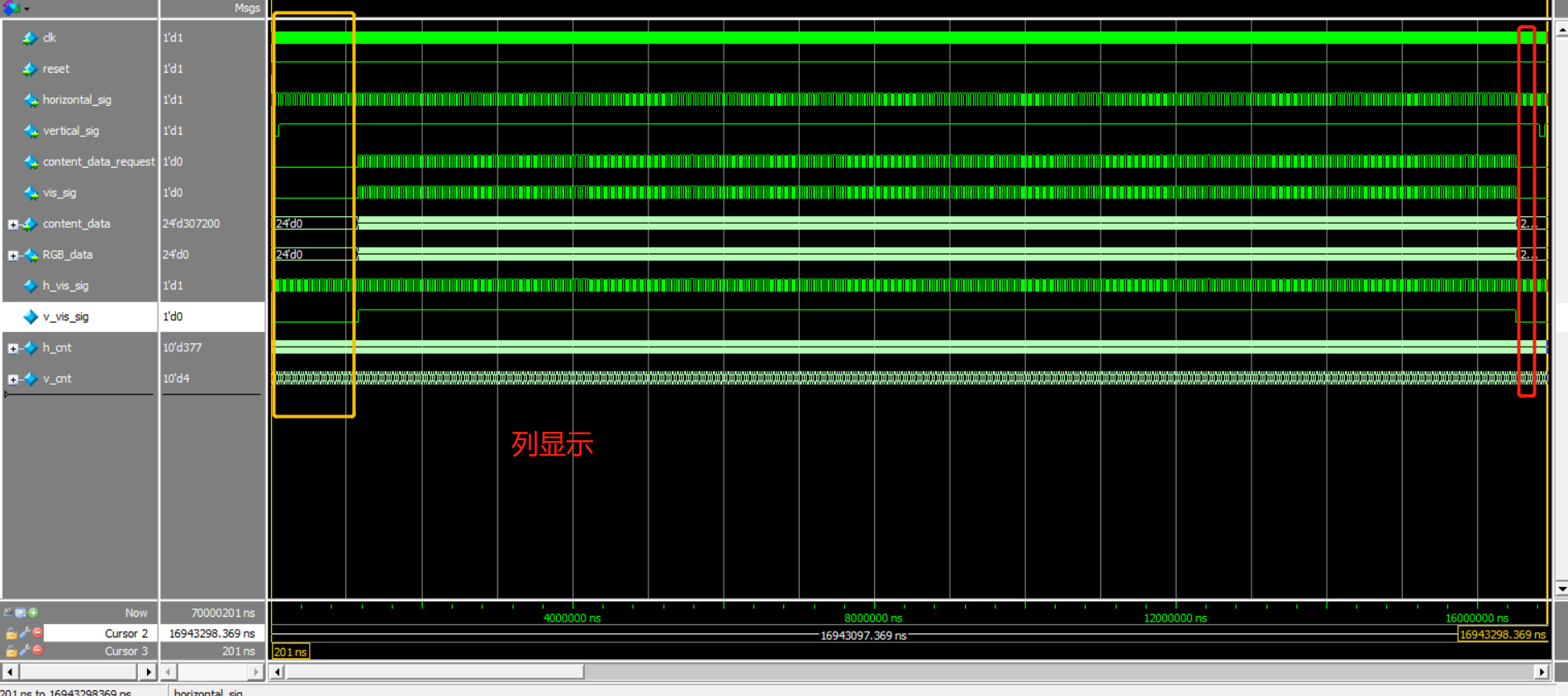

结果:

需要验证的点:同步信号的长度,脉冲信号的长度,显示行的时间长度,显示列的长度。(通过观察行计数器h_cnt和列计数器v_cnt即可)

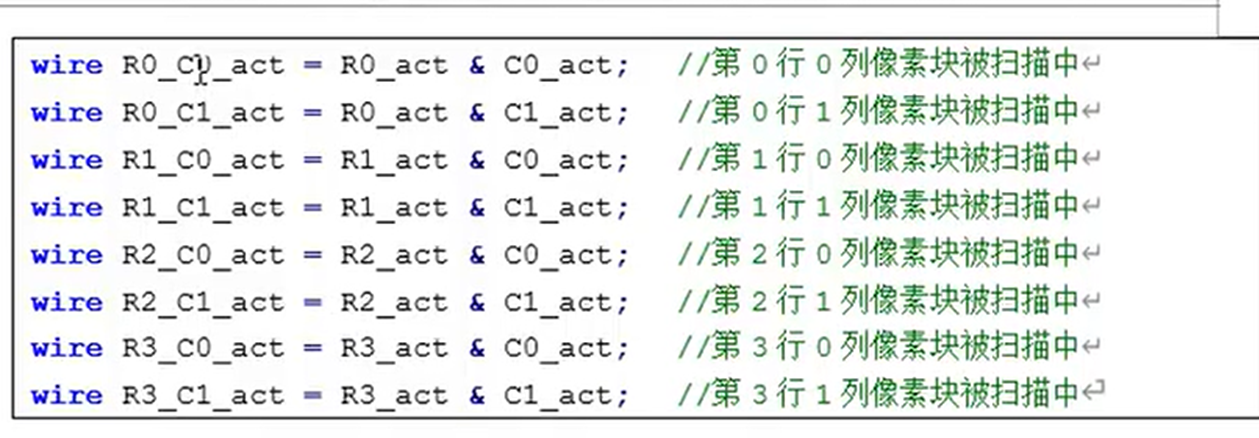

新功能:显示特定区域。

实现:设定参数来界定区域。

VGA设计(原理说明。Verilog代码实现,仿真结果)的更多相关文章

- 【接口时序】7、VGA接口原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 寄存器,移位寄存器的电路原理以及verilog代码实现

寄存器:用以存放二进制代码的电路,下图为由维特阻塞D触发器组成的4位数码寄存器: 逻辑功能分析: 1.异步端CR置0时,输出置0: 2.同步并行置数:D0~D3为4个输入代码,当CP上升沿到达时,D0 ...

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- 【接口时序】6、IIC总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE .ChipScope 硬件平台: 1. FPG ...

- 【接口时序】4、SPI总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 【接口时序】3、UART串口收发的原理与Verilog实现

一.软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1.FPGA型号:XC6SLX45- ...

- SPI总线的原理与Verilog实现

转载地址:https://www.cnblogs.com/liujinggang/p/9609739.html 一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件 ...

- verilog 代码分析与仿真

verilog 代码分析与仿真 注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值 边沿检测 module signal_test( input wire cmos_pcl ...

- VCS使用学习笔记(1)——Verilog相关的仿真知识

本文主要学习Verilog的仿真特性,以及仿真器对Verilog的处理,算是对Verilog知识的增量学习.本文内容与我的另一篇博文(http://www.cnblogs.com/IClearner/ ...

- html5设计原理(转)

转自: http://www.cn-cuckoo.com/2010/10/21/the-design-of-html5-2151.html 今天我想跟大家谈一谈HTML5的设计.主要分两个方面:一 ...

随机推荐

- 团队Arpha6

队名:观光队 链接 组长博客 作业博客 组员实践情况 黄恒杰 - **过去两天完成了哪些任务 ** - 文字/口头描述 地图功能增加.博客 - 展示GitHub当日代码/文档签入记录 - 接下来的计划 ...

- 干货 | Keepalived高可用服务配置实例

一个执着于技术的公众号 Keepalived系列导读 Keepalived入门学习 keepalived安装及配置文件详解 前言 在前面的章节中,我们学习了Keepalived简介.原理.以及Keep ...

- mybatis两种嵌套查询方式

1,推荐用第一种 <select id="getTeacher2" resultMap="TeacherStudent"> select s.id ...

- 3D离线地图开发

3D离线地图介绍(3D离线采用矢量数据作为地图基础,可保持地图数据最新) 一.开发中引用3D离线地图(可独立部署通过内外IP+端口进行访问,也可拷贝js库文件到项目中通过绝对路径访问) 1).离线AP ...

- 我使用Spring AOP实现了用户操作日志功能

我使用Spring AOP实现了用户操作日志功能 今天答辩完了,复盘了一下系统,发现还是有一些东西值得拿出来和大家分享一下. 需求分析 系统需要对用户的操作进行记录,方便未来溯源 首先想到的就是在每个 ...

- flex布局的总结

1.开启了flex布局的元素叫: flex container 2.里面的直接子元素叫:flex items(默认情况下,所有item都会在一行显示) 3.display属性由flex和inline- ...

- vs2022+resharper创建模板——实现在新建文件的时候自动生成防卫式声明和自定义语句

在网上找了很久如何让visual studio新建文件的时候自动生成注释和防卫式声明,虽然防卫式声明可以用#proga once替代,但是在clion里可以自动生成vs里面没法自动生成还是觉得难受,于 ...

- np.linspace,numpy中的linspace()

import numpy as np x=np.linspace(1,10) y=np.linspace(1,10,num=10,retstep=True)#num可省略 print(x) print ...

- C语言 - 基础数据结构和算法 - 企业链表

听黑马程序员教程<基础数据结构和算法 (C版本)>,照着老师所讲抄的, 视频地址https://www.bilibili.com/video/BV1vE411f7Jh?p=1 喜欢的朋友可 ...

- Camunda开源流程引擎快速入门——Hello World

市场上比较有名的开源流程引擎有osworkflow.jbpm.activiti.flowable.camunda.由于jbpm.activiti.flowable这几个流程引擎出现的比较早,国内人用的 ...