使用verilog编写锁存器与触发器

需要注意的地方有四点:

1、关于锁存器与触发器在原理上的不同点,以及代码的不同点

2、关于高电平有效与低电平有效之前的区别

3、理解实现复位与实现D触发器之间的区别

4、理解同步与异步之间的区别

锁存器代码编写

|

Module D_latch(d,clk,q); Input d; Input lck; Output reg q; always@(clk or d) if(clk) q<=d; endmodule |

D触发器,标准

|

Module D_ff(d,clk,q); Input d; Input lck; Output reg q; always@( posedge clk) q<=d; endmodule |

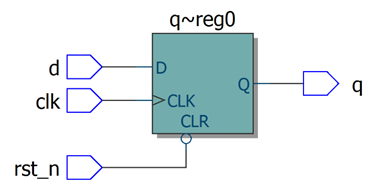

异步低有效D触发器

注意高电平有效跟低电平有效之间的区别

|

module code(clk,rst_n,d,q); input clk; input rst_n; input d; output reg q; always @( posedge clk or negedge rst_n) begin if(!rst_n) q <= 1'b0; else q <= d; end endmodule |

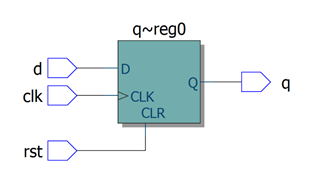

异步高有效D触发器

|

module code(clk,rst,d,q); //关于高有效还是低有效,都是驱动clk对输出端进行使能,有效 即为输 出为0,并不是输出要等于复位信号的值。 input clk; input rst; input d; output reg q; always @( posedge clk or posedge rst ) //注意这里是两个上升沿,高电平有效 begin if(rst) q <= 1'b0; else q <= d; end endmodule |

同步高有效D触发器

也就是说同步复位触发器时,必须使用触发器之外的门逻辑,才能构成同步触发器。

|

module code(clk,rst,d,q); input clk; input rst; input d; output reg q; always @( posedge clk) begin if(rst) q <= 1'b0; else q <= d; end endmodule |

使用verilog编写锁存器与触发器的更多相关文章

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- Verilog 编写规范

在学习Python时,作者有一句话对我影响很大.作者希望我们在学习编写程序的时候注意一些业内约定的规范.在内行人眼中,你的编写格式,就已经暴露了你的程度.学习verilog也是一样的道理,一段好的ve ...

- FPGA基础之锁存器与触发器的设计

转载:https://blog.csdn.net/lg2lh/article/details/39081061 一.锁存器 首先设计锁存器的时候应该清楚什么是锁存器,锁存器其实是对电平信号敏感的,一定 ...

- 【从零开始自制CPU之学习篇03】锁存器与触发器

本篇学习了两种锁存器:SR Latch和D Latch,一种触发器:D flip flop SR Latch:SR—锁存器 初始状态下,S和R都为0,Q和Q‘随机有一个为1另一个 为0(取决于电流速度 ...

- 关于verilog中if与case语句不完整产生锁存器的问题 分类: FPGA 2014-11-08 17:39 260人阅读 评论(0) 收藏

在很多地方都能看到,verilog中if与case语句必须完整,即if要加上else,case后要加上default语句,以防止锁存器的发生,接下来就来说说其中原因. 一,什么是锁存器?锁存器与触发器 ...

- 锁存器 Latch v.s. 触发器 Flip-Flop

转载 http://guqian110.github.io/pages/2014/09/23/latch_versus_flip_flop.html 根据 Wiki: Flip-flop (elec ...

- [FPGA]Verilog实现JK触发器组成的8421BCD码十进制计数器

目录 概述 电路分析 代码实现 参考文献 概述 本文以异步时序计数器为例,用Verilog实现以\(JK\)触发器组成的8421BCD码十进制异步计数器,并用ModelSim软件进行仿真验证. 电路分 ...

- 对Verilog 初学者比较有用的整理(转自它处)

*作者: Ian11122840 时间: 2010-9-27 09:04 ...

- 【接口时序】5、QSPI Flash的原理与QSPI时序的Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 4.Matlab版本:Matlab2014b/ ...

随机推荐

- Zookeeper_ACL

getAcl path 查看某个node的权限 设置权限1 world方式 setAcl <path> world:anyone:<acl>例如 setAcl /node1 w ...

- 【React】react学习笔记03-React组件对象的三大属性-state

今天晚上学习了React中state的使用,特做此记录,对于学习的方式,博主仍然推荐直接复制完整代码,对着注释观察现象!: 上文中,我列举了两种React自定义组件的声明,这里我拿方式二进行举例: / ...

- ph模拟登录获取信息

cURL 是一个功能强大的PHP库,使用PHP的cURL库可以简单和有效地抓取网页并采集内容,设置cookie完成模拟登录网页,curl提供了丰富的函数,开发者可以从PHP手册中获取更多关于cURL信 ...

- c++ 归并排序

c++ 归并排序 输入输出格式 输入格式: 第11行为一个正整数NN,第22行包含NN个空格隔开的正整数a_ia i ,为你需要进行排序的数,数据保证了A_iA i 不超过1000000000 ...

- Spring Cloud Alibaba | Nacos服务中心初探

目录 Spring Cloud Alibaba | Nacos服务中心初探 1. 什么是Nacos? 1.1 Nacos 1.0 1.2 Nacos 2.0 2. Nacos 架构及概念 2.1 服务 ...

- Q&A-20180128

Orleans与Akka对比,为什么选用Orleans? 答: Akka对参与开发的人员要求更高一些,普遍是专家级别,Orleans框架进一步抽象了一层,结合C#语言特性,能普遍降低开发难度. 下面是 ...

- I/O:Writer

Writer: Writer append(char c) :将指定字符添加到此 writer. Writer append(CharSequence csq) :将指定字符序列添加到此 writer ...

- 【题解】【A % B Problem(P1865)】-C++

题目背景 题目名称是吸引你点进来的 实际上该题还是很水的 题目描述 区间质数个数 输入输出格式 输入格式: 一行两个整数 询问次数n,范围m 接下来n行,每行两个整数 l,r 表示区间 输出格式: 对 ...

- 数据库触发器_trigger

部门表_删除: USE [test] GO /****** Object: Trigger [dbo].[部门_Delete] Script Date: 2015/8/31 16:41:46 **** ...

- 使用GDAL实现DEM的地貌晕渲图(二)

1. 问题 之前我在<使用GDAL实现DEM的地貌晕渲图(一)>这篇文章里面讲述了DEM晕渲图的生成原理与实现,大体上来讲是通过计算DEM格网点的法向量与日照方向的的夹角,来确定该格网点的 ...