quartus使用串口IP模块

在quartus平台中使用串口模块的IP,需要使用到platform designer软件来实现。

1、在quartus界面调出IP Catalog界面。

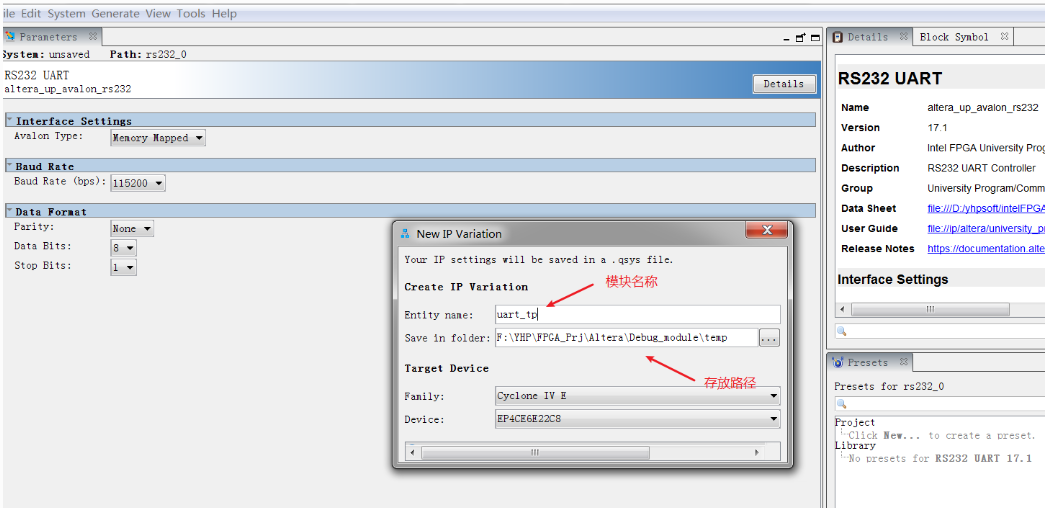

2、在IP catalog中搜索UART,找到RS2323模块,并双击打开,选择合适的路径和存放。

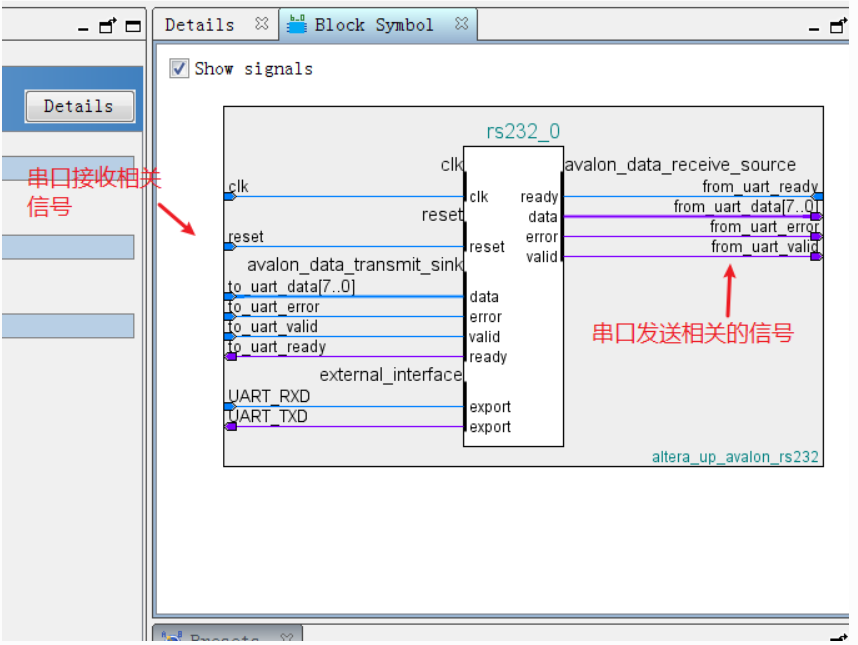

3、使用该模块若不搭建nios软核,则使用streaming。

在右上角电机Block Symbol或者在菜单选择View->Block Symbol打开模块符号。

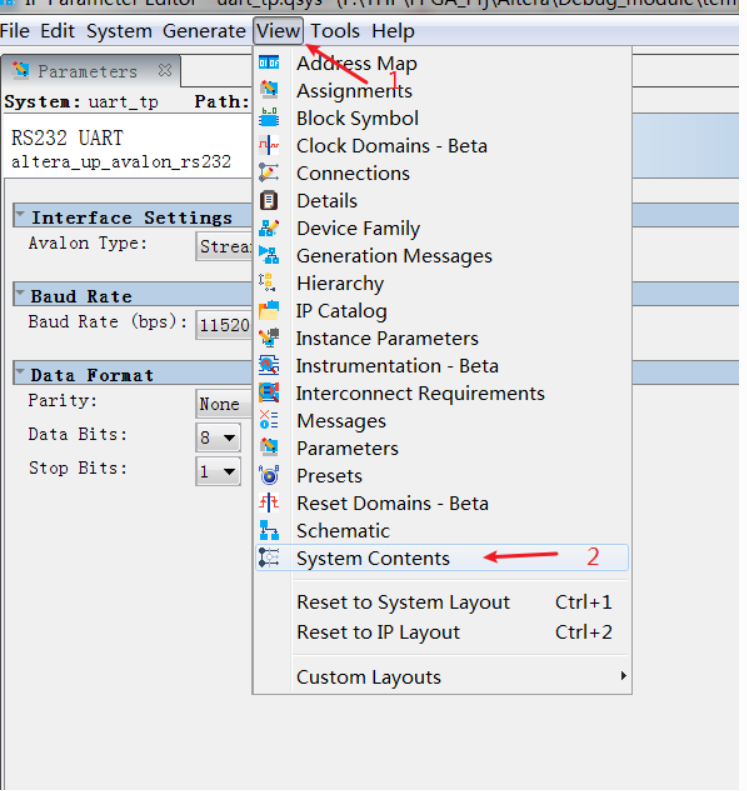

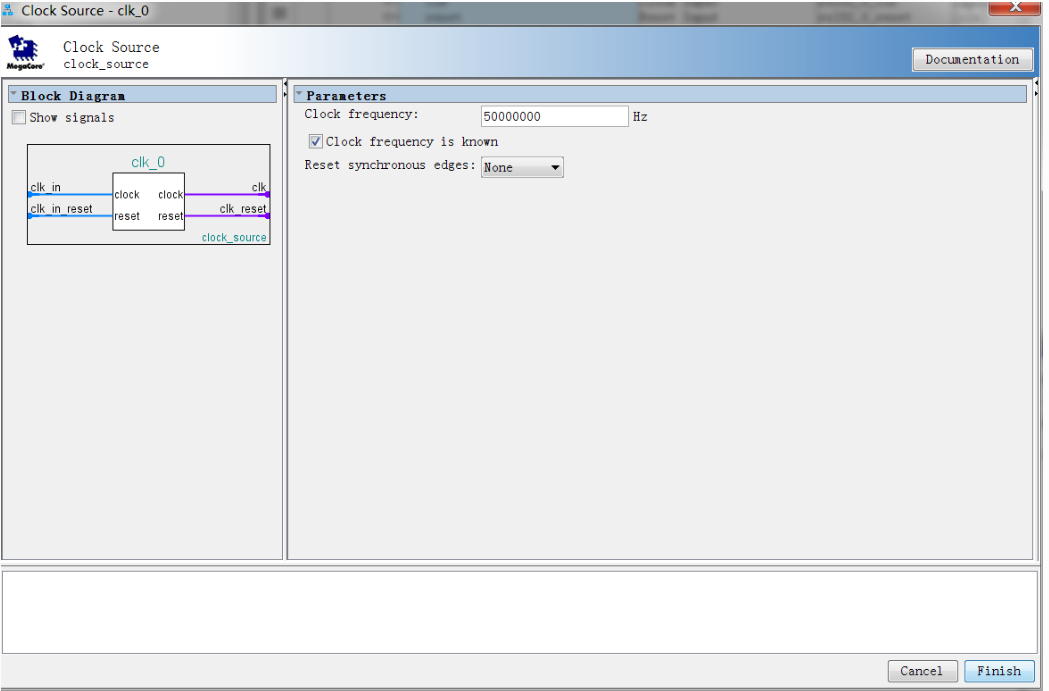

4、串口配置了波特率,其自动配置的参数与时钟有关,因此需要加入时钟模块,告知系统输入时钟为多少。

操作如下:

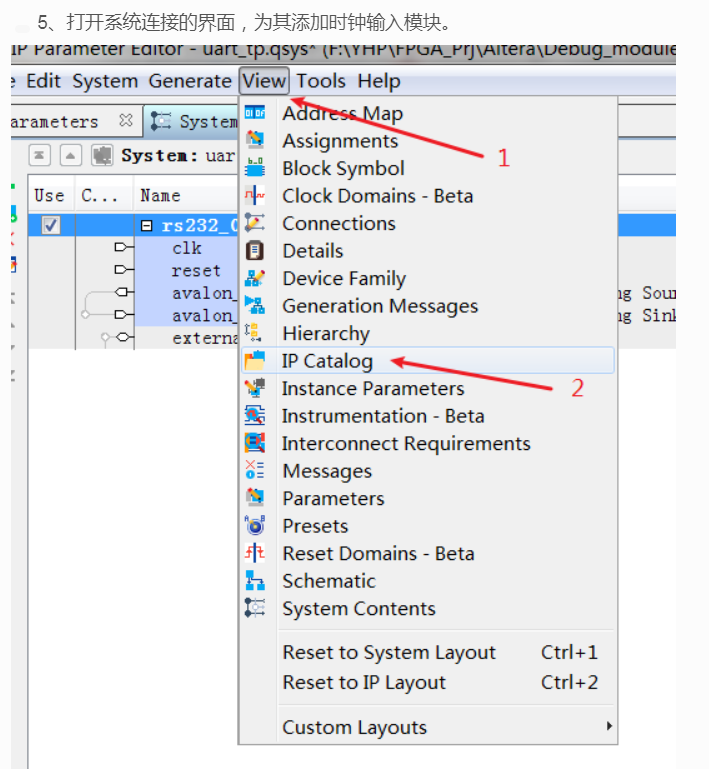

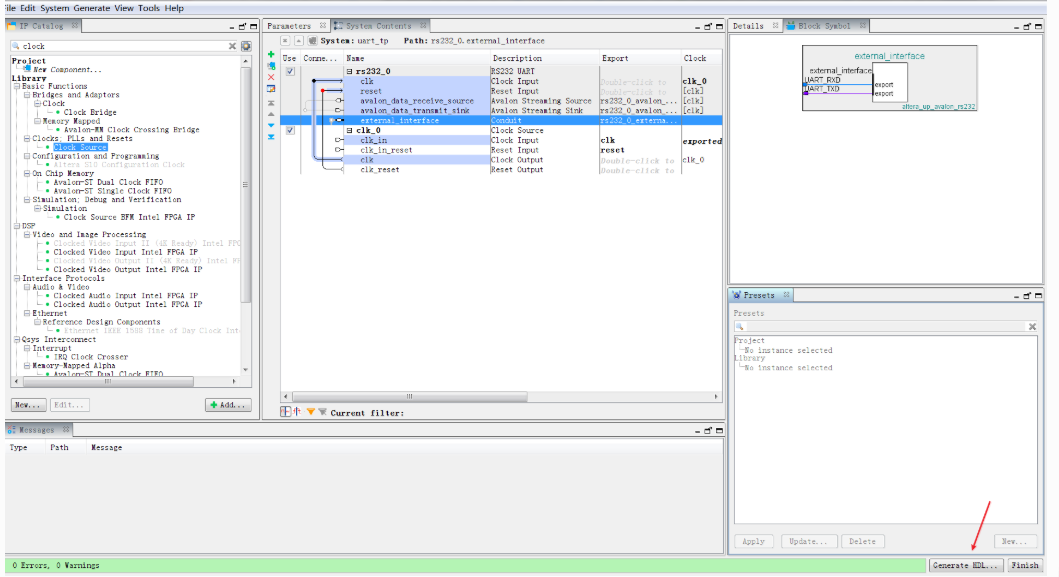

5、打开系统连接的界面,为其添加时钟输入模块。

6、在IP搜索栏搜索clock,双击选择的模块添加时钟模块,输入模块。

7、根据板载资源,设置时钟的参考时钟。

8、连接时钟模块和串口模块的clk和reset。

9、点击Generate HDL生成模块。

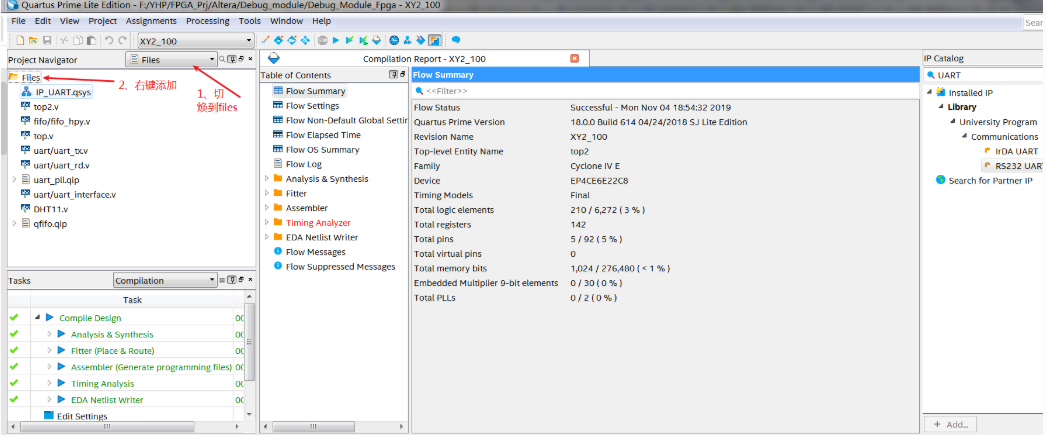

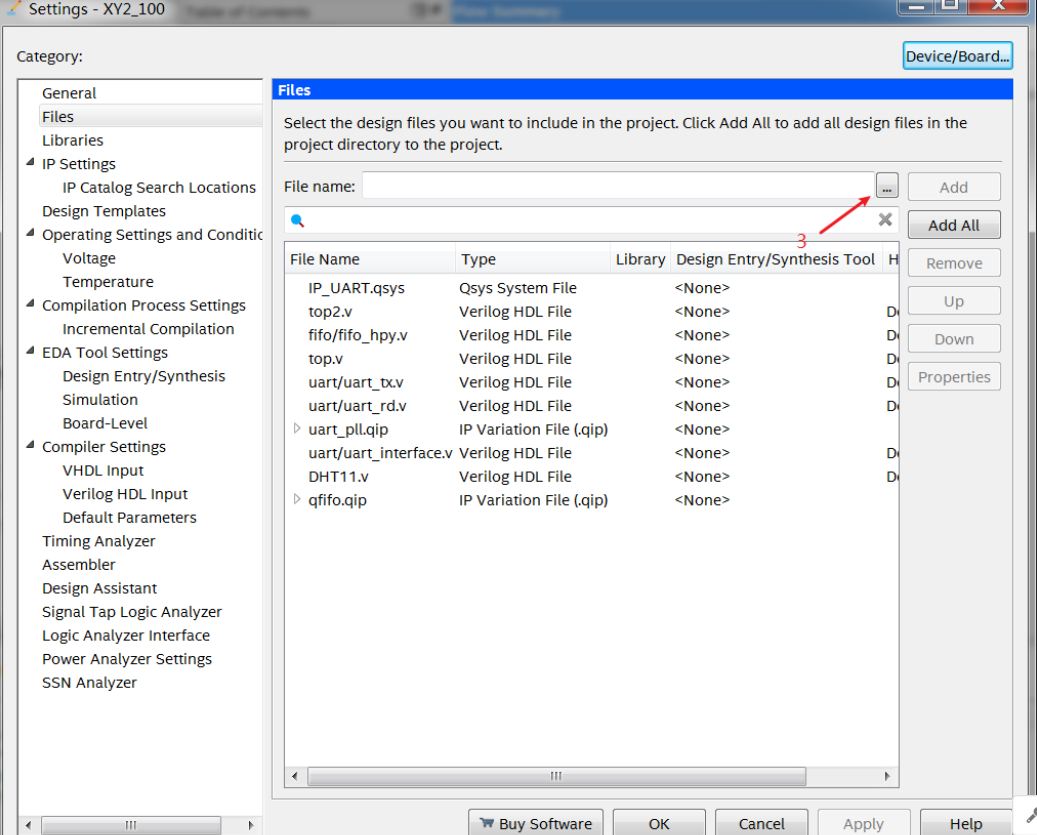

10、在quartus中添加生成的sys系统。

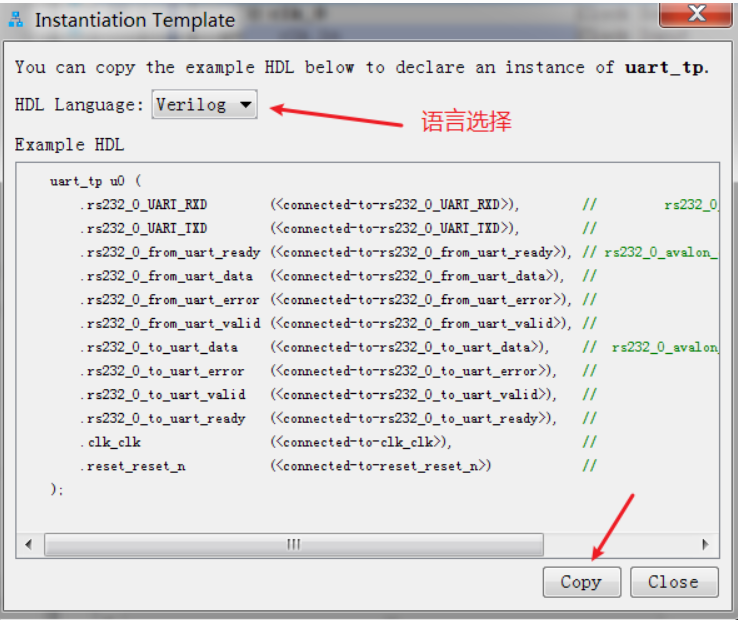

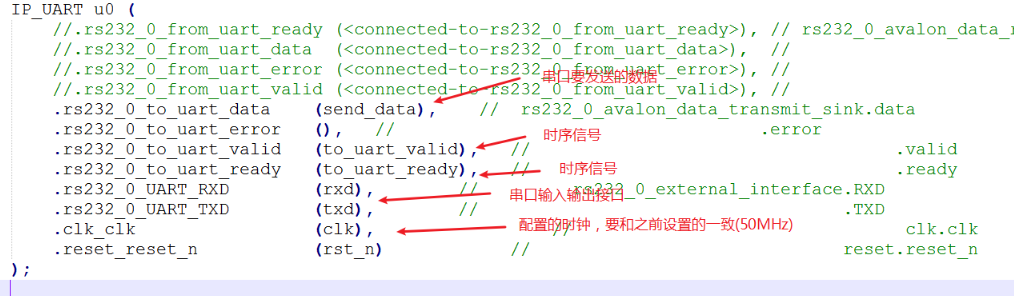

11、从platform designer生成模块实例将实例拷贝到添加到quartus的顶层文件中,添加写数据和读数据的时序。

这里只测试一下串口发送数据的功能,接收数据的操作基本是一样的。

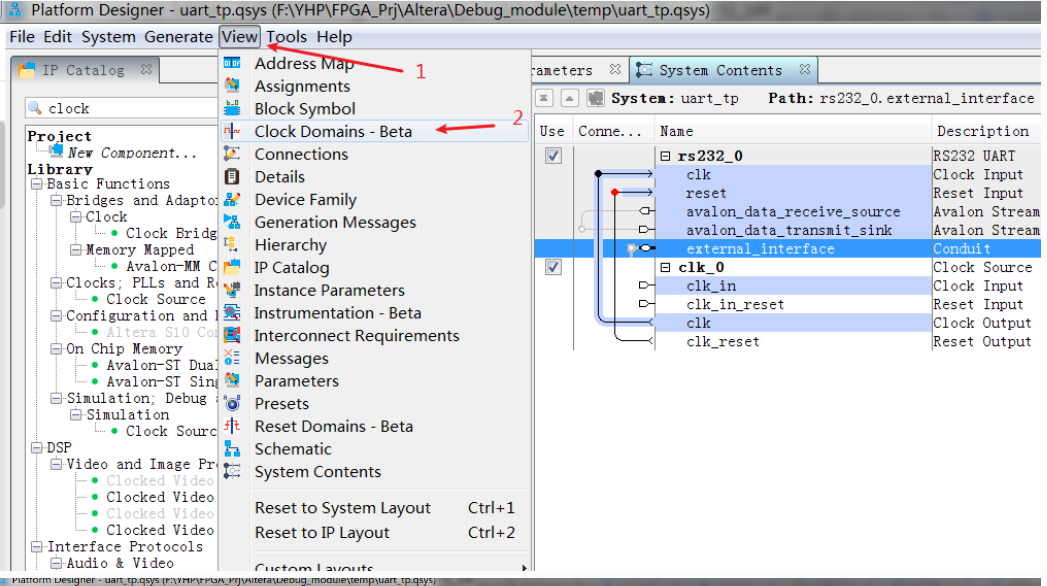

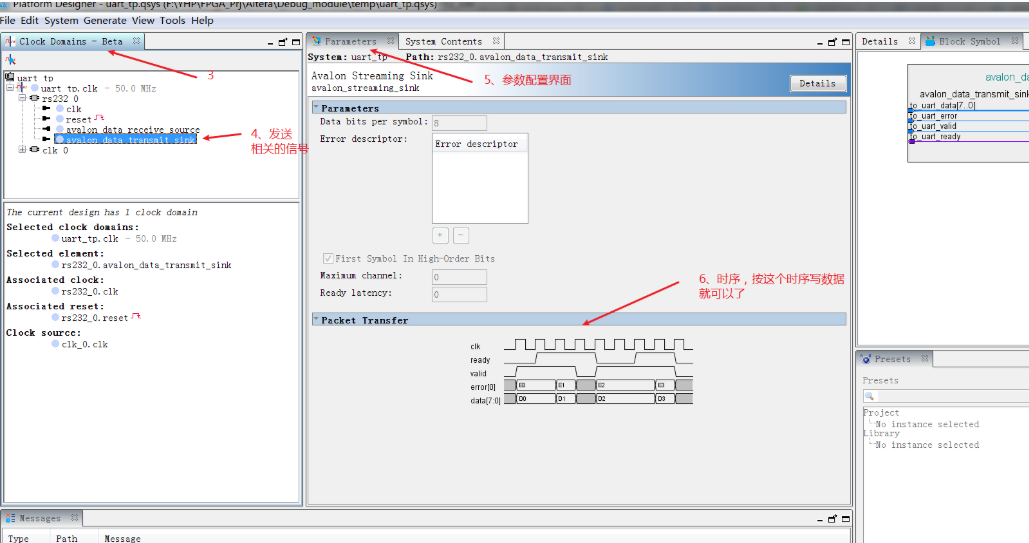

12、在platform designer查看串口模块发送数据的时序。

同理在这里一样可以查看到接收数据的时序。需要注意的是,时序中的数据其实是在to_uart_valid信号为1时,数据会被写入。下面是测试串口发送数据的顶层文件。

module top2(

input wire clk,//50MHz时钟

//rst,//

output reg led, //用于指示

input wire rxd,

output wire txd,

inout dht_io

); //*********************************PROCESS**************************************

// 复位模块

//****************************************************************************** reg rst_n ;

reg [:]delay_cnt;

always@(posedge clk)

begin

if(delay_cnt>='d35530)begin

delay_cnt <= delay_cnt;

rst_n <= 'b1;

end

else begin

rst_n <= 'b0;

delay_cnt <= delay_cnt + 'b1;

end

end

//指示灯

//assign txd = led;

reg [:]cnt;

reg led_f1,tx_flag;

always@(posedge clk)

begin

led_f1 <= led;

tx_flag <= led &(~led_f1);

if(cnt >= 'd25000000 - 1)

begin

cnt <= ;

led <=~led;

end

else begin

cnt <= cnt + 'b1 ;

end

end

//--------------------------------------------

localparam s_s1=;

localparam s_s2=;

localparam s_s3=;

localparam s_s4=;

reg [:]send_data;

reg to_uart_valid , to_uart_ready;

reg [:]send_st;

reg [:]data_cnt;

always@(posedge clk)

begin

if(!rst_n)begin

to_uart_ready <= 'b0;

to_uart_valid <= 'b0;

send_data <= 'd0;

send_st<= s_s1;

data_cnt <= 'd0;

end

else begin

case(send_st)

s_s1:begin//待机

if(tx_flag)begin

send_st <= s_s2;

to_uart_valid <= 'b0;

to_uart_ready<= 'b0;

data_cnt <= 'd0;

send_data <= ;

end

else begin

to_uart_valid <= 'b0;

to_uart_ready<= 'b0;

end

end

s_s2:begin

if(data_cnt <= 'd8-1'b1)begin

to_uart_valid <= 'b1;

//to_uart_ready <= (data_cnt >= 8'd5-1)?1'b0:1'b1;

send_data <= data_cnt+;

data_cnt <= data_cnt + 'b1;

send_st <= (data_cnt >= 'd5-1)?s_s3:s_s2;

end

end

s_s3:begin

to_uart_valid <= 'b0;

to_uart_ready <= 'b1;

send_st <= s_s1;

data_cnt<='d0;

end

default :send_st <= s_s1;

endcase

end

end

IP_UART u0 (

//.rs232_0_from_uart_ready (<connected-to-rs232_0_from_uart_ready>), // rs232_0_avalon_data_receive_source.ready

//.rs232_0_from_uart_data (<connected-to-rs232_0_from_uart_data>), // .data

//.rs232_0_from_uart_error (<connected-to-rs232_0_from_uart_error>), // .error

//.rs232_0_from_uart_valid (<connected-to-rs232_0_from_uart_valid>), // .valid

.rs232_0_to_uart_data (send_data), // rs232_0_avalon_data_transmit_sink.data

.rs232_0_to_uart_error (), // .error

.rs232_0_to_uart_valid (to_uart_valid), // .valid

.rs232_0_to_uart_ready (), // 这是输入信号 .ready

.rs232_0_UART_RXD (rxd), // rs232_0_external_interface.RXD

.rs232_0_UART_TXD (txd), // .TXD

.clk_clk (clk), // clk.clk

.reset_reset_n (rst_n) // reset.reset_n

); endmodule

quartus使用串口IP模块的更多相关文章

- SoC中的IP模块学习

SoC中的IP模块学习 理解IP Spec-->register定义,理解原理+架构框图 查看testcase+model(看已有的测试例程),分析操作/使用模块的流程,寄存器的配置方法 运行仿 ...

- 玩转X-CTR100 l STM32F4 l ESP8266串口WIFI模块

我造轮子,你造车,创客一起造起来!更多塔克创新资讯[塔克社区 www.xtark.cn ][塔克博客 www.cnblogs.com/xtark/ ]- ESP8266是一款非常火的WIFI模块,性价 ...

- 基于H7的串口WIFI模块ESP8266的TCP客户端例子和操作说明(AP兼STA模式)

说明: 1.如果不熟悉网络的话,等我这几天更新V7用户手册的ESP8266章节,如果熟悉的话,直接操作即可,这里将操作说明发出来. 2.串口WIFI是采用的AT指令操作,简单易用,指令手册在这个帖子里 ...

- python 跟踪IP模块

#coding=utf-8 import re import subprocess def tracertIP(ip): p = subprocess.Popen(['tracert',ip],std ...

- Quartus II 中参数化模块库(LPM)的使用

Quartus II 的LPM库所在的目录是\altera\11.0\quartus\libraries\megafunctions 现以LPM_MULT为例进行演示: 思路:1.首先创建一个pro ...

- ESP8266串口模块的基本使用【转】

本文转载自:http://www.shaoguoji.cn/2017/01/15/ESP8266-usage/ ESP8266是一款超低功耗的UART-WiFi 透传模块,拥有业内极富竞争力的封装尺寸 ...

- python自动化运维笔记2 —— IP地址处理模块IPy

1.2 实用的IP地址处理模块IPy ip地址规划是网络设计中非常重要的一个环节,规划的好坏会直接影响路由协议算法的效率,包括网络性能.可扩展性等方面,在这个过程当中,免不了要计算大量的IP地址,包括 ...

- quartus ip核破解

在证书文件中添加一段: FEATURE 6AF7_0012 alterad 2035.12 permanent uncounted E75BE809707E VENDOR_STRING="i ...

- nios II--实验6——串口硬件部分

串口 硬件开发 新建原理图 打开Quartus II 11.0,新建一个工程,File -> New Project Wizard…,忽略Introduction,之间单击 Next> 进 ...

随机推荐

- Save&Load--Unity存档读档的学习总结

存档与读档功能 举例: 传统RPG游戏(仙剑.空之轨迹): 1.角色信息(生命值,等级) 2.道具信息(装备,药品) 3.场景信息(场景名称.角色坐标) 4.事件信息(任务相关) 关卡类游戏:关卡的通 ...

- Spark 学习笔记之 Standalone与Yarn启动和运行时间测试

Standalone与Yarn启动和运行时间测试: 写一个简单的wordcount: 打包上传运行: Standalone启动: 运行时间: Yarn启动: 运行时间: 测试结果: Standalon ...

- IDEA 学习笔记之 Scala项目开发

Scala项目开发: 由于直接下载Scala plugin太慢,老是中断,所以手动下载: https://plugins.jetbrains.com/ 手动安装Scala plugin: 新建Scal ...

- 手把手带你利用Ribbon实现客户端的负载均衡

之前的文章<SpringCloud搭建注册中心与服务注册>介绍了注册中心的搭建和服务的注册,本文将介绍下服务消费者通过Ribbon调用服务实现负载均衡的过程. 本文目录 一.Ribbon服 ...

- linux下修改python版本号

修改python版本 1.查看已安装版本: /home/user$ whereis python 2.在其 home 目录下创建一个 alias(别名) user@ubuntu:/home/user$ ...

- 排坑日记之批量从库IO进程停止

早上刚睁眼,看到了一堆数据库告警的短信,其中一个内容如下: Problem started at 05:02:58 on 2019.10.12 Problem name: Slave is stopp ...

- Springboot2.x + ShardingSphere 实现分库分表

之前一篇文章中我们讲了基于Mysql8的读写分离(文末有链接),这次来说说分库分表的实现过程. 概念解析 垂直分片 按照业务拆分的方式称为垂直分片,又称为纵向拆分,它的核心理念是专库专用. 在拆分之前 ...

- cocos2d-x 系统学习cocos(2) 交互

交互 玩游戏的时候,我们需要用输入设备和游戏进行交互,那么游戏需要对玩家做出相应,比如说按下键盘的上下左右,角色就朝着对应的方向移动,按下技能键,角色就释放技能 键盘监听 响应 cocos2d-x中要 ...

- Python_三元运算与lambda表达式

[是什么] 三元运算是if...else...的简化版,lambda表达式是函数的简化版 三元运算(三目运算) # 判断两个数中的较大者 fun(a1,a2): return a1 if a1> ...

- Hibernate HQL注入与防御(ctf实例)

遇到一个hql注入ctf题 这里总结下java中Hibernate HQL的注入问题. 0x01 关于HQL注入 Hibernate是一种ORM框架,用来映射与tables相关的类定义(代码) ...