FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习,将感悟记于此,如有错误,欢迎指出、讨论。

一、关于时钟引脚

FPGA芯片一般有好几组时钟引脚 CLK [0..N] [p,n],我的理解是:首先,时钟必须由外部晶振通过CLK引脚输入到FPGA的时钟网络,至于选用哪一组CLK,主要看FPGA哪个bank对时钟要求最为苛刻;其次,一般用p端,n端由quartus置位三态;再次,对于简单的系统,只有一组CLK输入作为系统主时钟,其他时钟引脚空置,或者作为某些高带载能力的时钟的输出口(是否可作为输出口,要看芯片手册);然后,复杂系统,可以有不同源的时钟分别从不同CLK引脚输入,只是猜想,没实践过,个人认为这样不好,因为FPGA的核心就是同步;另外,不要把CLK引脚和全局时钟、区域时钟什么的混为一谈,一个是时钟输入引脚,一个是内部时钟走线;最后,CLK引脚进去的走线肯定进过优化的(H型铜皮,专用的、直达每个触发器的布线资源),所以能做到小的抖动和偏斜,带载能力

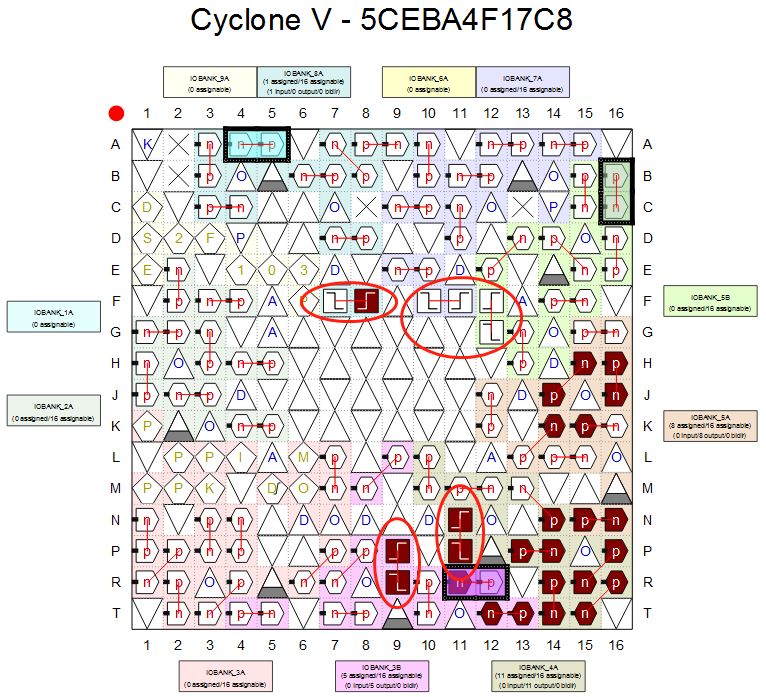

图1

图2

图1所示:红圈为时钟输入引脚,当然,从时钟引脚输入的时钟必定首先进入全局时钟网络,再进一步驱动区域时钟,或者由PLL进行分/倍频==;三个黑色方框内PLL输出引脚,我的理解是:这几组引脚的布线也经过了优化,可以使PLL分/倍频后输出的时钟信号质量较好。

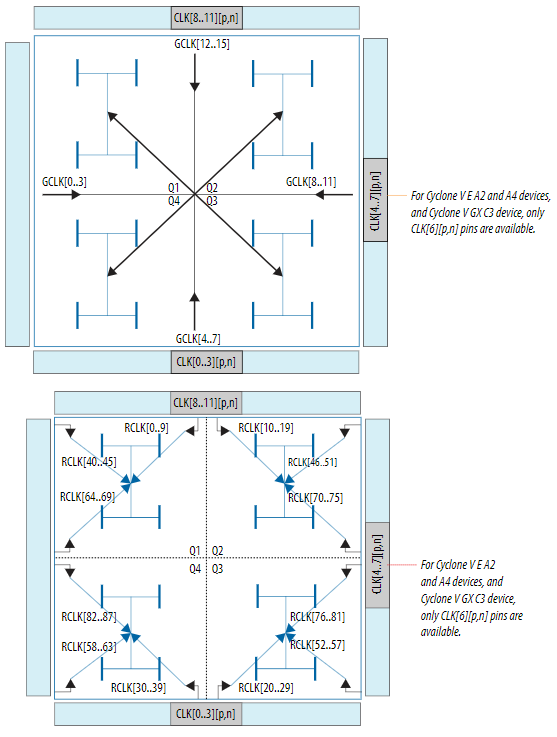

图2所示:CLK9p作为系统唯一的外部输入时钟源,图3

图4

******注意******

- 常规操作:外部晶振—>时钟引脚—>PLL—>区域时钟、各个模块、输出(待验证和完善,我也迷)。

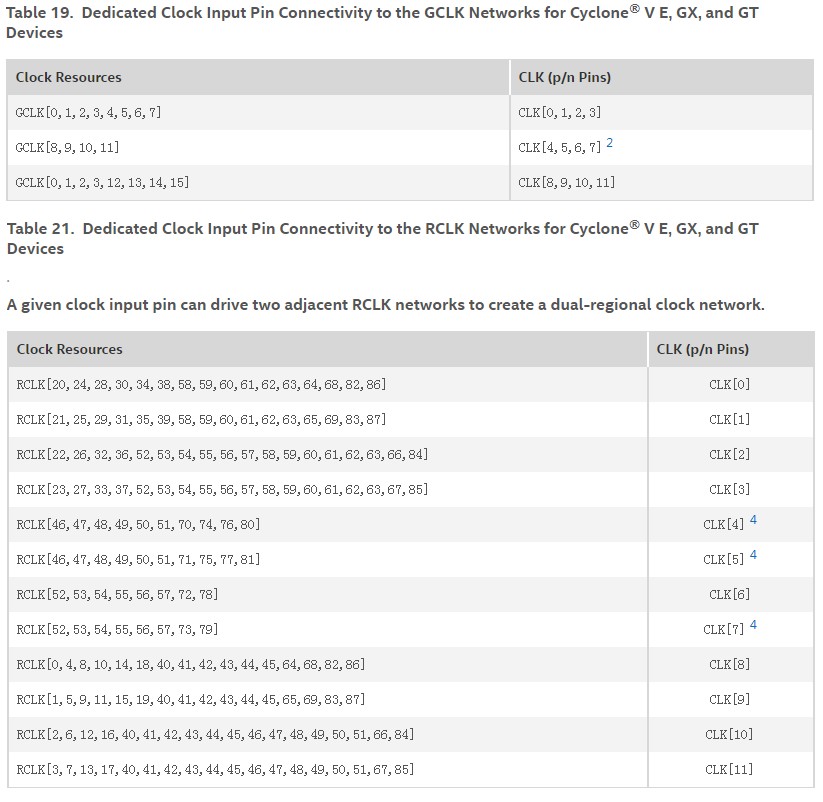

- 关于CLK引脚选择:不是所有的CLK引脚都可以连接到所有的全局/区域时钟网路,见图5。

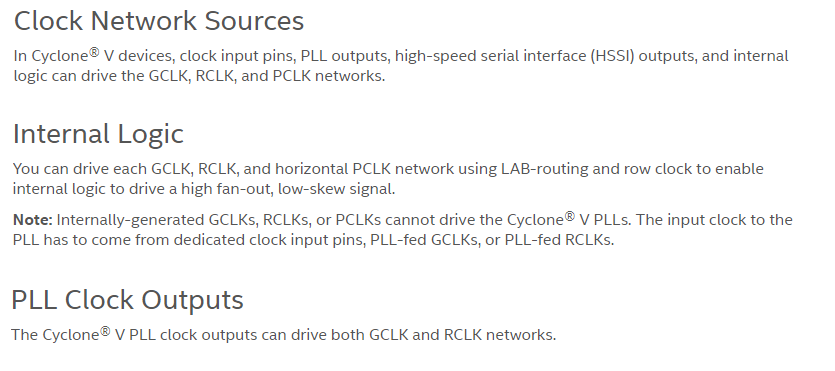

- 关于PLL:不是所有始终都可以驱动PLL,详见手册,如图6所示。

图5

图6

三、时钟资源的使用、分配

20181101提出

- 疑问:编写逻辑电路,或者布局布线时,我怎么知道某个时钟具体使用了哪种、哪个网络?以及怎么人为地控制使用具体某个网络?

20181102补充

- 除非是时钟资源(尤其是全局时钟资源)紧张,或者需要进行时序优化,否则,一般不用过于关心这些资源怎么使用的,quartus会根据电路逻辑,自动选择最优的布局布线。

- 实际上,根据硬件电路和逻辑电路,也能推断出用了多少全局时钟、区域时钟。

- 比如:clk0=50MHz,然后它在几个always中都被用到,而这几个always占用的逻辑资源分布在不同的区域,那么这个时钟应该是全局时钟;再比如:clk1=100MHz,它只在一个always里被使用,或使用它的逻辑资源都在一个区域,那么clk1应该是区域时钟。

- https://www.cnblogs.com/zuilangsanshu/

FPGA系列之一:Cyclone V中的时钟资源的更多相关文章

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- 三叔学FPGA系列之二:Cyclone V中的POR、配置、初始化,以及复位

对于FPGA内部的复位,之前一直比较迷,这两天仔细研究官方数据手册,解开了心中的诸多疑惑,感觉自己又进步了呢..... 原创不易,转载请转原文,注明出处,谢谢. 一.关于POR(Power-On ...

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- Xilinx Altera FPGA中的逻辑资源(Slices VS LE)比较

前言 经常有朋友会问我,“我这个方案是用A家的FPGA还是X家的FPGA呢?他们的容量够不够呢?他们的容量怎么比较呢?”当然,在大部分时候,我在给客户做设计的时候,直接会用到最高容量的产品,因为我们的 ...

- 友晶Altera Cyclone V GX Starter Kit开发板使用ADC-第一篇

1. 拿到板子在,做工很好,属于GX系列,GX应该是高速收发器 2. 去探究下GX是什么用途,大约有6个型号,这个板子是5CGXFX5,有77 LE逻辑单元,这个收发器不知道是什么?6个 3.125G ...

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

- SSE 系列内置函数中的 shuffle 函数

SSE 系列内置函数中的 shuffle 函数 邮箱: quarrying@qq.com 博客: http://www.cnblogs.com/quarryman/ 发布时间: 2017年04月18日 ...

- Spartan6系列之Spartan6系列之芯片时钟资源深入详解

1. 时钟资源概述 时钟设施提供了一系列的低电容.低抖动的互联线,这些互联线非常适合于传输高频信号.最大量减小时钟抖动.这些连线资源可以和DCM.PLL等实现连接. 每一种Spartan-6芯片提 ...

随机推荐

- OCM_第六天课程:Section3 —》数据库可用性

注:本文为原著(其内容来自 腾科教育培训课堂).阅读本文注意事项如下: 1:所有文章的转载请标注本文出处. 2:本文非本人不得用于商业用途.违者将承当相应法律责任. 3:该系列文章目录列表: 一:&l ...

- Laravel 的文件存储 - Storage

记录一下 Laravel Storage 的常见用法 内容写入磁盘文件 > php artisan tinker >>> use Illuminate\Support\Faca ...

- mysql 快速拷贝表

- Codeforces Round #469 (Div. 2)

Codeforces Round #469 (Div. 2) 难得的下午场,又掉分了.... Problem A: 怎么暴力怎么写. #include<bits/stdc++.h> #de ...

- Storm通信机制(了解)

Worker间的通信:经常需要通过网络跨节点进行,Storm使用ZeroMQ或Netty(0.9以后默认使用)作为进程间通信的消息框架. Worker进程内部通信:不同worker的thread通信使 ...

- zyb的面试

今天zyb参加一场面试,面试官听说zyb是ACMer之后立马抛出了一道算法题给zyb:有一个序列,是1到n的一种排列,排列的顺序是字典序小的在前,那么第k个数字是什么?例如n=15,k=7, 排列顺序 ...

- 使用PhoneGap搭建一个山寨京东APP(转)

为什么要写一个App 首先解释下写出来的这个App,其实无任何功能,只是用HTML和CSS模仿JD移动端界面写的一个适配移动端的Web界面.本篇主要内容是介绍如何使用PhoneGap把开发出来的m ...

- centos6.8 yum安装mysql 5.6 (完整)

一.检查系统是否安装其他版本的MYSQL数据 #yum list installed | grep mysql #yum -y remove mysql-libs.x86_64 二.安装及配置 # w ...

- Mysql学习(一)添加一个新的用户并用golang操作Mysql

Mysql添加一个新的用户并赋予权限 添加一个自己的用户到mysql 首先我们需要先用root用户登录mysql,但是刚安装完没有密码,我们先跳过密码 ailumiyana@ailumiyana:~/ ...

- Spring框架学习09——基于AspectJ的AOP开发

1.基于注解开发AspectJ (1)AspectJ注解 基于注解开发AspectJ要比基于XML配置开发AspectJ便捷许多,所以在实际开发中推荐使用注解方式.关于注解的相关内容如下: @Aspe ...