CRC校验原理和verilog实现方法(三)

1 代码生成

verilog实现CRC校验,可以充分发挥FPGA的硬件特性,即并行运算的能力。

具体实现方式,可以参考我上一篇博客,关键是用线性反馈移位寄存器表示出多项式,另外注意校验数据高位在先。然后根据电路结构推导出逻辑表达式,再转换成verilog就行了。

更高效的方法是利用现成的代码生成工具,例如附件的链接1,就是一种在线的CRC校验代码生成工具。

2 修改移植

我这里用代码生成工具生成多项式为x^4 + x^1 + 1,即CRC-4/ITU校验模型,校验输入数据位宽为4bit的CRC代码,并分享一下修改移植时的心得。

生成的代码如下,这个多项式和我上一篇博客举例所用多项式一样,所以生成的代码之前推导的逻辑表达式也是相同的。

function [3:0] nextCRC4_D4;

input [3:0] Data;

input [3:0] crc;

reg [3:0] d;

reg [3:0] c;

reg [3:0] newcrc;

begin

d = Data;

c = crc;

newcrc[0] = d[3] ^ d[0] ^ c[0] ^ c[3];

newcrc[1] = d[3] ^ d[1] ^ d[0] ^ c[0] ^ c[1] ^ c[3];

newcrc[2] = d[2] ^ d[1] ^ c[1] ^ c[2];

newcrc[3] = d[3] ^ d[2] ^ c[2] ^ c[3];

nextCRC4_D4 = newcrc;

end

endfunction

其实这段代码有用的只是中间那四行行为级赋值语句,可以直接拷贝到工程里使用。其中d是4位的校验数据,c是CRC寄存器。

用这段代码做CRC校验时,有几点需要明确:

1)数据位宽。

2)输入输出是否高低位反转。

3)c的初值。

4)输出是否按位取反。

其中第1点取决于通信时一帧数据的长度,第2、3点一般在常用的CRC校验模型中规定好了。这里用的CRC-4/ITU校验模型规定c的初值为0,输出不需要取反,输入输出高低位需要反转。

如果被校验数据data只有4bit,那么直接令data高低位反转后赋值d,c=0,组合逻辑输出的就是4位newcrc做高低位反转,最后得到的就是CRC校验码;

假如被校验的数据位数大于4bit,需要按字节来进行“叠加”校验。

比如数据data[15:0]=1577h,那么安照这样的校验流程:高字节低4bit(5h)反转后给d——newcrc作为下次校验的c的值——高字节高4bit(1h)反转后给d——newcrc作为下次校验的c的值——低字节低4bit(7h)反转后给d——newcrc作为下次校验的c的值——低字节高4bit(7h)反转后给d——newcrc反转后作为CRC校验码。

c的更新可以用寄存器实现。如下所示:

reg [3:0] c;

wire [3:0] d; //参与校验数据

assign d = {data_r[0], data_r[1], data_r[2], data_r[3]};//翻转数据位

assign newcrc[0] = crc_en & (d[3] ^ d[0] ^ c[0] ^ c[3]);

assign newcrc[1] = crc_en & (d[3] ^ d[1] ^ d[0] ^ c[0] ^ c[1] ^ c[3]);

assign newcrc[2] = crc_en & (d[2] ^ d[1] ^ c[1] ^ c[2]);

assign newcrc[3] = crc_en & (d[3] ^ d[2] ^ c[2] ^ c[3]);

always @(posedge clk or negedge rstn) begin

if(!rstn)

c <= 4'h0;//初始0

else begin

if(start_pos)

c <= 4'h0;

else if(crc_en)

c <= newcrc;

end

end

3 功能验证

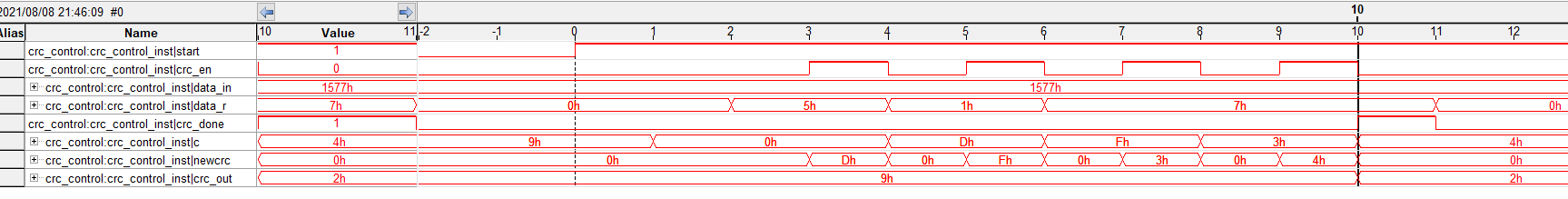

为了验证上面修改的代码功能,编写了测试代码,对16bit的数据求校验码。这里分别验证了data[15:0]=1577h和data[15:0]=4511h两个数据的CRC校验。

1)data[15:0]=1577h

在开发板上运行测试代码,用signalTAP观察结果(电脑上没有装Modelsim),其中data_in为待校验数据,经过4次计算,得到校验码为crc_out=0x2。

利用在线CRC计算工具(链接见我之前的博客),计算1577h的校验码,与测试结果一致:

2)data[15:0]=4511h

得到校验码为crc_out=0xF。

利用在线CRC计算工具(链接见我之前的博客),计算4511h的校验码,与测试结果一致:

这就说明,本文的“叠加”校验,可以实现对多字节数据的“分段”校验。多字节数据可以是4字节、16字节等,CRC校验代码中的输入数据d可以是1bit、2bit、4bit、8bit等。

不过据我的经验,要实现这种“叠加”校验,必须设置输入输出数据高低位反转,不然结果不对。也就是说如果你选的校验模型不需要数据位反转,那么只能做一次性的校验了。具体原因咱也研究不清楚,不知道有没有大神解答。

在线CRC代码生成链接:

1、https://www.easics.com/crctool/

CRC校验原理和verilog实现方法(三)的更多相关文章

- CRC校验原理和verilog实现方法(二)

1 前言 在 前面的博客 CRC校验原理和verilog实现方法(一) 中,介绍了CRC校验的原理和手动计算过程.本文说一下我在学习CRC校验FPGA实现的一点心得体会. 2 线性反馈移位寄存器 ...

- CRC校验原理和verilog实现方法(一)

1.CRC简介 CRC全称循环冗余校验(Cyclic Redundancy Check, CRC),是通信领域数据传输技术中常用的检错方法,用于保证数据传输的可靠性.网上有关这方面的博客和资料很多,本 ...

- 流水线技术原理和Verilog HDL实现(转)

源:流水线技术原理和Verilog HDL实现 所谓流水线处理,如同生产装配线一样,将操作执行工作量分成若干个时间上均衡的操作段,从流水线的起点连续地输入,流水线的各操作段以重叠方式执行.这使得操作执 ...

- 流水线技术原理和Verilog HDL实现

所谓流水线处理,如同生产装配线一样,将操作执行工作量分成若干个时间上均衡的操作段,从流水线的起点连续地输入,流水线的各操作段以重叠方式执行.这使得操作执行速度只与流水线输入的速度有关,而与处理所需的时 ...

- golang中浮点型底层存储原理和decimal使用方法

var price float32 = 39.29 float64和float32类似,只是用于表示各部分的位数不同而已,其中:sign=1位,exponent=11位,fraction=52位,也就 ...

- Verilog语言实现并行(循环冗余码)CRC校验

1 前言 (1) 什么是CRC校验? CRC即循环冗余校验码:是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定.循环冗余检查(CRC)是一种数据传输检错功能, ...

- 用C#实现的几种常用数据校验方法整理(CRC校验;LRC校验;BCC校验;累加和校验)

CRC即循环冗余校验码(Cyclic Redundancy Check):是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定.循环冗余检查(CRC)是一种数据传输检错 ...

- 常用校验码(奇偶校验码、海明校验码、CRC校验码)

一.奇偶校验码 二.海明校验码 三.CRC校验码 计算机系统运行时,各个部之间要进行数据交换.交换的过程中,会有发生误码的可能(即0变成1或1变成0),由于计算机的储存是通过二进制代码来实现的的, ...

- CRC校验的C语言实现

文章转自 循环冗余校验(CRC)算法入门引导 - Ivan 的专栏 - 博客频道 - CSDN.NET http://blog.csdn.net/liyuanbhu/article/details/7 ...

随机推荐

- Mongo写入安全机制

写入安全(Write Concern) 是一种客户端设置,用于控制写入的安全级别.默认况下,插入.删除和更新都会一直等待数据库响应(写入是否成功),然后才会继续执行.通常,遇到错误时,客户端会抛出一个 ...

- 堆&&优先队列&&TreeMap

题目描述 5710. 积压订单中的订单总数 题解 题目不难,主要是要读懂题意,一步步模拟,代码较长,需要细心检查. 坑较多,比如我犯了很多傻逼问题:想都不想就拿1<<9+7当作100000 ...

- Flask(8)- jinja2 模板入门

前言 之前的文章有个栗子,视图函数可以直接返回一段 html 代码,浏览器可以自动渲染 但是当你的 HTML 非常复杂的话,也要整串写在代码里面吗,这显然不合理的,可阅读性也非常差 所以,就诞生了 J ...

- MySql:Windows10安装mysql-8.0.18-winx64步骤

步骤: 1. 首先在安装的mysql目录下创建my.ini文件 (深坑)注意:my.ini必须保存为ANSI格式!!! 可以先创建一个my.txt的文件,然后另存为ANSI格式的文件! my.ini内 ...

- MySQL 卡死的问题

1. 执行show full processlist观察state和info两列,查看有哪些线程在运行. 2.使用kill命令+对应线程前面id杀死卡死的线程. 其他的方式: -- 查询是否锁表 sh ...

- 深度解析HashMap底层实现架构

摘要:分析Map接口的详细使用以及HashMap的底层是如何实现的? 本文分享自华为云社区<[图文并茂]深度解析HashMap高频面试及底层实现结构![奔跑吧!JAVA]>,原文作者:灰小 ...

- konga的初步使用

目录 1. 设置连接 2. konga的重要功能 Dashboard Snapshots Settings 3. 通过konga 实现kong api配置 前言: 在上篇文章中,我们已经创建了一个到k ...

- excle名字后面直接跟别的出来

名字后面直接跟别的出来 =IF($E6="","",VLOOKUP(E6,通讯录!$B$2:$D$1000,3,0)) $E6:是填写位置的地方 VLOOKUP ...

- Oracle-索引分裂研究

目录 索引分裂介绍 分类 索引分裂实验 基础环境准备 基础信息统计--之前 数据插入 基础信息统计--之后 Trace 数据统计 数据分析 索引PRI_ID之dba_extents视图 索引PRI_I ...

- python exec()函数

''' 函数的作用: 动态执行python代码.也就是说exec可以执行复杂的python代码,而不像eval函数那样只能计算一个表达式的值. exec(source, globals=None, l ...