怎么用Verilog语言描述同步FIFO和异步FIFO

感谢

知乎龚大佬

打杂大佬

网上几个nice的博客(忘了是哪个了。。。。)

前言

虽然FIFO都有IP可以使用,但理解原理还是自己写一个来得透彻。

什么是FIFO?

Fist in first out。先入先出的数据缓存器,没有外部读写地址线,可同时读写。

规则:永远不要写一个已经写满了的fifo。

永远不要读一个读空了的fifo。

FIFO种类?

同步FIFO和异步FIFO。

同步FIFO只有一个时钟,也就是说写端和读端的时钟是一毛一样的。

异步FIFO读端和写端两个时钟则是不一样的。包括同频异相,异频异相。

FIFO用途?

- 数据缓冲器。比如你写端burst一个数据,没有fifo缓冲的话就炸了。Fifo会把写端的突发数据吃到肚子里,读端可以慢慢的一个个读出来。

- 跨时钟域。异步fifo主要使用在不同时钟域的边缘,用来同步数据到另一个时钟域。

ALTERA FIFO IP 的缺点是什么?

虽然altera贴心的提供了FIFO的IP块,但是对于可移植性与自定义位宽深度更好的话,还是自己写的更佳。

FIFO深度如何计算?(避免溢出)

对于异步fifo,如果读时钟大于写时钟且每个周期读写,那么一定是会读空的,反之一定会被写满。一般来说,不会设计这么无聊的东西。

假设写端有突发的数据,而读端是均匀的读出,怎么保证fifo不溢出呢?

异步FIFO快转慢的问题:可能采样踩不到某些值。

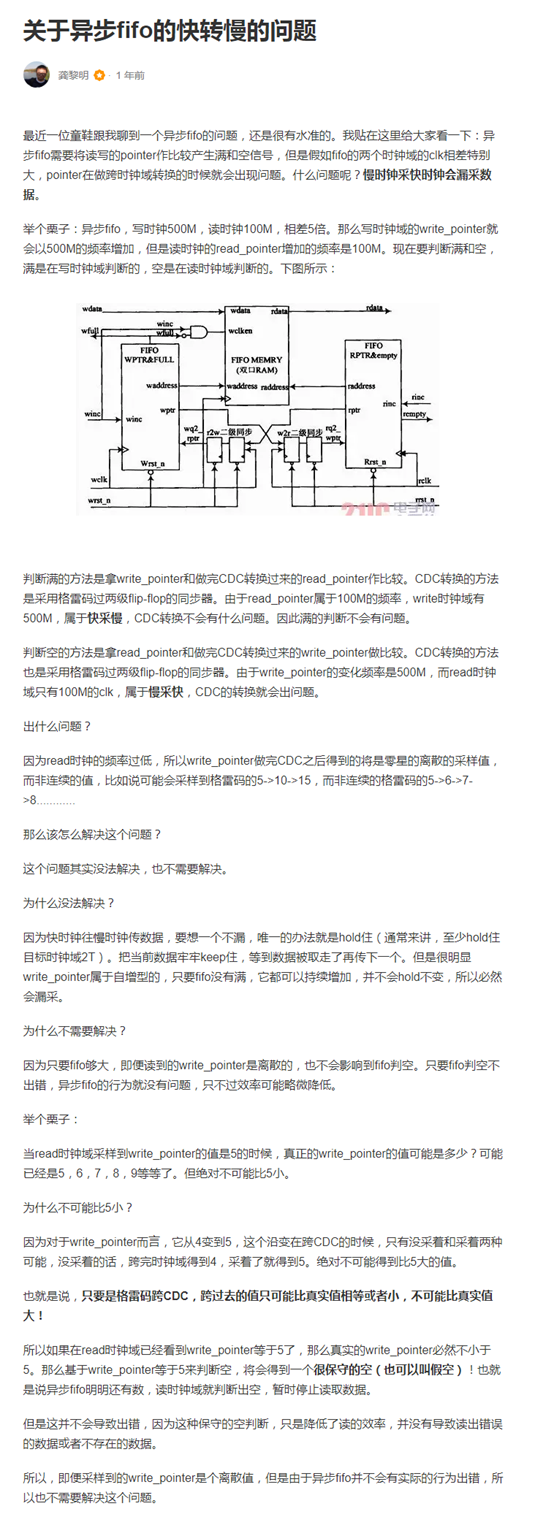

同步FIFO:

当缓冲器使用,可以用ram资源搭。

原理图:

信号定义:

clk:时钟信号

rst_n:异步复位信号

wr:写请求

rd:读请求

data:数据输入

q: 数据输出

full:满信号,表示fifo吃饱了

empty:空信号,表示fifo肚子已经空掉了

usedw:表示fifo中已有的数据个数

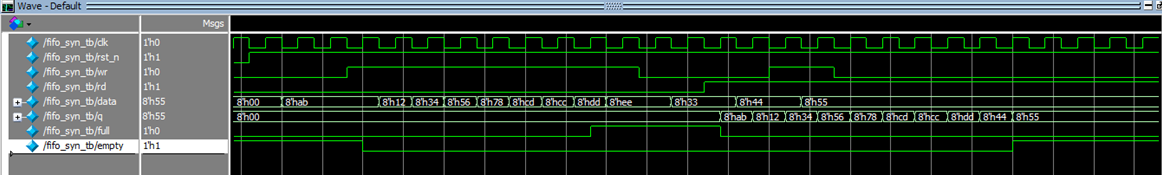

仿真:

没有usedw款:

有usedw款:

资源使用量:

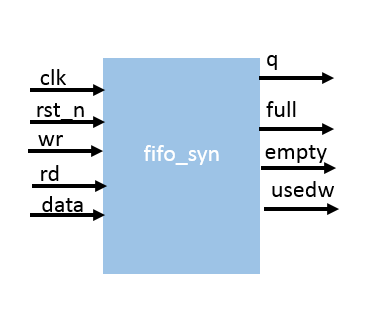

如何设计一个异步FIFO?

一般用作跨时钟域,可用ram搭。

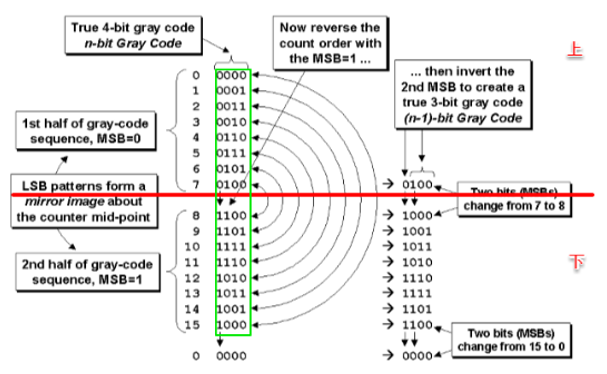

判断读空与写满,读写指针要跨时钟域,所以采用格雷码减少亚稳态。

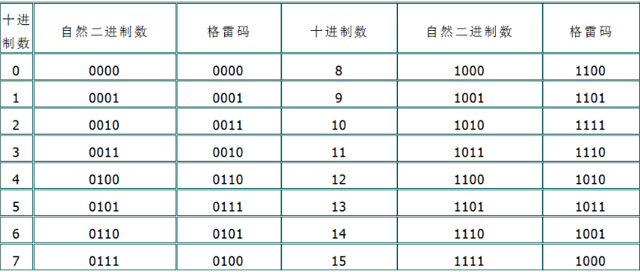

什么是格雷码?如何与二进制码转换?

格雷码的基本特点是两个相邻的码只有一位二进制数不同。

二进制转格雷码:

简单来说就是把二进制码右移一位再与二进制异或。

assign wr_poi_gray = wr_poi ^ (wr_poi>>1); //produce wr pointer gray code;

格雷码转二进制:

格雷码转二进制是从左边第二位起,将每位与左边一位二进制码的值异或,作为该位二进制码的值。

比如四位的码:

bin[3] = gray[3];

bin[2] = gray[2]^bin[3];

bin[1] = gray[1]^bin[2];

bin[0] = gray[0]^bin[1];

原理图:

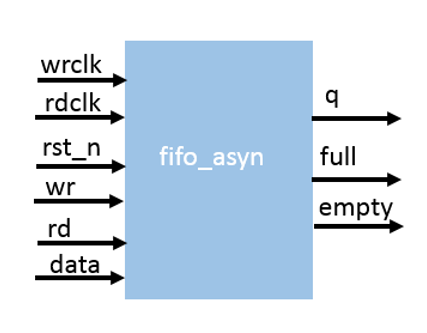

信号定义:

wrclk:写时钟信号

rdclk: 读时钟信号

rst_n:异步复位信号

wr:写请求

rd:读请求

data:数据输入

q: 数据输出

full:满信号,表示fifo吃饱了

empty:空信号,表示fifo肚子已经空掉了

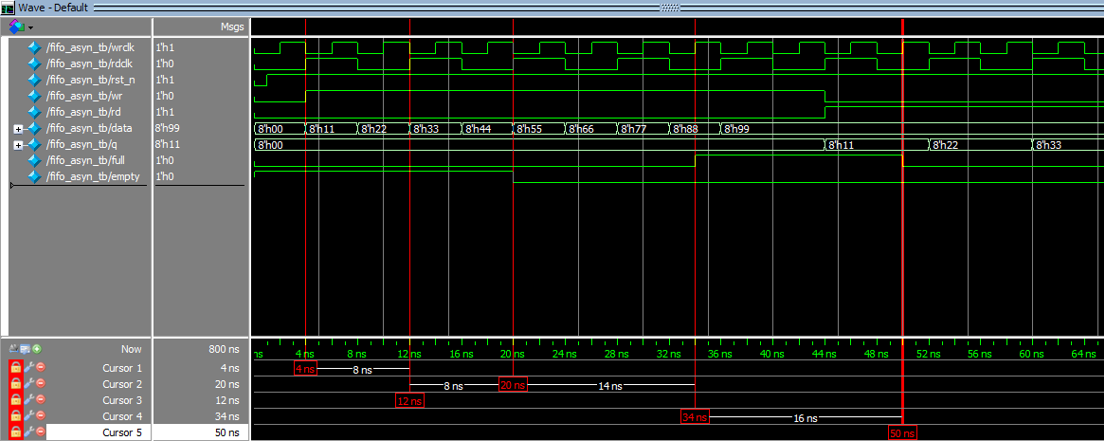

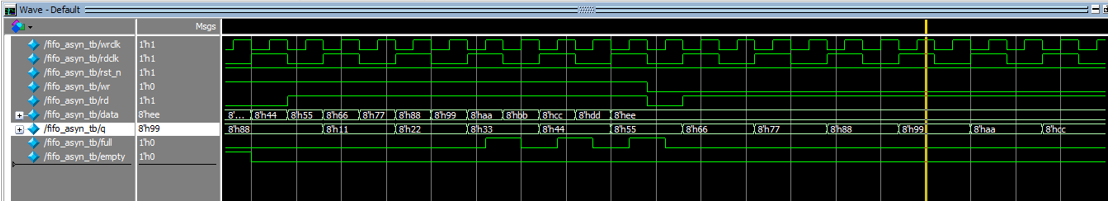

仿真:写时钟是读时钟的两倍。

写读测试:由于两级同步器的存在,判定空满滞后两个周期。

同时读写测试:

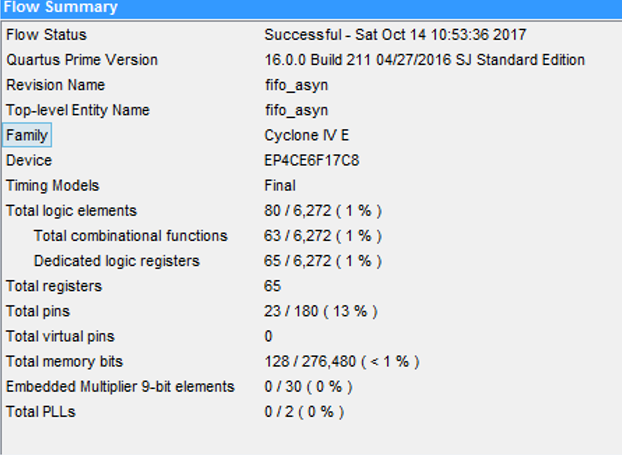

资源使用量:

注意:

同步FIFO的地址扩展一位作为判断空满的状态位,读写指针低位都相同的时候,最高位相同则表示读空,不同则表示写满。

assign full = (wr_poi[clogb2(DEPTH)-:]== rd_poi[clogb2(DEPTH)-:]) && (wr_poi[clogb2(DEPTH)] ^ rd_poi[clogb2(DEPTH)] == ); //highest bit is not same but rests bit is same;

assign empty = (wr_poi[clogb2(DEPTH)-:]== rd_poi[clogb2(DEPTH)-:]) && (wr_poi[clogb2(DEPTH)] ^ rd_poi[clogb2(DEPTH)] == ); //every bit is same;

异步FIFO的地址位也扩展一位作为状态位,通过格雷码跨过时钟域判断空满。

在写时钟域判断full:如果本时钟域的写地址格雷码和同步过来的读地址格雷码最高位和次高位均不同,其余位相同,则表示写满了。

在读时钟域判断empty:如果本时钟域的读地址格雷码和同步过来的写地址格雷码最高位和次高位都一样,其余位也一样,则表示读空。

assign full = (wr_poi_gray == {~rd_poi_gray2[clogb2(DEPTH):clogb2(DEPTH)-],rd_poi_gray2[clogb2(DEPTH)-:]});

assign empty = (wr_poi_gray2 == rd_poi_gray);

贴一下同步FIFO的代码:

已定制ramstyle,如果你的不同请删掉或者更改。深度必须为2^n,否则更改函数clogb2中的depth为depth>0.

仅供学习交流,请勿用于商业用途,版权所有。异步代码就不贴了,想研究请联系我。

//************************************************

// Filename : fifo_syn.v

// Author : kingstacker

// Company : School

// Email : kingstacker_work@163.com

// Device : Altera cyclone4 ep4ce6f17c8

// Description : synchronize fifo ;8*8 ;depth shuold be 2^n,otherwise change the clogb2 funtion;

//************************************************

module fifo_syn #(parameter WIDTH = ,DEPTH = )(

//input;

input wire clk, //only one clock;

input wire rst_n,

input wire wr, //wr request;

input wire rd, //rd request;

input wire [WIDTH-:] data, //data in;

//output;

output wire [WIDTH-:] q, //data out;

output wire full, //fifo is full;

output wire empty, //fifo is empty;

output wire [clogb2(DEPTH)-:] usedw //data number in fifo;

);

function integer clogb2 (input integer depth);

begin

for (clogb2=; depth>; clogb2=clogb2+) //depth>1 when you choose depth 2^n;otherwise change it to depth>0;for example depth is 7;

depth = depth >>;

end

endfunction

(* ramstyle = "M9K" *) reg [WIDTH-:] memory [:DEPTH-];

reg [clogb2(DEPTH):] wr_poi; //wr pointer;

reg [clogb2(DEPTH):] rd_poi; //rd pointer;

reg [WIDTH-:] q_r; //reg q;

reg [clogb2(DEPTH)-:] usedw_r; //reg usedw_r;

wire wr_flag; //real wr request;

wire rd_flag; //real rd request;

assign q = q_r;

assign usedw = usedw_r;

assign full = (wr_poi[clogb2(DEPTH)-:]== rd_poi[clogb2(DEPTH)-:]) && (wr_poi[clogb2(DEPTH)] ^ rd_poi[clogb2(DEPTH)] == ); //highest bit is not same but rests bit is same;

assign empty = (wr_poi[clogb2(DEPTH)-:]== rd_poi[clogb2(DEPTH)-:]) && (wr_poi[clogb2(DEPTH)] ^ rd_poi[clogb2(DEPTH)] == ); //every bit is same;

assign wr_flag = ((wr == 'b1) && (full == 1'b0)); //wr enable;

assign rd_flag = ((rd == 'b1) && (empty == 1'b0)); //rd enable;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

wr_poi <= ;

end //if

else begin

wr_poi <= wr_flag ? wr_poi + 'b1 : wr_poi;

memory[wr_poi[clogb2(DEPTH)-:]] <= wr_flag ? data : memory[wr_poi[clogb2(DEPTH)-:]];

end //else

end //always

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

rd_poi <= ;

q_r <= ;

end //if

else begin

rd_poi <= rd_flag ? rd_poi + 'b1 : rd_poi;

q_r <= rd_flag ? memory[rd_poi[clogb2(DEPTH)-:]] : q_r;

end //else

end //always

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

usedw_r <= ;

end //if

else begin

case ({wr_flag,rd_flag})

'b00: begin

usedw_r <= usedw_r;

end

'b10: begin

if (usedw_r == DEPTH-) begin // full;

usedw_r <= usedw_r;

end

else begin

usedw_r <= usedw_r + 'b1;

end

end

'b01: begin

if (usedw_r == ) begin //empty;

usedw_r <= usedw_r;

end

else begin

usedw_r <= usedw_r - 'b1;

end

end

'b11: begin

usedw_r <= usedw_r;

end

default: usedw_r <= ;

endcase //case

end //else

end //always endmodule

以上。

怎么用Verilog语言描述同步FIFO和异步FIFO的更多相关文章

- 同步fifo与异步fifo

参考以下帖子: https://blog.csdn.net/hengzo/article/details/49683707 https://blog.csdn.net/Times_poem/artic ...

- Verilog语言实现并行(循环冗余码)CRC校验

1 前言 (1) 什么是CRC校验? CRC即循环冗余校验码:是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定.循环冗余检查(CRC)是一种数据传输检错功能, ...

- 异步FIFO总结+Verilog实现

异步FIFO简介 异步FIFO(First In First Out)可以很好解决多比特数据跨时钟域的数据传输与同步问题.异步FIFO的作用就像一个蓄水池,用于调节上下游水量. FIFO FIFO是一 ...

- 异步FIFO及verilog原码

这几天看了Clifford E. Cummings的两篇大作<Simulation and Synthesis Techniques for Asynchronous FIFO Design&g ...

- 异步FIFO总结

异步FIFO总结 异步FIFO的基本概念 异步FIFO读写分别采用相互异步的不同时钟,使用异步FIFO可以在两个不同时钟系统之间快速而方便地传输实时数据 FIFO的常见参数 FIFO的宽度:即FIFO ...

- 异步fifo的Verilog实现

一.分析 由于是异步FIFO的设计,读写时钟不一样,在产生读空信号和写满信号时,会涉及到跨时钟域的问题,如何解决? 跨时钟域的问题:由于读指针是属于读时钟域的,写指针是属于写时钟域的,而异步FIFO ...

- Jquery如何序列化form表单数据为JSON对象 C# ADO.NET中设置Like模糊查询的参数 从客户端出现小于等于公式符号引发检测到有潜在危险的Request.Form 值 jquery调用iframe里面的方法 Js根据Ip地址自动判断是哪个城市 【我们一起写框架】MVVM的WPF框架(三)—数据控件 设计模式之简单工厂模式(C#语言描述)

jquery提供的serialize方法能够实现. $("#searchForm").serialize();但是,观察输出的信息,发现serialize()方法做的是将表单中的数 ...

- Verilog 语言 001 --- 入门级 --- 编写一个半加器电路模块

Verilog 语言编写一个 半加器 电路模块 半加器 的电路结构: S = A 异或 B C = A 与 B 1. 程序代码 module h_adder (A, B, SO, CO); input ...

- FPGA基础(verilog语言)——语法篇

verilog语言简介 verilog语言是一种语法类似于c的语言,但是与c语言也有不同之处,比如: 1.verilog语言是并行的,每个always块都是同时执行,而c语言是顺序执行的 2.veri ...

随机推荐

- H5 文字属性

03-文字属性 我是文字 我是文字 abc我是段落 <!DOCTYPE html> <html lang="en"> <head> <me ...

- 11076: 小P的集合 位运算

考虑当只有一个数出现奇数次的时候,我们可以很轻松的知道,把所有的数异或和即可,因为异或运算有一个非常有意思的性质,a^b^a=b 考虑当有两个数(a,b)出现奇数次的时候,我们异或和得到,num=a^ ...

- ASP.NET项目开发

ASP.NET项目开发 1.C/S模式 (client 客户端 server 服务器):QQ.证券.酷狗.旺旺...需要下载响应软件: 工作原理:客户端请求--ASP.net服务器端应用(<-- ...

- Linux提示删除文件cannot remove `文件名': Operation not permitted

Linux系统下删除某个文件时提示如下报错: 执行lsattr命令可以看到隐藏属性-------i--------,如下图: 通过查找资料发现: chattr命令用于改变文件属性.这项指令可改变存放在 ...

- 搭建私服-docker registry

Docke官方提供了Docker Hub网站来作为一个公开的集中仓库.然而,本地访问Docker Hub速度往往很慢,并且很多时候我们需要一个本地的私有仓库只供网内使用.Docker仓库实际上提供两方 ...

- php使用gd库输出中文内容的图片

正如标题所说那样,本文只讨论输出内容全部为中文或者包含中文的情况.如果内容全是字母或者其他字符的话,可以参考这篇博客:生成验证码 问题 此处要注意,标题中为什么要区别windows和linux分别实现 ...

- 【kindle笔记】之 《解忧杂货店》-2018-3-13

[kindle笔记]读书记录-总 <解忧杂货店>-2018-3-13 东野的大ID加上此书的大ID,今天终于在回来天津的火车上一口气读完了. 此前在微信读书上看过这本书,只看了前一部分,感 ...

- [转帖]CentOS 查看系统信息汇总

CentOS 查看系统信息汇总 http://blog.itpub.net/15498/viewspace-2637493/ 感觉应该是 centos相关的 改了下名字 日志文件说明 /var/log ...

- CentOS7安装Jenkins自动化部署maven项目

前言: 最近要弄一个jenkins工具,已经安装好了并且jenkins使用部署项目的流程已经基本走通,上图: 话不多说,开始 第一步:安装jenkins: [ 准备环境: 在centOS7环境上:安装 ...

- python之路-列表、元组、range

一 . 列表 # 列表的定义 列表就是能装对象的对象 在python中用[ ]来描述列表,内部元素用逗号隔开,对数据类型没有要求 索引和切片 lst = ["天龙八部", &quo ...