FPGA CFGBVS 管脚接法

说明

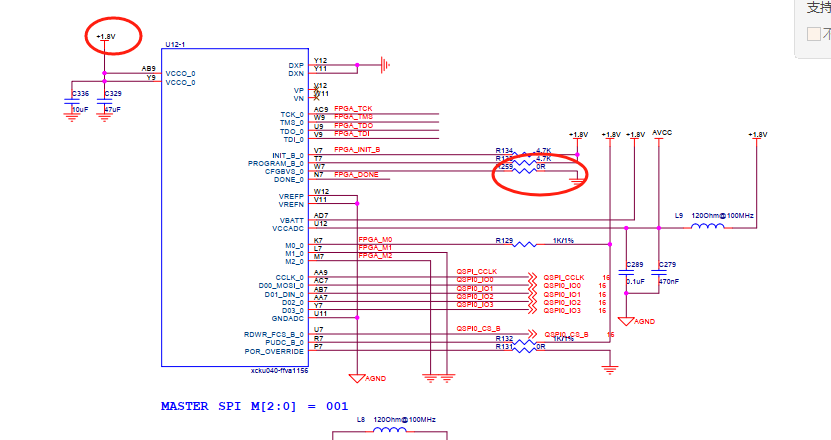

新设计了1个KU040 FPGA板子,回来之后接上JTAG FPGA不识别。做如下检查:

1、电源测试点均正常;

2、查看贴片是否有漏焊,检查无异常,设计上NC的才NC;

3、反复检查JTAG接线是否异常,贴片是否异常;

上述检查均无问题,开始查看原理图,逐个对照XILINX手册进行研究。

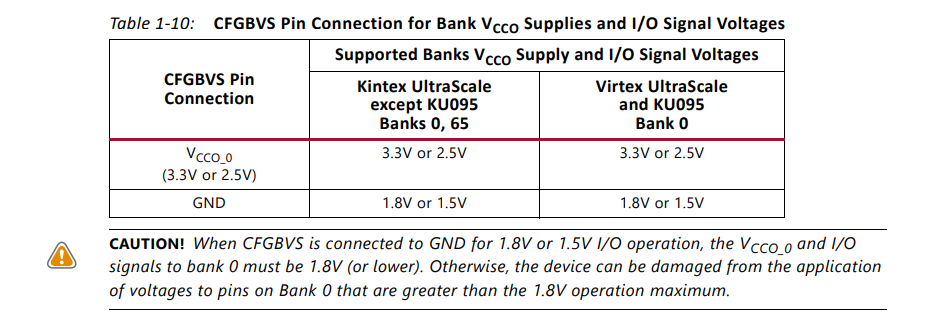

其中发现 CFGBVS 在设计图中接了地,对照XILINX 手册 https://www.amd.com/content/dam/xilinx/support/documents/user_guides/ug570-ultrascale-configuration.pdf

In the Kintex UltraScale and Virtex UltraScale FPGAs, the configuration banks voltage select

(CFGBVS) pin must be set to High or Low to determine the I/O voltage support for the pins

in bank 0, and for the multi-function pins in bank 65 when they are used during

configuration. The CFGBVS is a logic input pin referenced between VCCO_0 and GND. When

the CFGBVS pin is connected to the VCCO_0 supply of 3.3V or 2.5V, the configuration I/O

support operation at 3.3V or 2.5V. When the CFGBVS pin is connected to GND, the

configuration I/O support operation at 1.8V or 1.5V. There is no CFGBVS pin in the Artix

UltraScale+, Kintex UltraScale+, and Virtex UltraScale+ FPGAs because their configuration

I/O only support operation at 1.8V or 1.5V.

Configuration is not supported below the minimum recommended operating voltage for

1.5V as specified in the data sheet. The CFGBVS pin setting determines the I/O voltage

support for bank 0 at all times, before, during, and after configuration. CFGBVS similarly

controls the voltage tolerance on bank 65, but only during configuration.

也就是说,这里原理图 CFGBVS 接地肯定是不对的,必须拉高到3.3V,还好留了1个0欧姆电阻在这里 还可以飞线补救一下。

FPGA CFGBVS 管脚接法的更多相关文章

- Quartus II中FPGA的管脚分配保存方法

一.摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总. 二.管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按 ...

- (转载)Quartus II中FPGA的管脚分配保存方法(Quartus II)

一.摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总. 二.管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择"Assignments ->Pin&quo ...

- 4.FPGA芯片管脚解释

用户I/O:不用解释了. 配置管脚: MSEL[1:0] 用于选择配置模式,比如AS.PS等. DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚. DCLK FPGA串行时钟输出 ...

- quartus2中FPGA管脚分配保存方法(转)

一.摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总. 二.管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按 ...

- FPGA研发之道(25)-管脚

管脚是FPGA重要的资源之一,FPGA的管脚分别包括,电源管脚,普通I/O,配置管脚,时钟专用输入管脚GCLK等. 本文引用地址:http://www.eepw.com.cn/article/2664 ...

- FPGA Timing笔记

很多FPGA工程师都会遇到timing的问题,如何让FPGA跑到更快的处理频率是永久话题.决定FPGA的timing关键是什么?如何才能跑到更快的频率呢? A. 第一步需要了解FPGA的timing路 ...

- 【小梅哥FPGA进阶学习之旅】基于Altera FPGA 的DDR2+千兆以太网电路设计

DDR2电路设计 在高速大数据的应用中,高速大容量缓存是必不可少的硬件.当前在FPGA系统中使用较为广泛的高速大容量存储器有经典速度较低的单数据速率的SDRAM存储器,以及速度较高的双速率DDR.DD ...

- 第一个FPGA工程—LED流水灯

这一章我们来实现第一个FPGA工程-LED流水灯.我们将通过流水灯例程向大家介绍一次完整的FPGA开发流程,从新建工程,代码设计,综合实现,管脚约束,下载FPGA程序.掌握本章内容,大家就算正式的开始 ...

- 如何新建Quartus工程—FPGA入门教程【钛白Logic】

这一章我们来实现第一个FPGA工程—LED流水灯.我们将通过流水灯例程向大家介绍一次完整的FPGA开发流程,从新建工程,代码设计,综合实现,管脚约束,下载FPGA程序.掌握本章内容,大家就算正式的开始 ...

- FPGA与图像处理

用FPGA做图像处理最关键的一点优势就是:FPGA能进行实时流水线运算,能达到最高的实时性.因此在一些对实时性要求非常高的应用领域,做图像处理基本就只能用FPGA.例如在一些分选设备中图像处理基本上用 ...

随机推荐

- .NET周刊【5月第2期 2024-05-12】

国内文章 C#在工业数字孪生中的开发路线实践 https://mp.weixin.qq.com/s/b_Pjt2oii0Xa_sZp_9wYWg 这篇文章探讨了C#在工业数字孪生技术中的应用,介绍了三 ...

- PageOffice实现文件在线安全预览——禁止编辑、下载、复制等

实际应用中,很多时候不仅需要在线编辑文件,还需要在线安全预览文件,要求不能复制.下载.另存到本地等情况.pageoffice可以实现文件在线安全预览,禁止:编辑.复制.粘贴.右键菜单.选择.下载.另存 ...

- (二)Redis 数据类型与结构

1.值的数据类型 Redis "快"取决于两方面,一方面,它是内存数据库,另一方面,则是高效的数据结构.Redis 键值对中值的数据类型,也就是数据的保存形式有5种:String( ...

- AIRIOT答疑第6期|如何使用二次开发引擎?

灵活扩展,满足客户定制化需求 AIRIOT物联网低代码平台提供丰富的前端.后台服务二次开发接口,具备灵活的组件服务部署与管理能力,对任何功能模块进行二次开发,满足客户各类二次开发需求.支持多种 ...

- FFmpeg开发笔记(二十二)FFmpeg中SAR与DAR的显示宽高比

<FFmpeg开发实战:从零基础到短视频上线>一书提到:通常情况下,在视频流解析之后,从AVCodecContext结构得到的宽高就是视频画面的宽高.然而有的视频文件并非如此,如果按照A ...

- Django模型层的QuerySet对象

def index(request): # 查询数据,返回QuerySet对象books books=Book.objects.filter(id__gte=1) # 打印books, 是一个Quer ...

- 在 Flask 项目中配置 Session:简明指南

在 Flask 项目中配置 Session:简明指南 本文介绍如何在 Flask 项目中配置会话 1. Flask 内置会话 Flask 自带会话管理功能,使用客户端 Cookie 存储会话数据.默认 ...

- const与指针的组合

① const int *p; //指向一个整型常量的指针,p可变,p指向的对象不可变. ② int const *p; //同上. ③ int * const p; //p不可变,p指向的对象可变( ...

- 微信小程序跳转重新加载目标页

可用于在首次进入到小程序后就执行性了首页的onLoad方法,等你再去点击其它页面再回来的时候就不会加载onLoad了,比如你跳到登录页后再返回到首页会发现首页啥数据都没加载,所以你在登录那边进行跳转的 ...

- vue 的时间格式化

大江东去,浪淘尽,千古风流人物.故垒西边,人道是,三国周郎赤壁.乱石穿空,惊涛拍岸,卷起千堆雪.江山如画,一时多少豪杰.遥想公瑾当年,小乔初嫁了,雄姿英发.羽扇纶巾,谈笑间,樯橹灰飞烟灭.故国神游,多 ...