第十一章 ZYNQ-MIZ701 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将结果打印输出到串口终端显示。

涉及到AXI BRAM Controller 和 Block Memery Generator等IP的使用。

本系列文章尽可能的让每一个实验都相对独立,过程尽可能保证完整性,保证实验的可重现性。 但是用到的模块或者IP的具体作用和用法不保证都重复详细的介绍。

本文所使用的开发板是Miz702 PC 开发环境版本:Vivado 2015.4 Xilinx SDK 2015.4

11.0本章难度系数★★☆☆☆☆☆

11.1 搭建硬件工程

Step1:新建一个名为为Miz701_sys的工程

Step2:选择RTL Project 勾选Do not specify source at this time

Step3:选择xc7z010clg400-1为开发器件。

Step4:单击Finish

11.2使用IP Integrator创建硬件系统

Step1:单击Create Block Design

Step2:输入system

Step3:单击下图中 添加IP按钮

添加IP按钮

Step4:搜素单词z选择ZYNQ7 Processing System,然后双击

Step5:添加进来了ZYNQ CPU IP,然后双击对其进行配置。

Step6:修改输入时钟为50MHZ,PL端频率FCLK_CLK0为100MHZ。

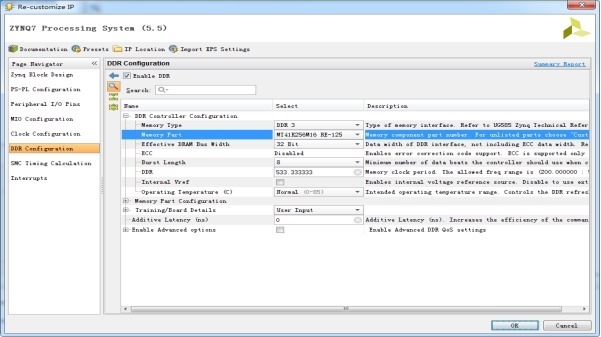

Step7:修改内存型号为MT41K256M16 RE-125。

Step8:在MIO configuration选项中,勾选添加UART1接口。

Step9: 在PL-PS Configuration下,选中 GP0和GP1然后 点击ok。

Step10:单击Run Block Automation进行智能布线。

Step11:直接单击OK

Step12:在你点击了OK后,你会发现DDR以及FICED_IO自动的延伸出来。

Step13:连线的作用就是把PS的时钟可以接入PL部分,当然这里我们暂时用不到PL部分的资源。在Block文件中,我们迚行连线,将鼠标放在引脚处,鼠标变成铅笔后迚行拖拽,连线如下图所示:

Step14:点击,Add IP,连续添加两个 AXI BRAM Controller

Step15:分别双击AXI BRAM Controller模块,把number of BRAM interfaces 全部修改成1

Step16:点击ADD IP,添加Block Memory Generator

Step17:双击Block Memory Generator ,修改Memory Type。

Step18:点击run Connection Automation,把axi_bram_ctrl_1的S_AXI端口的连接目标修改为如图所示:

Step19:点击重新布局,生成好的硬件框架如下

Step20:点击Address Editor 可以看到系统已经为我们自动分配好了正确的地址

Step21: 右击 system.bd, 单击Generate Output Products

Step22:支部操作会产生执行、仿真、综合的文件

Step23:右击system.bd 选择 Create HDL Wrapper 这步的作用是产生顶层的HDL文件

Step24:选择Leave Let Vivado manager wrapper and auto-update 然后单击OK

Step25:执行->产生bit文件

11.3导出SOC硬件到SDK

Step1:File->Export->Export Hardware

Step2:勾选Include bitstream 直接单击OK

Step3:File->Launch SDK加载到SDK

Step4:单击OK

11.4 软件工程

Step1:打开的SDK界面如下,这里的信息是和硬件相关的,例如在Address Map 这一栏下可以看到axi_bram_ctrl_0和刚刚在vavado Address Editor下的地址是一致的

Step2: 新建一个名为BRAM_Test的空的工程,并且新建一个main.c文件,添加如下代码。

|

/* * mai.c * * Created on: 2016年6月26日 * Author: Administrator */ #include <stdio.h> #include "xil_io.h" //这个头文件下面包含很重要的IO读写函数 #include "xparameters.h" //这个头文件里把硬件的地址映射等参数都写成了宏定义方便使用 //void print(char *str); int main() { int num; int rev; xil_printf("------The test is start...------\n\r"); //XPAR_AXI_BRAM_CTRL_0_S_AXI_BASEADDR是axi_bram_ctrl_0的地址,Xil_Out32通过控制axi_bram_ctrl_0,向blk_mem_gen_0写数据 for( num=0; num<15; num++ ) { Xil_Out32(XPAR_BRAM_0_BASEADDR + num*4, 0x10000000+num); // } //XPAR_AXI_BRAM_CTRL_1_S_AXI_BASEADDR是axi_bram_ctrl_1的地址,Xil_In32 通过控制axi_bram_ctrl_0,把blk_mem_gen_0里的数据读出来 //PS和PL可以在blk_mem_gen_0里共享数据 for( num=0; num<15; num++ ) { rev = Xil_In32(XPAR_BRAM_0_BASEADDR + num*4); xil_printf( "The data at %x is %x \n\r",XPAR_BRAM_0_BASEADDR + num*4,rev); } xil_printf("------The test is end!------\n\r"); return 0; } |

11.5 测试结果

串口终端打印输出信息如下:

------The test is start...------

The data at 80000000 is 10000000

The data at 80000004 is 10000001

The data at 80000008 is 10000002

The data at 8000000C is 10000003

The data at 80000010 is 10000004

The data at 80000014 is 10000005

The data at 80000018 is 10000006

The data at 8000001C is 10000007

The data at 80000020 is 10000008

The data at 80000024 is 10000009

The data at 80000028 is 1000000A

The data at 8000002C is 1000000B

The data at 80000030 is 1000000C

The data at 80000034 is 1000000D

The data at 80000038 is 1000000E

------The test is end!------

11.6 本章小结

本文通过PS端把数据写入到PL端的BRAM,然后从而又把数据从PL端读到PS端,从而简单的实现了PL和PS的数据交互和共享。

第十一章 ZYNQ-MIZ701 PS读写PL端BRAM的更多相关文章

- 第十二章 ZYNQ-MIZ702 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- 第十一章 ZYNQ-MIZ702 DDR3 PS读写操作方案

本编文章的目的主要用简明的方法在纯PS里对DDR3进行读写. 本文所使用的开发板是Miz702 PC 开发环境版本:Vivado 2015.4 Xilinx SDK 2015.4 11.0本章难度 ...

- Vivado设计二:zynq的PS访问PL中的自带IP核(基于zybo)

1.建立工程 首先和Vivado设计一中一样,先建立工程(这部分就忽略了) 2.create block design 同样,Add IP 同样,也添加配置文件,这些都和设计一是一样的,没什么区别. ...

- ZYNQ笔记(1):PL端——led灯

ZYNQ分为PS和PL,此博客实际上是FPGA中一个完整的FPGA工程的创建. PS:处理系统 (Processing System) 即ARM的Soc部分 PL:可编程逻辑(Programable ...

- [原创]基于Zynq PS与PL之间寄存器映射 Standalone & Linux 例程

基于Zynq PS与PL之间寄存器映射 Standalone & Linux 例程 待添加完善中

- 使用axi_datamover完成ZYNQ片内PS与PL间的数据传输

分享下PS与PL之间数据传输比较另类的实现方式,实现目标是: 1.传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送: 2.PL端接口为FIFO接口: PS到PL的数据传输流程: PS到 ...

- Zynq PS和PL间的连接

跨越PS和PL的信号 AXI总线.EMIO.其他(看门狗.重启信号.中断信号.DMA接口信号) AXI标准 AXI(高级可扩展接口)是ARM AMBA的一部分.AMBA总线主要用于片上系统.AXI总线 ...

- 第十章 ZYNQ-MIZ701 DDR3 PS读写操作方案

本编文章的目的主要用简明的方法在纯PS里对DDR3进行读写. 本文所使用的开发板是Miz701 PC 开发环境版本:Vivado 2015.4 Xilinx SDK 2015.4 10.0本章难度 ...

- zedboard如何从PL端控制DDR读写(七)

前面已经详细介绍了从PL端如何用AXI总线去控制DDR的读写,并且从AXI_BRESP的返回值来看,我们也是成功写入了的.但是没有通过别的方式来验证写入的数据的话,总是感觉差了点什么. 今天试了一把从 ...

随机推荐

- bash 基础之五 条件测试、read

一 条件选择if语句 顺序执行:逐条运行: 选择执行: 代码有一个分支:条件满足时才会执行: 两个或以上的分支:只会执行其中一个满足条件的分支: 循环执行:代码片断(循环体)要执行0.1或多个来回: ...

- 从TCP到Socket,彻底理解网络编程是怎么回事

进行程序开发的同学,无论Web前端开发.Web后端开发,还是搜索引擎和大数据,几乎所有的开发领域都会涉及到网络编程.比如我们进行Web服务端开发,除了Web协议本身依赖网络外,通常还需要连接数据库,而 ...

- err="etherbase address must be explicitly specified"

如果要初始化区块链的话就用创始区块 如果通过创世区块来初始化区块链的话,首先需要一个初始化区块链的json文件,如下. { "config": { "chainId& ...

- BufferedWriter中write与close函数使用

BufferedWriter 是一个缓冲字符输出流,可以将要输出的内容先缓冲到一个字符数组中,等字符数组满了才一次性写到输出流内,默认的字符数组长度为8192.使用BufferedWriter 时需要 ...

- Qt编写自定义控件31-面板仪表盘控件

一.前言 在Qt自定义控件中,仪表盘控件是数量最多的,写仪表盘都写到快要吐血,可能是因为各种工业控制领域用的比较多吧,而且仪表盘又是比较生动直观的,这次看到百度的echart中有这个控件,所以也来模仿 ...

- 升级系统中的java到1.8版本

(1).安装或升级java,并配置环境变量 注意:此处分为yum安装与rpm安装,区别在于yum安装省事但配置麻烦,rpm安装麻烦但配置省事. 1)yum安装 在安装前可以使用yum list ins ...

- [C++]数据结构:线性表之顺序表

1 顺序表 ADT + Status InitList(SeqList &L) 初始化顺序表 + void printList(SeqList L) 遍历顺序表 + int ListLengt ...

- MySQL数据库相关资料

python 全栈开发,Day60(MySQL的前戏,数据库概述,MySQL安装和基本管理,初识MySQL语句) python 全栈开发,Day61(库的操作,表的操作,数据类型,数据类型(2),完整 ...

- JavaScript 真值和假值

常见的假值有 值 说明 var a=false; 值为假 var a =0; 值为0 var a=''; 值为空 var a=10/'abc' 算式错误 var a; 未赋值变量 常见的真值有 ...

- 解决element-ui按需引入不了Scrollbar的问题

一.报错原因 在我想按需引入element-ui时,突然报错: 这个报错来的有点措不及防.明明在页面当中能够使用,为仕么在单独引入时却不能引用了,真是百思不得其解. 经过在百度上的查找才知道,原来Sc ...