串口接收端verilog代码分析

串口接收端verilog代码分析

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/05/23 16:14:30

// Design Name:

// Module Name: uart_rx

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module uart_rx( input wire clk,

input wire rxd,

output reg [:]data_i,

output wire receive_ack ); reg [:] data_i = ; localparam IDLE = ,

RECEIVE = ,

RECEIVE_END = ; reg [:]cur_st = ;

reg [:]nxt_st = ;

always @(posedge clk)

begin

cur_st <= nxt_st;

end always @(*)

begin

nxt_st = cur_st; case(cur_st) IDLE:

begin

if(!rxd) //当从接收端口上进来的数据开始为0时,即启动接收

nxt_st = RECEIVE;

end RECEIVE:

begin

if(count == )

nxt_st = RECEIVE_END;

end RECEIVE_END:

begin

nxt_st = IDLE;

end default:

begin

nxt_st = IDLE;

end endcase end reg [:]count = ;

always @(posedge clk)

begin

if(cur_st == RECEIVE)

count <= count + ;

else if(cur_st == IDLE || cur_st == RECEIVE_END)

count <= ;

end //当前状态为接收状态时,rxd 信号线上的数据存储在data_i的最高位

//同时data_i 的数据总体右移一位

always @(posedge clk)

begin

if(cur_st == RECEIVE)

begin

data_i[:] <= data_i[:];

data_i[] <= rxd; // rxd 传过来什么数据, data_i上立马显示什么数据,因为是从端口采集到的数据

end end assign receive_ack = (cur_st == RECEIVE_END) ? : ; endmodule /* add_force {/uart_rx/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/uart_rx/rxd} -radix hex {1 0ns} {0 300ns} {1 400ns} {0 500ns} {1 600ns} {0 700ns} {1 800ns} {0 900ns} {1 1000ns} */

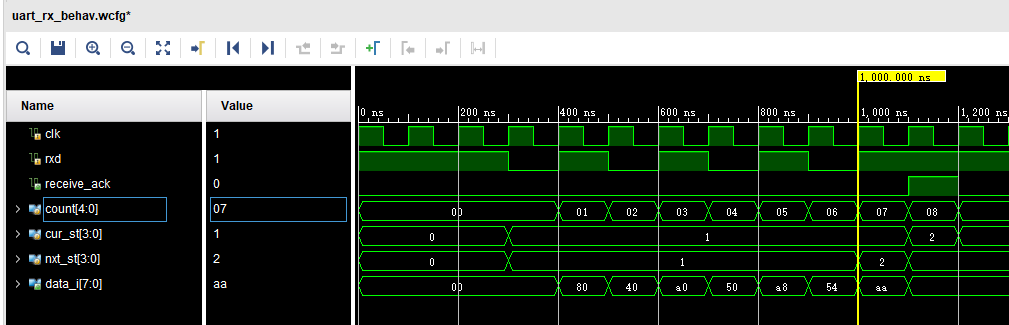

仿真结果:

注意:

分析寄存器的更新一定要结合时钟沿,然后寄存器在时钟沿前后的变化状态。

串口接收端verilog代码分析的更多相关文章

- 串口发送端verilog代码分析

串口发送端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- verilog 代码分析与仿真

verilog 代码分析与仿真 注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值 边沿检测 module signal_test( input wire cmos_pcl ...

- Verilog代码规范I

Verilog代码规范I "规范"这问题 "规范"这个富含专业气息的词汇(个人感觉),其实规范这种东西,就是大家都约定熟成的东西,一旦你不遵守这个东西,专业人士 ...

- Linux内核中的GPIO系统之(3):pin controller driver代码分析

一.前言 对于一个嵌入式软件工程师,我们的软件模块经常和硬件打交道,pin control subsystem也不例外,被它驱动的硬件叫做pin controller(一般ARM soc的datash ...

- Bluez SPP实现代码分析(转)

源:http://blog.csdn.net/walkingman321/article/details/7218705 本文分析蓝牙协议栈中蓝牙转串口(SPP)部分的实现. 1. 基本概念 Blu ...

- ISD9160学习笔记05_ISD9160语音识别代码分析

前言 语音识别是特别酷的功能,ISD9160的核心卖点就是这个语音识别,使用了Cybron VR 算法. 很好奇这颗10块钱以内的IC是如何实现人家百来块钱的方案.且听如下分析. 本文作者twowin ...

- 2017-2018-2 《网络对抗技术》 20155322 Exp4 恶意代码分析

[-= 博客目录 =-] 1-实践目标 1.1-实践介绍 1.2-实践内容 1.3-实践要求 2-实践过程 2.1-Mac下网络监控 2.2-Windows下网络监控 2.3-Mac下恶意软件分析 2 ...

- STM32F103片外运行代码分析

STM32F103片外运行代码分析 STM32F103有三种启动方式: 1.从片内Flash启动: 2.从片内RAM启动: 3.从片内系统存储器启动,内嵌的自举程序,用于串口IAP. 无法直接在片外N ...

- Linux内核中的GPIO系统之(3):pin controller driver代码分析--devm_kzalloc使用【转】

转自:http://www.wowotech.net/linux_kenrel/pin-controller-driver.html 一.前言 对于一个嵌入式软件工程师,我们的软件模块经常和硬件打交道 ...

随机推荐

- Go 安装 sqlite3驱动报错

问题:最近在使用Go做一个博客示例,在使用go get 安装 sqlIite3的驱动遇到下面的问题(cc1.exe: sorry, unimplemented: 64-bit mode not com ...

- LeetCode--023--合并K个排序链表

合并 k 个排序链表,返回合并后的排序链表.请分析和描述算法的复杂度. 示例: 输入: [ 1->4->5, 1->3->4, 2->6 ] 输出: 1-&g ...

- python几种常见的模块安装方法

1. 在线安装 1.1 在命令提示符中运行 pip install package_name 指令 注:具体前置步骤和教程:http://www.cnblogs.com/jfl-xx/p/72895 ...

- Makefile 宏定义 -D

一.GCC编译器中使用: -D macro=string,等价于在头文件中定义:#define macro string. 例如:-D TRUE=true,等价于:#define ...

- 错误:com.mysql.jdbc.exceptions.jdbc4.MySQLSyntaxErrorException

Caused by: com.mysql.jdbc.exceptions.jdbc4.MySQLSyntaxErrorException: Table 'hdjyproj.t_userinfo' do ...

- 网络编程,socket

1.网络编程 网络: TCP/IP 彼此之间遵守协议和规范!之间才能产生通信! IP: 每个人都有自己的身份证号! 用来标识我们网络中每一台计算机! IP地址= 网络地址 +主机地址 网络地址 :标识 ...

- python单例(重点)

单例 目标 单例设计模式 __new__ 方法 Python 中的单例 01. 单例设计模式 设计模式 设计模式 是 前人工作的总结和提炼,通常,被人们广泛流传的设计模式都是针对 某一特定问题的成熟的 ...

- list的相关函数

# ### 列表相关的函数 # (1) append ''' 功能:向列表的末尾添加新的元素 格式:列表.append(值) 返回值:None 注意:新添加的值在列表的末尾,该函数直接操作原有列表 ' ...

- wc语法2

wc命令的功能为统计指定文件中的字节数.字数.行数, 并将统计结果显示输出. 语法:wc [选项] 文件… 说明:该命令统计给定文件中的字节数.字数.行数.如果没有给出文件名,则从标准输入读取.wc同 ...

- 剑指Offer 27. 字符串的排列 (字符串)

题目描述 输入一个字符串,按字典序打印出该字符串中字符的所有排列.例如输入字符串abc,则打印出由字符a,b,c所能排列出来的所有字符串abc,acb,bac,bca,cab和cba. 输入描述: 输 ...