红外解码编码学习----verilog

在设计中运用红外遥控器可以很好的解决按键缺少的问题,还可以方便的控制产品。

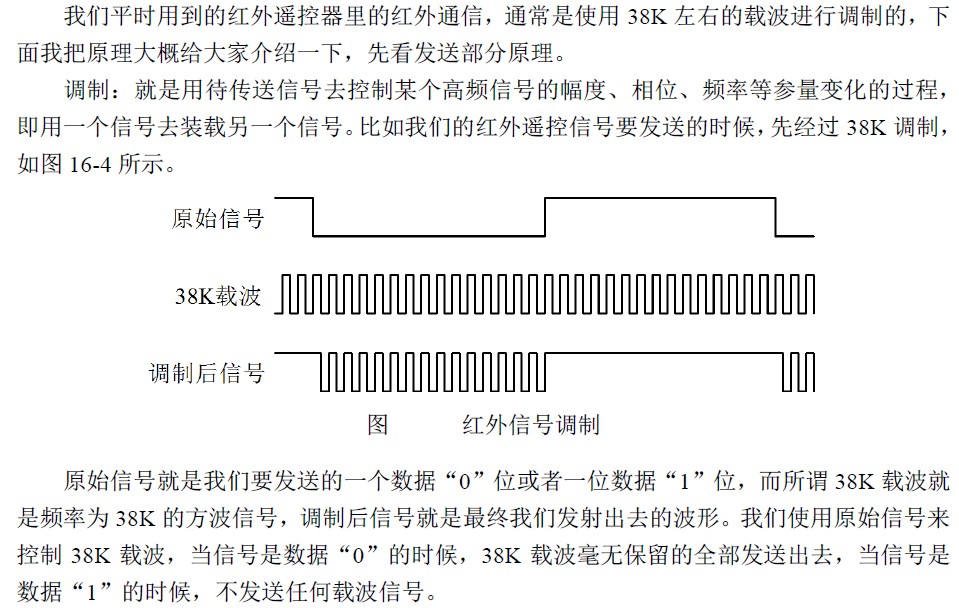

红外发射部分:

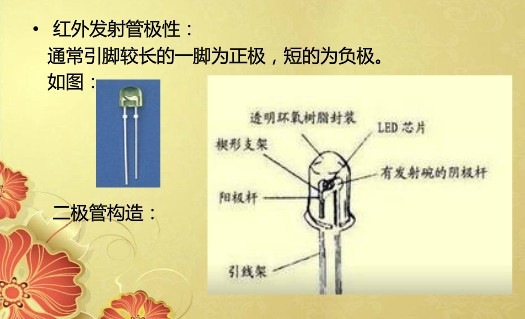

红外发射管:

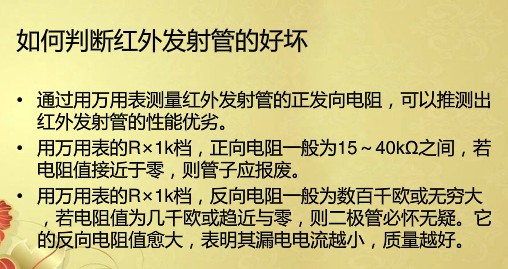

判断红外发射管的好坏

:

:

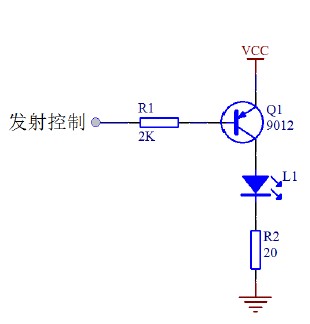

电路原理图:

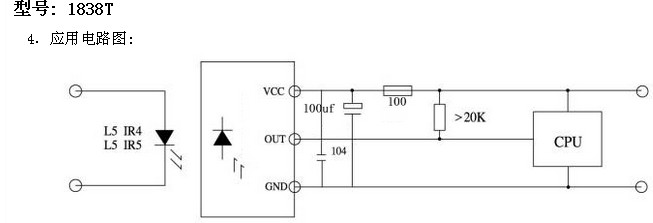

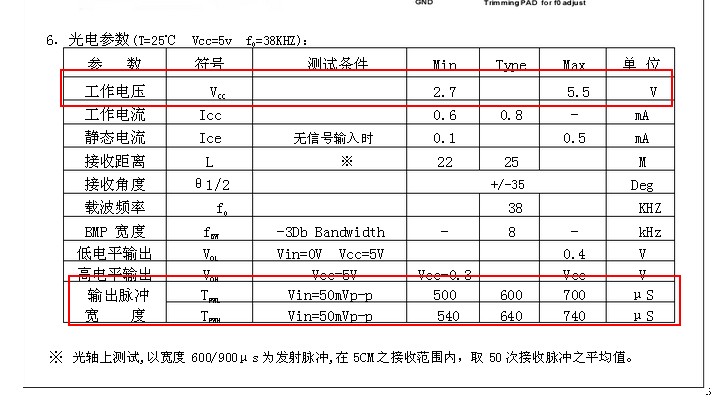

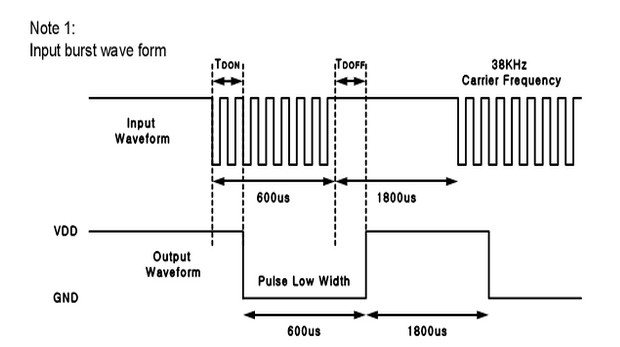

接收部分:

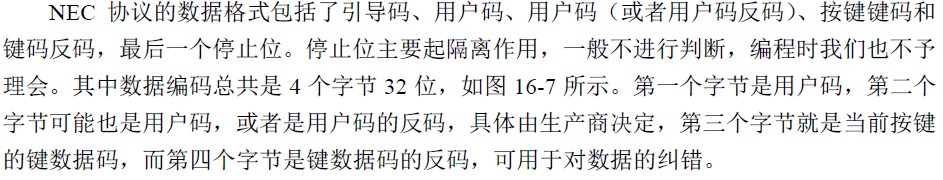

传输的NEC协议:

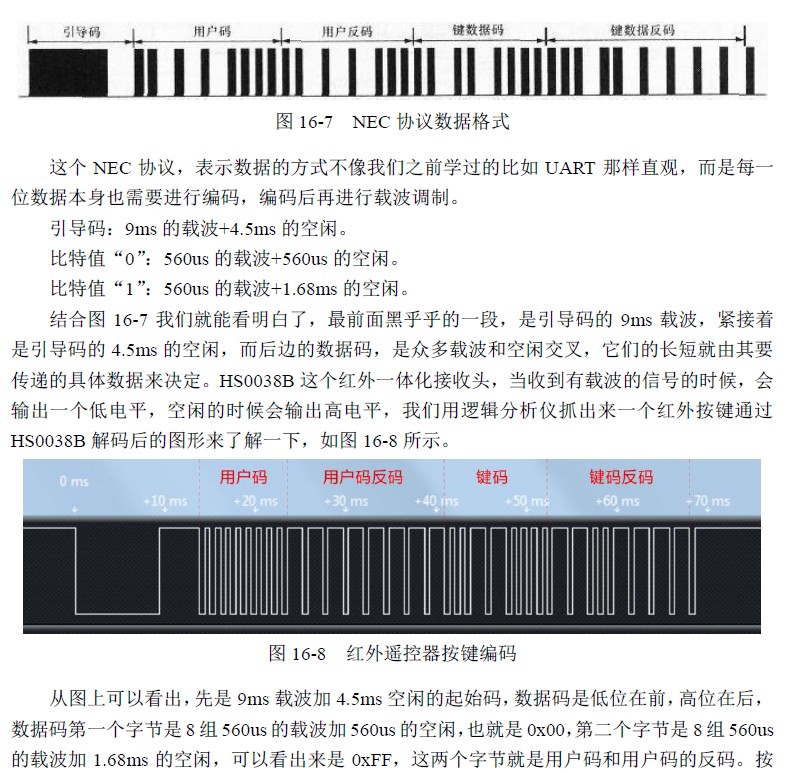

本实验电路:

verilog 程序:

发送程序:

/********************************Copyright**************************************

**----------------------------File information--------------------------

** File name :IR_send.v

** CreateDate :2015.06

** Funtions :红外信号的发送程序,发送格式:引导码+8bit用户码+8bit用户反码(或者用户反码)+8bit数据码+8bit用户反码+结束码

** Operate on :M5C06N3L114C7

** Copyright :All rights reserved.

** Version :V1.0

**---------------------------Modify the file information----------------

** Modified by :

** Modified data :

** Modify Content:

*******************************************************************************/

module IR_send (

clk,

rst_n,

key_1,

key_2,

IR_out,

led_1,

led_2,

led_3,

led_4

// testdata

);

input clk; //24M/20m

input rst_n;

input key_1;

input key_2;

output IR_out;

output reg led_1;

output reg led_2;

output led_3;

output led_4;

// output [7;0] testdata;

//-------------------//

`define CLK_20M

// `define CLK_24M

// `define CLK_50M

`ifdef CLK_20M

parameter t_38k = 'd526;

parameter t_38k_half = 'd263;

parameter t_9ms = 'd179999;

parameter t_4_5ms = 'd89999;

parameter t_13_5ms = 'd269999;

parameter t_560us = 'd11199;

parameter t_1_12ms = 'd22399;

parameter t_1_68ms = 'd33599;

parameter t_2_24ms = 'd44799;

`endif

`ifdef CLK_24M

parameter t_38k = 'd630;

parameter t_38k_half = 'd315;

parameter t_9ms = 'd215999;

parameter t_4_5ms = 'd107999;

parameter t_13_5ms = 'd323999;

parameter t_560us = 'd13439;

parameter t_1_12ms = 'd26879;

parameter t_1_68ms = 'd40319;

parameter t_2_24ms = 'd53759;

`endif

`ifdef CLK_50M

parameter t_38k = 'd1315;

parameter t_38k_half = 'd657;

parameter t_9ms = 'd449999;

parameter t_4_5ms = 'd224999;

parameter t_13_5ms = 'd674999;

parameter t_560us = 'd27999;

parameter t_1_12ms = 'd55999;

parameter t_1_68ms = 'd83999;

parameter t_2_24ms = 'd111999;

`endif

parameter DATA_USER = 'h00;

//---------------------------------//

//分频38Khz时钟

reg [:] cnt1;

wire clk_38k;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt1 <= ;

end

else if(cnt1 == t_38k)

begin

cnt1 <= ;

end

else cnt1 <= cnt1 + ;

end

assign clk_38k = (cnt1<t_38k_half)?:;

//-------------------------------------------//

// wire key_1_flg;

// wire key_2_flg;

// key_shake U1(

// .clk_100M(clk),

// .rst_n(rst_n),

//

// .key_in(key_1),

// .key_out(key_1_flg)

// );

//

// key_shake U2(

// .clk_100M(clk),

// .rst_n(rst_n),

//

// .key_in(key_2),

// .key_out(key_2_flg)

// );

reg [:] key_1_flag;

wire key_1_neg;

wire key_1_pos;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

key_1_flag <= 'b000;

end

else

begin

key_1_flag <= {key_1_flag[:],key_1};

end

end

assign key_1_pos = (key_1_flag[:]== 'b01);

reg [:] key_2_flag;

wire key_2_neg;

wire key_2_pos;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

key_2_flag <= 'b000;

end

else

begin

key_2_flag <= {key_2_flag[:],key_2};

end

end

assign key_2_pos = (key_2_flag[:] == 'b01);

//------------------------------------------//

parameter IDEL = 'D0; //初始化状态,等待发送命令

parameter START = 'D1; //开始发送引导码

parameter SEND_USER = 'D2; //发送用户码

parameter SEND_UNUSER= 'D3; //发送用户反码

parameter SEND_DATA = 'D4; //发送数据

parameter SEND_UNDATA= 'D5; //发送数据反码

parameter FINISH = 'D6; //发送结束码

parameter FINISH_1 = 'D7; //发送结束

reg [:] state;

reg start_en;

wire start_over;

reg zero_en;

wire zero_over;

reg one_en;

wire one_over;

reg finish_en;

wire finish_over;

reg sendover;

reg [:] shiftdata;

reg [:] i;

reg [:] DATA;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

state <= IDEL;

start_en <= ;

zero_en <= ;

one_en <= ;

finish_en <= ;

sendover <= ;

shiftdata <= ;

i <= ;

DATA <= 'D0;

led_1 <= ;

led_2 <= ;

end

else

begin

case(state)

IDEL:

begin

start_en <= ;

zero_en <= ;

one_en <= ;

finish_en <= ;

sendover <= ;

shiftdata <= ;

i <= ;

DATA <= 'd0;

if(key_1_pos)

begin

state <= START;

DATA <= 'd1;

end

else if(key_2_pos)

begin

state <= START;

DATA <= 'd2;

end

else state <= IDEL;

end

START: //发送引导码

begin

if(start_over)

begin

start_en <= ;

state <= SEND_USER;

shiftdata <= DATA_USER;

end

else

begin

start_en <= ;

state <= START;

end

end

SEND_USER:

begin

// led_3 <= 1;

if((i==)&&(one_over||zero_over)) //结束位

begin

i <=;

shiftdata <= ~DATA_USER;

state <= SEND_UNUSER;

one_en <= ;

zero_en <= ;

end

else

begin

if(zero_over||one_over) //1bit发送结束

begin

i <= i + ;

one_en <= ;

zero_en <= ;

end

else if(shiftdata[i])

begin

one_en <= ;

end

else if(!shiftdata[i]) zero_en <= ;

else

begin

i <= i ;

one_en <= one_en;

zero_en <= zero_en;

end

end

end

SEND_UNUSER:

begin

led_1 <= ~led_1;

if((i==)&&(one_over||zero_over)) //结束位

begin

i <=;

state <= SEND_DATA;

shiftdata <= DATA;

one_en <= ;

zero_en <= ;

end

else

begin

if(zero_over||one_over) //1bit发送结束

begin

i <= i + ;

one_en <= ;

zero_en <= ;

end

else if(shiftdata[i])

begin

one_en <= ;

end

else if(!shiftdata[i]) zero_en <= ;

else

begin

i <= i ;

one_en <= one_en;

zero_en <= zero_en;

end

end

end

SEND_DATA:

begin

led_2 <= ~led_2 ;

if((i==)&&(one_over||zero_over)) //结束位

begin

i <=;

state <= SEND_UNDATA;

shiftdata <= ~DATA;

one_en <= ;

zero_en <= ;

end

else

begin

if(zero_over||one_over) //1bit发送结束

begin

i <= i + ;

one_en <= ;

zero_en <= ;

end

else if(shiftdata[i])

begin

one_en <= ;

end

else if(!shiftdata[i]) zero_en <= ;

else

begin

i <= i ;

one_en <= one_en;

zero_en <= zero_en;

end

end

end

SEND_UNDATA:

begin

if((i==)&&(one_over||zero_over)) //结束位

begin

i <=;

shiftdata <= ;

state <= FINISH;

one_en <= ;

zero_en <= ;

end

else

begin

if(zero_over||one_over) //1bit发送结束

begin

i <= i + ;

one_en <= ;

zero_en <= ;

end

else if(shiftdata[i])

begin

one_en <= ;

end

else if(!shiftdata[i]) zero_en <= ;

else

begin

i <= i ;

one_en <= one_en;

zero_en <= zero_en;

end

end

end

FINISH:

begin

if(finish_over)

begin

finish_en <= ;

state <= FINISH_1;

end

else

begin

finish_en <= ;

state <= FINISH;

end

end

FINISH_1:

begin

sendover <= ;

state <= IDEL;

end

default: state <= IDEL;

endcase

end

end

//----------------------------------------------//

//引导码,9ms载波加4.5ms空闲

reg [:] cnt2;

wire start_flag;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt2 <= ;

end

else if(start_en)

begin

if(cnt2 >= t_13_5ms) cnt2 <= t_13_5ms+;

else cnt2 <= cnt2 + ;

end

else cnt2 <= ;

end

assign start_over = (cnt2 == t_13_5ms)?:;

assign start_flag = (start_en&&(cnt2 <= t_9ms))?:;

//----------------------------------------------//

//比特0, 560us载波 + 560us空闲

reg [:] cnt3;

wire zero_flag;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt3 <= ;

end

else if(zero_en)

begin

if(cnt3 >= t_1_12ms) cnt3 <= t_1_12ms+;

else cnt3 <= cnt3 + ;

end

else cnt3 <= ;

end

assign zero_over = (cnt3 == t_1_12ms)?:;

assign zero_flag = (zero_en&&(cnt3 <= t_560us))?:;

//----------------------------------------------//

//比特1, 560us载波 + 1.68ms空闲

reg [:] cnt4;

wire one_flag;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt4 <= ;

end

else if(one_en)

begin

if(cnt4 >= t_2_24ms) cnt4 <= t_2_24ms+;

else cnt4 <= cnt4 + ;

end

else cnt4 <= ;

end

assign one_over = (cnt4 == t_2_24ms)?:;

assign one_flag = (one_en&&(cnt4 <= t_560us))?:;

//----------------------------------------------//

//结束码, 560us载波

reg [:] cnt5;

wire finish_flag;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt5 <= ;

end

else if(finish_en)

begin

if(cnt5 >= t_560us) cnt5 <= t_560us+;

else cnt5 <= cnt5 + ;

end

else cnt5 <= ;

end

assign finish_over = (cnt5 == t_560us)?:;

assign finish_flag = (finish_en&&(cnt5 <= t_560us))?:;

//-----------------------------------//

wire ir_out;

assign ir_out = start_flag||zero_flag||one_flag||finish_flag;

assign IR_out = ir_out&&clk_38k;

assign led_3 = i[];

assign led_4 = i[];

endmodule

接收程序:

/********************************Copyright**************************************

**----------------------------File information--------------------------

** File name :ir_resive.v

** CreateDate :2015.06

** Funtions : 中断接收程序。结束数据为:引导码+用户码+用户反码+数据码+数据反码。

** Operate on :M5C06N3L114C7

** Copyright :All rights reserved.

** Version :V1.0

**---------------------------Modify the file information----------------

** Modified by :

** Modified data :

** Modify Content:

*******************************************************************************/

module IR_resive (

clk,

rst_n,

ir_in,

led_error,

led_5,

led_6,

led_7,

test_data

);

input clk;

input rst_n;

input ir_in;

output led_error;

output led_5;

output led_6;

output led_7;

output [:] test_data;

//---------------------------------------------//

reg [:] ir_in_reg;

wire ir_in_pos;

wire ir_in_neg;

wire ir_in_change;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

ir_in_reg <= 'b111;

end

else

begin

ir_in_reg <= {ir_in_reg[:],ir_in};

end

end

assign ir_in_pos = (ir_in_reg[:] == 'b01)?1:0;

assign ir_in_neg = (ir_in_reg[:] == 'b10)?1:0;

assign ir_in_change = ir_in_pos|ir_in_neg;

//------------------------------------//

//设计分频和计数部分:从1838T的 技术手册中,可以得出最小的脉冲持续时间为500us,在采样时可以对最小的电平采样16次,即对500us采样16次,

//则每次的采样间隔时间是 500us/16=31.25us 时钟频率为FCLK = X MHZ, 则最小采样计数为:N =31.25*X,

//然后再用一个计数器计数同一电平的采样计数时间。

//最后判断是leader的9ms 还是4.5ms,或是数据的 0 还是 1。

//--------------------------------------------------------//

`define FCLK_20M

// `define FCLK_24M `

`ifdef FCLK_20M

parameter t_31_25us = 'd625;

parameter t_100k = ;

`endif

`ifdef FCLK_24M

parameter t_31_25us = 'd750; //

parameter t_100k = ;

`endif

`ifdef FCLK_50M

parameter t_31_25us = 'd1562; //

parameter t_100k = ;

`endif

parameter t_low_H = ;

parameter t_low_L = ; //16

parameter t_high_H=; //54 1.7MS左右

parameter t_high_L= ;

parameter t_9ms_H ='d398; //288

parameter t_9ms_L ='d278;

parameter t_4_5ms_H ='d154; //144

parameter t_4_5ms_L ='d134;

parameter t_watch = 'd500; //定时,计数达到500,则已经跑飞,

parameter t_1s = 'd31999;

//---------------------------------------------//

reg idel_flag;

reg [:] cnt;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt <= ;

end

else if(idel_flag) cnt <= ; //空闲状态,不再变化

else if(ir_in_change) cnt <= ;

else if(cnt == t_31_25us) cnt <= ;

else cnt<= cnt + ;

end

reg [:] cnt1;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt1 <= ;

end

else if(idel_flag) cnt1 <= ;

else if(ir_in_change) cnt1 <= ;

else if(cnt == t_31_25us) cnt1 <= cnt1 + ;

else cnt1 <= cnt1;

end

wire t_9ms_flag;

wire t_4_5_ms_flag;

wire short_flag; //短电平,可是高电平也可以是低电平

wire long_flag; //长电平,肯定是高电平

assign t_9ms_flag = ((cnt1 > t_9ms_L)&&(cnt1 < t_9ms_H));

assign t_4_5_ms_flag = ((cnt1 > t_4_5ms_L)&&(cnt1 < t_4_5ms_H));

assign long_flag = ((cnt1 > t_high_L)&&(cnt1 < t_high_H));

assign short_flag = ((cnt1 > t_low_L)&&(cnt1 < t_low_H));

wire watchdog;

assign watchdog = (cnt1 > t_watch)?:;

//---------------------------------------------//

parameter IDEL = 'd0;

parameter L_9MS = 'd1;

parameter L_4_5MS = 'd2;

parameter DATA_R = 'd4;

parameter FINISH_R= 'd8;

reg [:] state;

reg [:] shiftdata;

reg [:] n;

reg error_flag;

reg r_over;

reg [:] rdata;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

state <= IDEL;

shiftdata <= ;

n <= ;

error_flag <= ;

rdata <= ;

r_over<= ;

idel_flag <= ;

// led_5 <= 1;

// led_6 <= 1;

end

// else if(watchdog) state <= IDEL;

else

begin

case(state)

IDEL:

begin

idel_flag <= ; //空闲状态

shiftdata <= ;

n <= ;

error_flag <= ;

r_over<= ;

if(ir_in_reg[] ==)

begin

state <= L_9MS; //检测到拉低数据线

idel_flag <= ;

end

else state <= IDEL;

end

L_9MS: //9ms为低电平,数据线拉高时结束

begin

// led_5 <= 0;

if(watchdog) state <= IDEL;

else if(ir_in_pos)

begin

if(t_9ms_flag) state <= L_4_5MS;

else

begin

state <= IDEL;

error_flag <= ;

end

end

else state <= L_9MS;

end

L_4_5MS:

begin

if(watchdog) state <= IDEL;

else if(ir_in_neg)

begin

if(t_4_5_ms_flag) state <= DATA_R;

else

begin

state <= IDEL;

error_flag <= ;

end

end

else state <= L_4_5MS;

end

DATA_R:

begin

// led_6 <= 0;

if(watchdog) state <= IDEL;

else if((n == )&&(ir_in_reg[:] == 'b11)) state <= FINISH_R;

else if(ir_in_pos)

begin

if(short_flag) state <= DATA_R;

else

begin

state <= IDEL;

error_flag <= ;

end

end

else if(ir_in_neg)

begin

n<= n + ;

if(short_flag) shiftdata[n] <= ; //从低位到高位依次接收,这样数据的位置是 相反的

else if(long_flag) shiftdata[n] <= ; //从原来的{用户码,用户反码,数据,数据反码}变为{数据反码,数据,用户反码,用户码}

else //所以要调整数据位置

begin

state <= IDEL;

error_flag <= ;

end

end

else state <= DATA_R;

end

FINISH_R:

begin

r_over <= ;

rdata <= {shiftdata[:],shiftdata[:],shiftdata[:],shiftdata[:]}; //调整位置

state <= IDEL;

end

default:state <= IDEL;

endcase

end

end

//---------------------------------------------//

assign led_5 = (rdata[:] == 'h01)?0:1;

assign led_6 = (rdata[:] == 'h02)?0:1;

assign led_7 = (rdata[:] == 'h00)?0:1;

assign test_data = rdata[:];

// assign test_data = {error_flag,t_4_5_ms_flag,ir_in_change,ir_in_reg[1],state[3:0]};

endmodule

按键消抖(与以前有修改):

/********************************Copyright**************************************

**----------------------------File information--------------------------

** File name :key_shake.v

** CreateDate :2015.03

** Funtions : 按键的消抖操作:在复位之后的100us内,不响应按键的操作,在之后有按键按下后,有20ms的延迟,之后输出按键输出.

** Operate on :M5C06N3L114C7

** Copyright :All rights reserved[F].

** Version :V1.0

**---------------------------Modify the file information----------------

** Modified by :

** Modified data : 2015.04 2015.06

** Modify Content:V1.1:clk-->clk_100M, 常数声明放到一起,便于修改。 增加实用20Mclk,并将输出修改为连续高电平

*******************************************************************************/ module key_shake (

clk_100M,

rst_n, key_in,

key_out

);

input clk_100M; //100Mhz

input rst_n; input key_in;

output key_out; //-------------------------------------- //在复位之后的100us内,不响应按键的操作 // `define CLK_100M

`define CLK_20M `ifdef CLK_100M

parameter t_100us = 'd9999;

parameter t1ms = 'd99999; //定时1ms

parameter t_20ms = 'd20;

`endif `ifdef CLK_20M

parameter t_100us = 'd1999;

parameter t1ms = 'd19999; //定时1ms

parameter t_20ms = 'd20;

`endif reg [:] cnt;

reg key_en; //复位之后允许按键输入标志

always @(posedge clk_100M or negedge rst_n)

begin

if(!rst_n)

begin

cnt <= ;

key_en <=;

end

else

begin

if(cnt == t_100us)

begin

key_en <= ;

end

else

begin

key_en <= ;

cnt <= cnt + ;

end

end

end //--------------------------------------------------

wire HtoL_flag; //下降沿标志

wire LtoH_flag; //上升沿标志

reg [:] key_reg;

always @(posedge clk_100M or negedge rst_n)

begin

if(!rst_n)

begin

key_reg <= 'b111; //默认没按下状态为高,按下之后为低.反之则为3'b000;

end

else

begin

key_reg <= {key_reg[:],key_in};

end

end assign HtoL_flag = key_en?(key_reg[:] == 'b10):0; //下降沿检测,一个时钟的高电平

assign LtoH_flag = key_en?(key_reg[:] == 'b01):0; //上升沿检测,一个时钟的高电平

//---------------------------------------------

reg cnt_en; //计数使能标志 reg [:] cnt2;

always @(posedge clk_100M or negedge rst_n)

begin

if(!rst_n)

begin

cnt2 <= 'd0;

end

else if((cnt_en)&&(cnt2 == t1ms))

begin

cnt2 <= 'd0;

end

else if(cnt_en)

begin

cnt2 <= cnt2 + 'd1;

end

else

cnt2 <= 'd0;

end reg [:] cnt3;

always @(posedge clk_100M or negedge rst_n)

begin

if(!rst_n)

begin

cnt3 <= 'd0;

end

else if((cnt_en)&&(cnt2 == t1ms))

begin

if(cnt3 == t_20ms )

cnt3 <= t_20ms;

else

cnt3 <= cnt3 + ;

end

else if(!cnt_en)

cnt3 <= 'd0;

end //----------------------------------

//按键状态机

reg [:] i;

reg key_down; //按键按下标志

reg key_up; //按键释放标志

always @(posedge clk_100M or negedge rst_n)

begin

if(!rst_n)

begin

key_down <= ;

key_up <= ;

i <= ;

cnt_en <= ;

end

else

begin

case(i)

'd0:

begin

key_down <= ;

key_up <= ;

if(HtoL_flag) i <= 'd1; //检测到按下

else if(LtoH_flag) i <= 'd2; //检测到释放按键

else i <= 'd0;

end

'd1:

begin

if(cnt3 == t_20ms )

begin

if(!key_in) //检测到按键依然被按下

begin

key_down <= ; //按键按下成功

i <= 'd3;

cnt_en <= ;

end

else

begin

key_down <= ;

i <= 'd0;

cnt_en <= ;

end

end

else

cnt_en <= ;

end

'd2:

begin

if(cnt3 == t_20ms )

begin

if(key_in) //检测到按键被释放

begin

key_up <= ; //按键释放成功

i <= 'd4;

cnt_en <= ;

end

else

begin

key_up <= ;

i <= 'd0;

cnt_en <= ;

end

end

else

cnt_en <= ;

end

'd3:

begin

if(key_in)

begin

key_down <= ;

i <= 'd0;

end

else

i <= 'd3;

end

'd4:

begin

if(!key_in)

begin

key_up <= ;

i <= 'd0;

end

else

i <= 'd4;

end

default:i <= 'd0;

endcase

end

end assign key_out = key_down; //当按键被按下有效时

// assign key_out = key_up; //当按键被释放后才有效时

endmodule

将两个程序合在一起的顶层文件:

/********************************Copyright**************************************

**----------------------------File information--------------------------

** File name :IR_TOP.v

** CreateDate :2015.06

** Funtions : 中断的顶层文件

** Operate on :M5C06N3F256C7

** Copyright :All rights reserved.

** Version :V1.0

**---------------------------Modify the file information----------------

** Modified by :

** Modified data :

** Modify Content:

*******************************************************************************/

module IR_TOP (

clk,

rst_n,

ir_in,

ir_out,

key_1,

key_2,

led_d1,

led_d2,

led_d3,

led_d4,

led_d5,

led_d6,

led_d7,

led_d8,

test_data

);

input clk;

input rst_n;

input key_1;

input key_2;

input ir_in;

output ir_out;

output led_d1;

output led_d2;

output led_d3;

output led_d4;

output led_d5;

output led_d6;

output led_d7;

output led_d8;

output [:] test_data;

//---------------------------------------------//

wire key_1_flag;

wire key_2_flag;

key_shake U1(

.clk_100M(clk),

.rst_n(rst_n),

.key_in(key_1),

.key_out(key_1_flag)

);

key_shake U2(

.clk_100M(clk),

.rst_n(rst_n),

.key_in(key_2),

.key_out(key_2_flag)

);

wire [:] data_t;

IR_send u1(

.clk(clk),

.rst_n(rst_n),

.key_1(key_1_flag),

.key_2(key_2_flag),

.IR_out(ir_out),

.led_1(led_d1),

.led_2(led_d2),

.led_3(led_d3),

.led_4(led_d4)

);

IR_resive u2(

.clk(clk),

.rst_n(rst_n),

.ir_in(ir_in),

.led_error(led_d8),

.led_5(led_d5),

.led_6(led_d6),

.led_7(led_d7),

.test_data(data_t)

);

//---------------------------------------------//

assign test_data = data_t;

endmodule

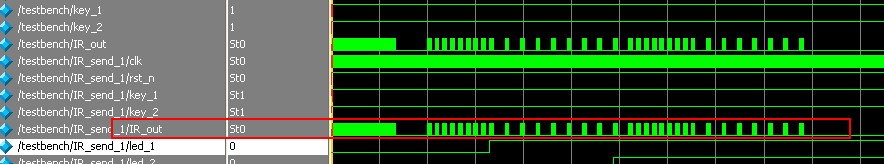

仿真图:

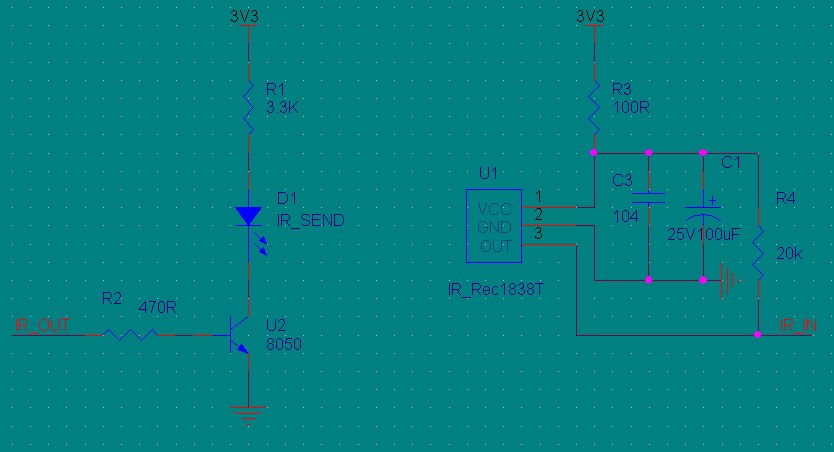

接收仿真图:

发送仿真图:

红外解码编码学习----verilog的更多相关文章

- MicroPython TPYBoard v102 无线红外遥控舵机(基于红外解/编码模块)

转载请注明文章来源,更多教程可自助参考docs.tpyboard.com,QQ技术交流群:157816561,公众号:MicroPython玩家汇 红外解码/编码模块介绍 模块上搭载了红外接收头.红外 ...

- python --- 字符编码学习小结(二)

距离上一篇的python --- 字符编码学习小结(一)已经过去2年了,2年的时间里,确实也遇到了各种各样的字符编码问题,也能解决,但是每次都是把所有的方法都试一遍,然后终于正常.这种方法显然是不科学 ...

- 关于音频总线IIS的学习---Verilog

关于音频总线IIS的学习---Verilog 主要思想: 在分析寄存器的值变化的时候,将时钟的边沿分两边来看,边沿之前,边沿之后,在always 块语句里面用来分析判断的寄存器的值,都应该用边沿变化之 ...

- FFmpeg软件只是个解码编码软件,如果支持多种格式必须先安装好对应的库,下面就说下我装的库

FFmpeg软件只是个解码编码软件,如果支持多种格式必须先安装好对应的库,下面就说下我装的库:1. 安装faad2 # wget http://downloads.sourceforge.net/fa ...

- python --- 字符编码学习小结

上半年的KPI,是用python做一个测试桩系统,现在系统框架基本也差不多定下来了.里面有用到新学的工厂设计模式以及以及常用的大牛写框架的业务逻辑和python小技巧.发现之前自己写的代码还是面向过程 ...

- .NET:字符集和编码学习总结

背景 一直没有深入的学习字符集和编码的知识(现在也没有深入),今天查阅了一些资料,弄明白了一些事情,本文就简单记录一下. 字符集和编码 字符集是指一些符号组成的集合,编码是对指定字符集如何表示为字节的 ...

- 红外 NEC编码

它是一种电磁波,可以实现数据的无线传输 它的波长范围为760nm ~ 1mm,不为人眼所见 紫外光波长为10-400nm 红外与蓝牙 红外:对准.直接.0-10米,单对单 蓝牙:10米左右,加强信号后 ...

- JS编码,解码. asp.net(C#)对应解码,编码

escape不编码字符有69个:*,+,-,.,/,@,_,0-9,a-z,A-Z encodeURI不编码字符有82个:!,#,$,&,',(,),*,+,,,-,.,/,:,;,=,?,@ ...

- 关于URL 解码, 编码

由于近期客户需要用到CA认证,此CA认证采用的是URL方式出传值 使用指定的编码对象将 URL 编码的字符串转换为已解码的字符串. 编码个人理解就是将某字符串以某种方式储存起来,而解码则以其编码格式得 ...

随机推荐

- 【转载】javaAgent 参数

-javaagent 这个JVM参数是JDK 5引进的. java -help的帮助里面写道: -javaagent:<jarpath>[=<options>] load Ja ...

- Xcode 7 App Transport Security has blocked a cleartext HTTP 报错解决办法

Xcode 7 创建新项目用到 UIWebView 发送请求时,报下面的错: “App Transport Security has blocked a cleartext HTTP (http:// ...

- iOS开发——UI进阶篇(一)UITableView,索引条,汽车数据展示案例

一.什么是UITableView 在iOS中,要实现展示列表数据,最常用的做法就是使用UITableViewUITableView继承自UIScrollView,因此支持垂直滚动,而且性能极佳 UIT ...

- 爆料喽!!!开源日志库Logger的剖析分析

导读 Logger类提供了多种方法来处理日志活动.上一篇介绍了开源日志库Logger的使用,今天我主要来分析Logger实现的原理. 库的整体架构图 详细剖析 我们从使用的角度来对Logger库抽茧剥 ...

- C++ 零碎知识点

C++的一些知识点比较零碎,下面清单的形式做一些记录与归纳,以供参考. 1.赋值操作符重载(深复制): (1)由于目标对象可能引用了以前的一些数据,所以应该先delete这些数据: (2)注意到对象可 ...

- Android使用Unity导致Activity被销毁的解决办法

由于需要在Android中使用Unity(Android的Activity会继承Unity提供的UnityPlayerActivity),可能是第三方的原因退出Unity后就导致Android整个应用 ...

- Exploiting the Circulant Structure of Tracking-by-Detection with Kernels(二)

之前给导师汇报时,主要是论文涉及公式的一些推导

- mysql 主从数据库设置方法

1.主从数据库都需开启bin-log日志 2.在my.ini(windows)或my.cnf(linux)配置文件中添加 server-id = 1(主从配置 id 必须不同) 例子: [mysqld ...

- C# 接口基础

接口只包含方法.属性.事件或索引器的签名. 实现接口的类或结构必须实现接口定义中指定的接口成员 接口中可以包含字段吗? 第一次被问到这个问题的时候被问愣住了,只能回答:印象当中没见过在接口中定义变量 ...

- MMO可见格子算法

看注释吧,写的很清楚了 using System; using System.Collections.Generic; using System.Diagnostics; using System.L ...